Allegro基本操作——PCB布线

转:http://blog.sina.com.cn/s/blog_1538bc9470102vyyq.html

http://www.elecfans.com/article/80/110/2010/20100628219744.html

http://renguangling.blog.163.com/blog/static/4300262420120182517284/

https://wenku.baidu.com/view/3e14f7600b1c59eef8c7b439.html

http://www.doc88.com/p-780750159175.html

https://wenku.baidu.com/view/39eb2d84581b6bd97f19ea8a.html

DDR信号完整性仿真介绍(二)【转发】

2018-04-10 by:CAE仿真在线 来源:互联网

上篇文章我们对DDR做了一些基本的介绍,了解了DDR信号分组以及各组信号之间的长度匹配关系。那么,一般什么情况我们需要仿真分析呢?作者认为,多数情况下是我们的设计人员对这一块的把握不大的时候,因为DDR信号Net多,走线密度大,速率较高,DDR信号质量直接关系到整块板子的设计成败。

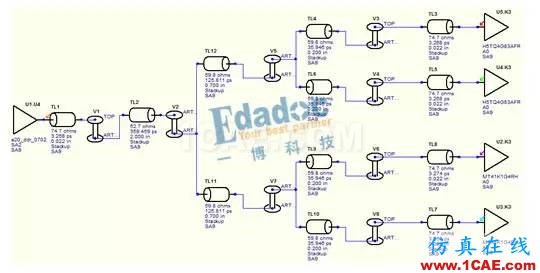

闲话不多说,本期将通过几个案例让初学者对DDR仿真有一个初步的认识。DDR信号仿真分为信号质量分析与时序分析,两者的侧重点不一样。下面来看看,某设计人员DDR3布线绕完等长之后,让我们仿真,拓扑结构如图1所示:

图 1

从拓扑结构来看,该设计是一个主控拖动四片DDR颗粒,采用T型结构。该设计分支等长做的都很好,貌似没什么问题,但是仿真出来的波形却是图2这样的:

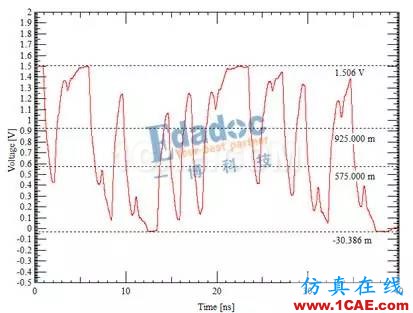

图 2

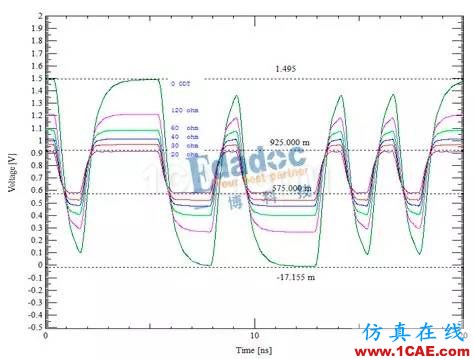

该波形电压虽然都通过了门限电平,但是裕量很小,波形也是参差不齐,显然不够理想。我们这里仅仅仿真了单根信号的质量,如果把串扰也考虑进来,波形就很难保证不出问题。作者以前也仿真过这种拓扑结构,但是波形没有这么糟糕啊。为了验证一下,作者把驱动芯片的IBIS换了,拓扑结构保持不变,结果得到的波形是这样的,如图3:

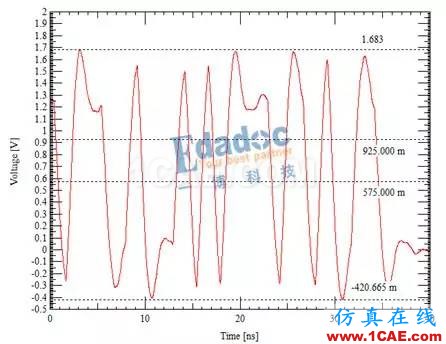

图3

图3信号质量与图2比起来要好一些,但结果不理想,过冲还是很大。其实这里,作者使用不同的IBIS模型,就是为了证明不同主控芯片输出的波形是不一样的。有时我们的Layout人员会有这样一个疑问,改版的时候仅仅只是换了一块主控芯片而已,PCB本身的布局没有改版,甚至芯片管脚对应的连接关系都没变,板子上的布线完全不用再改动了,这种想法是不对的,同一块板子,拓扑结构保持不变的情况,更换主控芯片,信号的质量也会受到影响的,这时我们的拓扑结构必须重新评估。

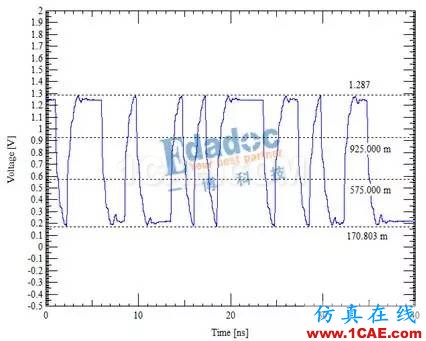

好了,造成图2与图3信号质量不好的原因是什么呢?经验丰富的网友们也许发现了,上面的T型结构没有做端接处理。同样,作者也发现了这个问题,结果加上端接电阻后,信号质量得到了改善,如图4所示:

图4

再来看一个DDR3设计案例,某设计人员在数据信号中加入了串阻,拓扑结构如下图5:

图5

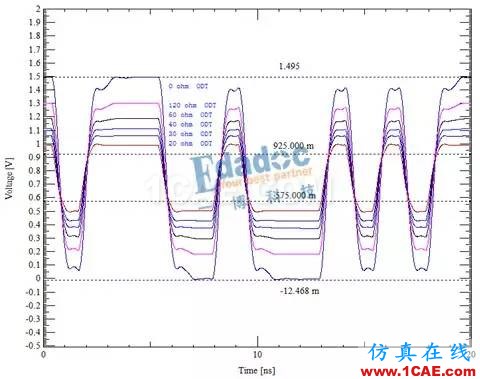

DDR3颗粒端有ODT功能,且有6种阻值可选,作者扫面这几种模式得到的波形如图6:

图6

图6的波形,在开ODT的情况下波形裕量较小,DDR3本身带有ODT功能啊,为什么还要加串阻呢?于是我果断把串阻去掉,仿真波形如图7

图7

去掉串阻之后,波形的裕量更大了,且上升沿没那么缓了。所以,对于有ODT功能的DDR颗粒,布线时不用加串阻,这样不仅节省了元件,也节省了布线空间。

看来SI工程师是十分重要的哈,高速设计的成功离不开SI工程师的努力。拓扑结构的设计不是一劳永逸的,什么驱动芯片适合什么样的拓扑结构,需要仿真评估。仿真是一个不断尝试与探索的过程,它帮助我们找到互连与器件的最佳匹配。

问题来了

ODT阻值选择与接收端电压幅值呈什么关系,为什么?

Allegro基本操作——PCB布线的更多相关文章

- PCB 布线,直角线,差分线,蛇形线

1.直角线 直角走线的一般标准是PCB布线中要尽量避免的情况,也几乎成为衡量布线好坏的标准之一. 直角走线对信号的影响主要体系那在下面三个方面 1.保教可以等效为传输线是哪个的容性负载,减缓上升时间. ...

- PCB布线经验

查看: 3645|回复: 11 [经验] PCB设计经验(1)——布局基本要领 [复制链接] ohahaha 927 TA的帖子 0 TA的资源 纯净的硅(中级) 发消息 加好友 电 ...

- Altera公司高速PCB布线指南

来至Altera公司的高速PCB布线指南,该文档言简意赅,深入浅出,对于日常高速PCB布局布线中经常碰到的一些问题进行了解析.例如:板材的选择,介电常数及损耗因子对高速高频线路的影响,传输线,阻抗控制 ...

- 0R电阻在PCB布线中对布线畅通的一个小妙用

在PCB布线中,我们都会尽量节约板子空间,将元器件排布的紧密一些,难免会遇到布线不通的时候. 博主下面就来说一个关于0R电阻在PCB布线使之畅通的一个小妙用. 使用0R电阻前 假设我们这个TXD的线周 ...

- PCB Layout设计规范——PCB布线与布局

1.PCB布线与布局隔离准则:强弱电流隔离.大小电压隔离,高低频率隔离.输入输出隔离,分界标准为相差一个数量级.隔离方法包括:空间远离.地线隔开. 2. 晶振要尽量靠近IC,且布线要较粗 ...

- PCB布线设计-模拟和数字布线的异同(转)

工程领域中的数字设计人员和数字电路板设计专家在不断增加,这反映了行业的发展趋势.尽管对数字设计的重视带来了电子产品的重大发展,但仍然存在,而且还会一直存在一部分与模拟或现实环境接口的电路设计.模拟和数 ...

- Altium Designer PCB文件的绘制(下:PCB布线和检查)

在完成电路板的布局工作后,就可以开始布线操作了.在PCB的设计中,布线是完成产品设计的最重要的步骤,其要求最高.技术最细.工作量最大.PCB布线可分为单面布线.双面布线.多层布线.布线的方式有自动布线 ...

- PCB布线总的原则

转自张飞实战电子公众号 PCB布线总的原则 最短路径和减少干扰 PCB布线的总的流程大致如下: 1了解制造厂商的制造规范-线宽,线间距,过孔要求及层数要求: 2确定层数并定义各层的功能: 3设计布线规 ...

- 关于PCB布线的顺序到底是怎样才合理?

有人说先布好电源线和地线,让它们尽量靠近走,然后再考虑信号线:也有人说先布好关键的信号线,然后再走电源和地线:还有人说先布好电源线,再布信号线,地线最后布.到底怎么样才算好呢?或者说,一般应按照什么顺 ...

随机推荐

- C# TypeDescriptor获取类型转换器,实现泛型转换

需求背景 平时的coding过程中,经常性遇到string类型转换成其他的基本类型,如 int double bool等,那我们正常的方式就是下面的方式进行类型转换 int.Parse("1 ...

- ubuntu14.04修改mysql默认编码

修改文件为/etc/mysql/my.cnf [client] default-character-set = utf8 (ps:client的设置没变) [mysqld] lower_case_ta ...

- JSON树节点的增删查改

最近了解到使用json字符串存到数据库的一种存储方式,取出来的json字符串可以进行相应的节点操作 故借此机会练习下递归,完成对json节点操作对应的工具类. 介绍一下我使用的依赖 复制代码 < ...

- LibreOJ2095 - 「CQOI2015」选数

Portal Description 给出\(n,k,L,R(\leq10^9)\),求从\([L,R]\)中选出\(n\)个可相同有顺序的数使得其gcd为\(k\)的方案数. Solution 记\ ...

- testng依赖

Testng提供了两种依赖实现 1.强制依赖:某个测试用例之前需要执行的依赖链中如果有一个失败,那么接下来所有的测试都不会被执行 2.顺序依赖(软依赖):顺序依赖的用处更多是用来检测一个测试链是否按照 ...

- hdu 1087 最大上升子序列的和(dp或线段树)

Super Jumping! Jumping! Jumping! Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 ...

- JQuery Option 排序

<script type="text/javascript"> $(document).ready(function () { $("select" ...

- 【CF1017B】The Bits(模拟)

题意:给定两个二进制数字a,b,可以任意交换a中的两个bit位,求进行这样一次操作,最多可产生多少种不同的a or b n<=1e5 思路:模拟,分类讨论 #include<cstdio& ...

- 超级钢琴 BZOJ 2006

超级钢琴 [问题描述] 小Z是一个小有名气的钢琴家,最近C博士送给了小Z一架超级钢琴,小Z希望能够用这架钢琴创作出世界上最美妙的音乐. 这架超级钢琴可以弹奏出n个音符,编号为1至n.第i个音符的美妙度 ...

- 以iphone6plus 为标准单位是px的页面 在运行时转换为rem

在页面中引入以下代码,把样式中带px单位的样式放到本页面中的<style>标签中 /** * Created by Administrator on 2017-03-14. */ /*** ...