关于过两级mux的时序约束的添加(一个非常经典的时序约束问题)

非常开心自己的微信公众号:

《数字集成电路设计及EDA教程》

关注者超过了1700

里面主要讲解数字IC前端、后端、DFT、低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程。

为了纪念,同时考虑到微信公众平台上面发布的很多推文百度搜索不到,所以以后的推文也会在这里进行转载。

一文、一曲、一图

文:

《童话里的生日祝福》

微风躲在霞草里舞蹈

提醒我你的生日快到

玫瑰刺拽着衬衫衣角

你的礼物我怎么会忘掉

绵云像麦芽糖被阳光发酵

是你也想了解的味道

我站在山坡上踮起脚

只有这个角度刚刚好

想象里摘一朵送给你要不要

下过雨的天怎么更吸引小鸟

关于这个问题我一直在思考

原来是涂了彩虹颜色的唇膏

于是我悄悄偷一点放在你的化装盒

想你也一定喜欢得不得了

庄园里刚结出的花苞

九百九十九朵不多也不少

让我用勤劳培育给你的祈祷

瞧

那一株花蕊轻盈像你的睫毛

那一朵欲放未放是你羞涩而温暖的笑

风车缓缓地绕陪着牛儿吃草

夕阳懒懒地照在等黎明破晓

你倔起嘴巴在撒娇

又溜走一岁这时光飞逝的年少

风筝飞呀飞系着愿望在飘

秋千摇呀摇我累得快睡着

想起这首旋律古老的歌谣

化身田园诗人为你唱:

祝你生日快乐

祝你生日快乐

祝你生日快乐

祝你生日快乐

曲:

暂时不知道怎么弄

图:

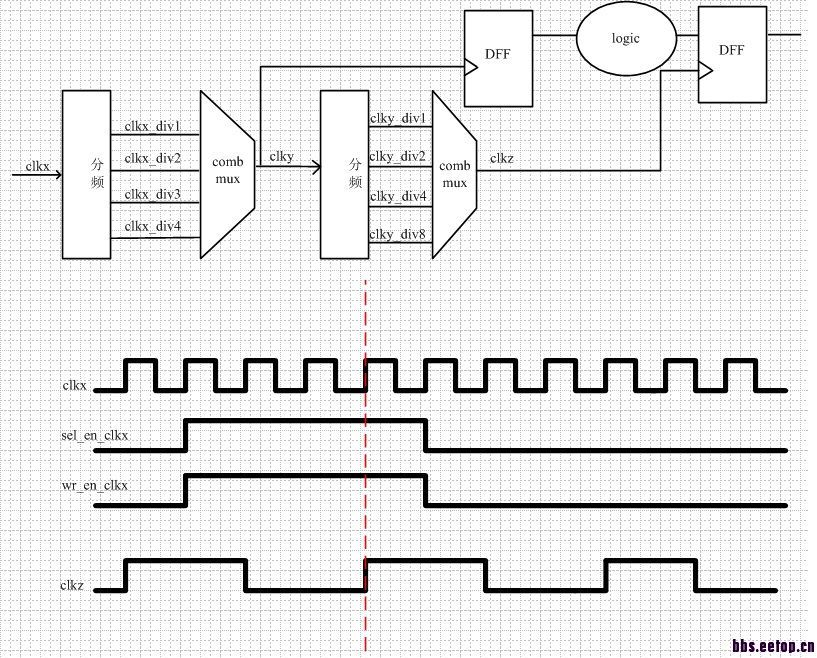

时序约束是逻辑综合以及布局布线中一个非常重要的环节,如果设计中时钟非常多,那么时序约束将非常复杂,下面给出一个经典案例来给出多时钟且时钟经过两级MUX的时序约束问题的最佳解决方案。

关于过两级mux的时序约束的添加

参考链接:http://bbs.eetop.cn/thread-458928-1-1.html

如上图,分频器都是寄存器做的,mux是用组合逻辑实现的,时序图列出了clkx与clkz之间4分频时的数据采集关系。

问:本电路完整的时序约束SDC文件,尤其是clkx和clkz之间应该如何约束?

答:

set_app_var timing_enable_multiple_clocks_per_reg true

create_generated_clock -divide_by 1 -name clkx_div1 -source [get_ports clkx] [get_pins freq_divA/clkx_div1]

create_generated_clock -divide_by 2 -name clkx_div2 -source [get_ports clkx] [get_pins freq_divA/clkx_div2]

create_generated_clock -divide_by 3 -name clkx_div3 -source [get_ports clkx] [get_pins freq_divA/clkx_div3]

create_generated_clock -divide_by 4 -name clkx_div4 -source [get_ports clkx] [get_pins freq_divA/clkx_div4]

set_clock_group -logically_exclusive -group clkx_div1 -group clkx_div2 -group clkx_div3 -group clkx_div4

create_generated_clock -divide_by 1 -name clky_1 -source [get_pins freq_divA/clkx_div1] [get_pins MUX1/clky]

create_generated_clock -divide_by 1 -name clky_2 -source [get_pins freq_divA/clkx_div2] [get_pins MUX1/clky] -add

create_generated_clock -divide_by 1 -name clky_3 -source [get_pins freq_divA/clkx_div3] [get_pins MUX1/clky] -add

create_generated_clock -divide_by 1 -name clky_4 -source [get_pins freq_divA/clkx_div4] [get_pins MUX1/clky] -add

set_clock_group -physically_exclusive -group clky_1 -group clky_2 -group clky_3 -group clky_4

create_generated_clock -divide_by 1 -name clky_div1 -source [get_pins MUX1/clky] [get_pins freq_divB/clky_div1]

create_generated_clock -divide_by 2 -name clky_div2 -source [get_pins MUX1/clky] [get_pins freq_divB/clky_div2]

create_generated_clock -divide_by 4 -name clky_div4 -source [get_pins MUX1/clky] [get_pins freq_divB/clky_div4]

create_generated_clock -divide_by 8 -name clky_div8 -source [get_pins MUX1/clky] [get_pins freq_divB/clky_div8]

set_clock_group -logically_exclusive -group clky_div1 -group clky_div2 -group clky_div4 -group clky_div8

create_generated_clock -divide_by 1 -name clkz_1 -source [get_pins freq_divB/clky_div1] [get_pins MUX2/clkz]

create_generated_clock -divide_by 1 -name clkz_2 -source [get_pins freq_divB/clky_div2] [get_pins MUX2/clkz] -add

create_generated_clock -divide_by 1 -name clkz_4 -source [get_pins freq_divB/clky_div4] [get_pins MUX2/clkz] -add

create_generated_clock -divide_by 1 -name clkz_8 -source [get_pins freq_divB/clky_div8] [get_pins MUX2/clkz] -add

set_clock_group -physically_exclusive -group clkz_1 -group clkz_2 -group clkz_4 -group clkz_8

之后再继续设定各个generated clokc的uncertainty、network latency和transition:set_clock_transition和set_clock_uncertainty

以及set_clock_latency -network 。。。,需要写的命令是多一些。但还是比用set_false_path命令好,DC会分析4*4=16条时序路径,

因此你需要些32句set_false_path命令,而用set_clock_group,只需要4句命令。

由你的图中,可知clkx_div?四个生成时钟是逻辑上互斥的,物理上不互斥,这样就不会分析它们之间的时序关系,但会分析它们之间的信号

完整性(PT SI),而引脚clky之后作用在launchregister的时钟之间既是逻辑互斥也是物理互斥。同样可以分析第二个分频器和mux的原理。

当然也可以采用如下写法:

create_generated_clock -divide_by 1 -name clky_1 -source [get_ports clkx] [get_pins MUX1/clky]

create_generated_clock -divide_by 2 -name clky_2 -source [get_ports clkx] [get_pins MUX1/clky] -add

create_generated_clock -divide_by 3 -name clky_3 -source [get_ports clkx] [get_pins MUX1/clky] -add

create_generated_clock -divide_by 4 -name clky_4 -source [get_ports clkx] [get_pins MUX1/clky] -add

set_clock_group -physically_exclusive -group clky_1 -group clky_2 -group clky_3 -group clky_4

create_generated_clock -divide_by 1 -name clkz_1 -source [get_pins MUX1/clky] [get_pins MUX2/clkz]

create_generated_clock -divide_by 2 -name clkz_2 -source [get_pins MUX1/clky] [get_pins MUX2/clkz] -add

create_generated_clock -divide_by 4 -name clkz_4 -source [get_pins MUX1/clky] [get_pins MUX2/clkz] -add

create_generated_clock -divide_by 8 -name clkz_8 -source [get_pins MUX1/clky] [get_pins MUX2/clkz] -add

set_clock_group -physically_exclusive -group clkz_1 -group clkz_2 -group clkz_4 -group clkz_8

同样设置各个generated clokc的network latency、uncertainty和transition。

问:那DC还会分析clkx 和 clky_div1/clky_div2/clky_div4/clky_div8 之间,以及clkx_div? 与clky_div? 之间的时序关系吗?

答:用set_clock_groups -logicall_exclusive 很方便,只要你不设false path(包括case analaysis,clock groups),dc都会分析

注:物理互斥表示两个时钟不会同时存在,最好用于一个引脚上可能输入几种不同的时钟频率。逻辑互斥表示两个时钟可以同时存在,但最终只有一个时钟有效,一般用于MUX的输出时钟。

如果喜欢也请多多分享哟,谢谢您的关注![]()

关于过两级mux的时序约束的添加(一个非常经典的时序约束问题)的更多相关文章

- vue项目两级全选(多级原理也一样),感觉有点意思,随手一记

需求: 首先说一下思路:我首先把数据列表两级遍历了一下,增加了一个checked属性来控制勾选和不勾线 this.productList.forEach((item)=>{ this.$set( ...

- 每天进步一点点------时序分析基础与时钟约束实例(四)IO口时序(Input Delay /output Delay)

1.1 概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛.因此,FPGA时序约束中IO口时序约束也是一个重点.只有约束正确 ...

- ipv4理论知识3-分类编址之两级编址

两级编制 分类编址时,同一网络中的所有地址都属于统一个地址块,而每个地址块包含两部分:网络标识和主机标识.网络标识指明了网络,主机标识则指明了连接到该网络的一台特定的主机.如下图描绘了分类编址中一个I ...

- Unity3D热更新全书-脚本(二) 两级分化

上篇明确了我们探讨的脚本是什么:是写在文本文件里面的代码,可以作为资源加载,取得字符串再执行. 可是为什么世界上会有那么多的脚本?而其使用方法完全看起来不一样呢?这是因为每种脚本都有自己的定位,在不同 ...

- [IOS 实现TabBar在Push后的隐藏 以及 两级Tabbar的切换]

翻了好多网页都没找到资料,自己试了下终于成功了,遂分享一下. 1.实现TabBar在Push后的隐藏 假如结构是这样 NavController->A->B,我们想要实现在A里有Tabba ...

- Android两级嵌套ListView滑动问题的解决

Android下面两级嵌套ListView会出现滑动失效,解决方案,把两级Listview全换成NoScrollListView,代码如下: public class NoScrollListView ...

- J2CACHE 两级缓存框架

概述 缓存框架我们有ehcache 和 redis 分别是 本地内存缓存和 分布式缓存框架.在实际情况下如果单台机器 使用ehcache 就可以满足需求了,速度快效率高,有些数据如果需要多台机器共享这 ...

- 实现外卖选餐时两级 tableView 联动效果

最近实现了下饿了么中选餐时两级tableView联动效果,先上效果图,大家感受一下: 下面说下具体实现步骤: 首先分解一下,实现这个需求主要是两点,一是点击左边tableView,同时滚动右边tabl ...

- Android 两级菜单栏

这里来记录下,android 的两级菜单栏,就是顶部切换,和底部的切换.因为在这个上面整了太久的时间,所以特此记录下. 第一种: 先介绍一个网上别人写出来的效果吧,这个当时积分真的很高..CSDN30 ...

随机推荐

- C#彩色艺术化二维码样式设计(仅说思路)

原文:C#彩色艺术化二维码样式设计(仅说思路) 仅讲思路,想要源码的请绕道. 一.样式 1.先看各种二维码的样式吧: (1)最简单的样式--黑白样式,如下图: 图1 最平常见到的二维码样式(如果 ...

- Nancy Web框架

原文 Nancy Web框架 Nancy框架 一.创建第一个Nancy应用 二.探索Nancy的module 1. 模块能够在全局被发现 2. 使用模块为路由创建一个根 三.定义路由 1. 方法 2. ...

- 八荣八耻 IT版

八荣八耻 IT版以可配置为荣,以硬编码为耻:以系统互备为荣,以系统单点为耻:以随时可重启为荣,以不能迁移为耻:以整体交付为荣,以部分交付为耻:以无状态为荣,以有状态为耻:以标准化为荣,以特殊化为耻:以 ...

- scala 学习

继续学习: https://segmentfault.com/a/1190000003068853#articleHeader2 https://docs.scala-lang.org/tour/mi ...

- Rails 最佳实践

在你业务简单的时候,让你简简单单用 ActiveRecord 模型. 复杂的时候,你可以用官方推荐的 Concerns. 更复杂的时候,可以通过 gem 和 API 来拆分. 极端复杂的时候,由于 R ...

- 把#define宏转换成指定格式

之前在弄一个东西的,有一大堆的宏,需要把它转换成其它的形式.遇到这种大批量的东西,我特别没有耐心去一个一个的弄,于是写了一段代码. 估计大家平常比较难用得上,不过可以平常相似的情况用来参考. Sort ...

- C#高性能大容量SOCKET并发(五):粘包、分包、解包

原文:C#高性能大容量SOCKET并发(五):粘包.分包.解包 粘包 使用TCP长连接就会引入粘包的问题,粘包是指发送方发送的若干包数据到接收方接收时粘成一包,从接收缓冲区看,后一包数据的头紧接着前一 ...

- UWP StorageFile StorageFolder StorageFileHelper

//获取表示指定文件系统路径中的文件夹的 StorageFolder. StorageFolder folder1 = await StorageFolder.GetFolderFromPathAsy ...

- jquery-ui sortable 使用实例

jquery-ui sortable 使用实例 最近公司需要做任务看板,需要拖拽效果.点击查看效果.由于网站是基于vue的技术栈,最开始找了一个现成的vue封装的拖拽组件:Vue.Draggable, ...

- FreeCL

FreeCL 1.03(Free Control Library)是一个开源且免费的Windows控件库,它属于3D图形引擎FreeGE中的一部分,用户可以自由地用于个人或商业开发.FreeCL使用类 ...