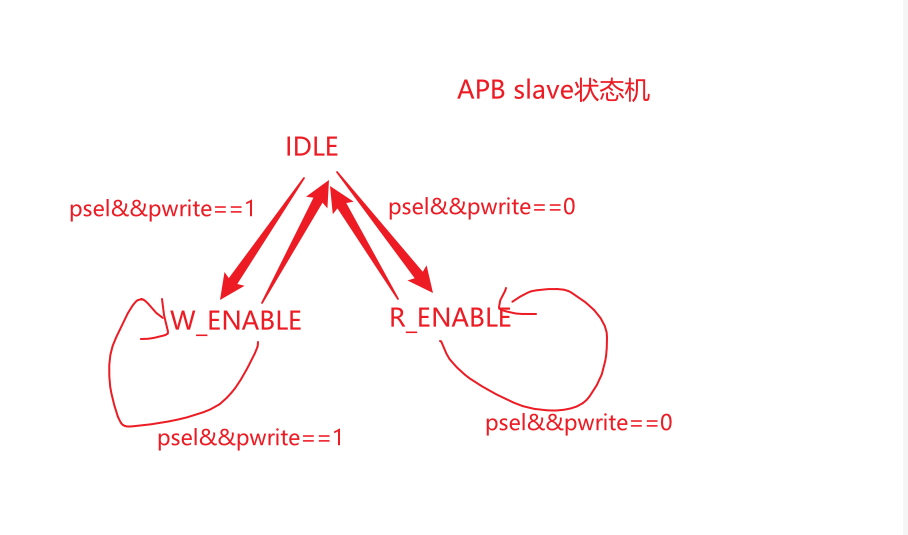

APB Slave状态机设计

`timescale 1ns/1ps

`define DATAWIDTH 32

`define ADDRWIDTH 8

`define IDLE 2'b00

`define W_ENABLE 2'b01

`define R_ENABLE 2'b10

module APB_Slave

(

input PCLK,

input PRESETn,

input [`ADDRWIDTH-1:0] PADDR,

input PWRITE,

input PSEL,

input [`DATAWIDTH-1:0] PWDATA,

output reg [`DATAWIDTH-1:0] PRDATA,

);

reg [`DATAWIDTH-1:0] RAM [0:2**`ADDRWIDTH -1];

reg [1:0] State;

always @(negedge PRESETn or posedge PCLK) begin

if (PRESETn == 0) begin

State <= `IDLE;

PRDATA <= 0;

end

else begin

case (State)

`IDLE : begin

PRDATA <= 0;

if (PSEL) begin

if (PWRITE) begin

State <= `W_ENABLE;

end

else begin

State <= `R_ENABLE;

end

end

end

`W_ENABLE : begin

if (PSEL && PWRITE) begin

RAM[PADDR] <= PWDATA;

end

State <= `IDLE;

end

`R_ENABLE : begin

if (PSEL && !PWRITE) begin

PRDATA <= RAM[PADDR];

end

State <= `IDLE;

end

default: begin

State <= `IDLE;

end

endcase

end

end

endmodule

APB Slave状态机设计的更多相关文章

- 08-FPGA状态机设计实例——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.学习状态机的相关概念 2.理解一段式.两段式以及三段式状态机的区别以及优缺点 实验平台:芯航线FPGA核心板 实验原理: 状态机全称是有限状态机(fin ...

- 实验七 状态机设计ADC0809采样控制电路

一.实验目的 学习用状态机实现A/D转换器ADC0809的采样控制电路. 二.实验内容 利用QuartusⅡ实现A/D转换器ADC0809的采样控制电路状态机设计:给出仿真波形.最后进行引脚锁定并进行 ...

- FPGA 状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy状态机. Moore状态机 其最大特点是输出只由当前状态确定,与输入无关.Moore状态机的 ...

- FPGA学习笔记(八)—— 状态机设计实例之独立按键消抖

###### [该随笔中部分内容转载自小梅哥] ######### 独立按键消抖自古以来在单片机和FPGA中都是个不可避免的问题,首先,解释一下什么叫做按键抖动,如图,按键在按下和松开的那个瞬间存在大 ...

- PCI总线目标接口状态机设计

module state_machine (devsel_l, trdy_l, stop_l, pci_ad_oe, dts_oe, par_oe, bk_oe, pci_ad_en, hi ...

- i2c状态机方法设计-verilog

2010-09-05 21:04:00 verilog语言基础学的差不多了.接着就是看看华为的语言编写规范.状态机设计方法是fpga的重要设计方法.所以我要记上一笔. 只要会FSM方法,用fpga编写 ...

- 基于AHB总线的master读写设计(Verilog)

一.AHB总线学习 1. AHB总线结构 如图所示,AHB总线系统利用中央多路选择机制实现主机与从机的互联问题.从图中可以看出,AHB总线结构主要可分为三部分:主机.从机.控制部分.控制部分由仲裁器. ...

- 【第一季】CH04_FPGA设计Verilog基础(一)Enter a post title

[第一季]CH04_FPGA设计Verilog基础(一) 4.1 Verilog HDL 代码规范 u 项目构架设计 项目的构架用于团队的沟通,以及项目设计的全局把控 u 接口时序设计规范 模块和模块 ...

- 【原创】EtherCAT主站IgH解析(一)--主站初始化、状态机与EtherCAT报文

目录 1 启动脚本 1.1 start 1.2 stop 2 主站实例创建 2.1 Master Phases 2.2 数据报与状态机 数据报 状态机 2.3 master状态机及数据报初始化 2.4 ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

随机推荐

- 华企盾DSC:wps个人模式无策略组新建的文件仍然加密

解决方法:右键wps安装目录手动解密即可(原因:wps模板被加密导致)

- zabbix常用监控项

https://blog.csdn.net/xkjcf/article/details/78559273?locationNum=10&fps=1 agent.ping #agent是否在线 ...

- 斯坦福 UE4 C++ ActionRoguelike游戏实例教程 13.使用GameplayTag实现使用钥匙卡打开箱子

斯坦福课程 UE4 C++ ActionRoguelike游戏实例教程 0.绪论 概述 本篇文章将会展示Gameplay另一个用法,也就是我们最常见的使用特定道具交互特定的机关.例如本文要实现的,获得 ...

- Programming abstractions in C阅读笔记:p181-p183

<Programming Abstractions In C>学习第61天,p181-p183总结. 一.技术总结 1.linear search algorithm 2.lexicogr ...

- 一文带你搞懂从动态代理实现到Spring AOP

摘要:本文主要讲了Spring Aop动态代理实现的两种方式. 1. Spring AOP Spring是一个轻型容器,Spring整个系列的最最核心的概念当属IoC.AOP.可见AOP是Spring ...

- 华为中国生态大会2021举行在即,GaussDB将重磅发布5大解决方案

摘要:企业数字化转型如火如荼,云成为数字化与新基建的关键要素,数据成为智能时代新的生产资料和企业数字化的生命,而数据库则是支撑数据生命线的底座. 本文分享自华为云社区<华为中国生态大会2021举 ...

- 物联网设备上云难?华为云IoT帮你一键完成模型定义,快速在线调试设备

摘要:在不到3分钟的操作里,不仅完成了一款智慧烟感设备在云端的模型定义,还通过在线调试了解到了设备和远端通信的过程. 本文分享自华为云社区<物联网设备上云难?华为云IoT帮你一键完成模型定义,快 ...

- 跟我读论文丨ACL2021 NER BERT化隐马尔可夫模型用于多源弱监督命名实体识别

摘要:本文是对ACL2021 NER BERT化隐马尔可夫模型用于多源弱监督命名实体识别这一论文工作进行初步解读. 本文分享自华为云社区<ACL2021 NER | BERT化隐马尔可夫模型用于 ...

- 开心档之CSS 测验

目录 CSS 测验 编辑 CSS 测验 CSS测验是一种衡量前端开发人员对CSS的熟练程度的测试.通过CSS测验,可以评估一个人对CSS语言的掌握程度和应用能力,帮助公司或招聘方挑选合适的人才. ...

- [BitSail] Connector开发详解系列三:SourceReader

更多技术交流.求职机会,欢迎关注字节跳动数据平台微信公众号,回复[1]进入官方交流群 Source Connector 本文将主要介绍负责数据读取的组件SourceReader: SourceRead ...