Altera DDR2 IP核学习总结1-----------SRAM,DRAM

SRAM,DRAM,SDRAM和DDR2这些芯片详解网上铺天盖地的各种资料都有,这里只是根据个人习惯做一下总结,方便记忆。

详细资料可以参考https://wenku.baidu.com/view/36eb2521af45b307e8719786.html?sxts=1560173120906

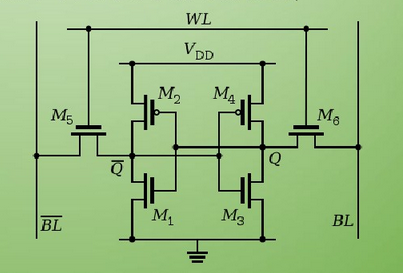

SRAM基本存储单元结构

SRAM中的每一bit存储在由四个场效应管(M1-M4)构成的两个交叉耦合的反相器中,另外两个场效应管(M5,M6)是存储基本单元

到用于读写的位线(Bit Line)的控制开关。

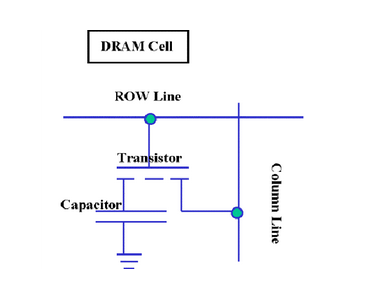

DRAM基本存储单元结构

DRAM的每一个Bit都由一个MOS管和一个电容组成,通过ROW LINE也就是MOS管的栅极来控制电容跟Column Line的导通与关闭,

通过Column Line来读取电容的高低电平。

优缺点比较:

地址总线差异:SRAM分为单地址总线,DRAM为双地址总线(行地址,列地址)原因是因为存储1bit的数据SRAM需要4-6个晶体管,

但是DRAM仅仅需要1个晶体管,这样相同容量的SRAM的体积比DRAM大至少四倍。这意味着DRAM没有足够的空间安放同样数量的引脚

(因为针脚并没有因此减少4倍)。如果为了安装同样数量的针脚而把DRAM芯片的体积加大,就会提高芯片的生产成本和功耗,所以减少

针脚数目也是必要的。对于现在的大容量DRAM芯片,多路寻址技术已经是必不可少的了。

读写速率差异:SRAM可以运行在比DRAM更高的频率,SRAM需要2-3个时钟周期来获得想要的数据(这里我们暂时忽略CPU,芯片组核内存DIMM

控制电路之间的延迟),同样的过程DRAM需要大约3-9个时钟周期。原因是因为DRAM采用一个晶体管和一个电容组成,这样的组成虽然是目前

最经济的方式,但是电容储存的电荷实惠慢慢泄露的,为了保证内存中数据的正确性需要不时的刷新内存,电容需要电流进行充电,而电流充电的

过程是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的,

这就意味着DRAM基本存储单元大约有1%的时间用在刷新上。同事读取内存会导致内存基本存储单元中的电荷丢失,所以每当DRAM被访问之后都要进行

刷新,以维持访问之前的状态,否则就会导致数据丢失。因为SRAM不存在刷新问题,SRAM采用了4个晶体管核两个电阻器构成的结构,它并不利用电容器

来存储数据,而是通过切换晶体管的状态来实现,所以读取的过程中不会造成SRAM内存数据的丢失。

综上所述两种芯片速率,成本,容量差异较大,所以两者都有自己更适合的场所。

Altera DDR2 IP核学习总结1-----------SRAM,DRAM的更多相关文章

- Altera DDR2 IP核学习总结3-----------DDR2 IP核的使用

根据上一篇生成的IP核,例化之后如上图,Local开头的数据是用户侧数据,其他数据暂时不用纠结,不用管. 这些是需要关注的信号,但是初学阶段很难对这些信号形成具体的概念,这里参考明德扬的代码进行二次封 ...

- Altera DDR2 IP核学习总结2-----------DDR2 IP核的生成

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next PLL reference clock frequency填入板子晶振的频率50MHZ,这里设 ...

- altera DDR2 IP核之仿真

在生成的IP核文件夹下,有一个testbench文件夹,里面包含了一个example测试激励和DDR2仿真模型. 如下 20 -rw-r--r-- 1 Administrator 197121 171 ...

- 关于AXI4-Stream to Video Out 和 Video Timing Controller IP核学习

关于AXI4-Stream to Video Out 和 Video Timing Controller IP核学习 1.AXI4‐Stream to Video Out Top‐Level Sign ...

- xilinx AXI相关IP核学习

xilinx AXI相关IP核学习 1.阅读PG044 (1)AXI4‐Stream to Video Out Top‐Level Signaling Interface (2)AXI4‐Stream ...

- 如何使用和了解ALTERA的IP核

可以通过直接对IP核进行仿真验证,通过波形来分析IP核的功能和工作方式,以及各个寄存器之间的工作关系. 也可以通过查看用户指导手册来学习IP核,如下图.

- Altera FIFO IP核时序说明

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- 关于ALTERA生成IP核卡住

最近搞fft,用的quartus13.1版本,发现quartus和modelism存在各种各样的坑啊,fftIP核大家可能也遇到过ip核 生成到一半就卡住的问题,之前我是通过换系统解决的,但是好景不长 ...

- altera DDR2 ip使用笔记之IP核生成

IP核生成 Quartus生成DDR2 ip流程如下: 点击菜单栏的Tools->MegaWizard Plug-In Manager,弹出 选择IP类型,保持路径即文件名等,如下图 点击n ...

随机推荐

- Gym - 102040F Path Intersection (树链剖分+线段树)

题意:给出棵树上的k条路径,求这些路径的公共点数量. 将每条路径上的点都打上标记,被标记过k次的点就是公共点了.由于公共点形成的区间是连续的,因此直接在线段树上暴搜即可在$O(logn)$求出一条链上 ...

- eclipse error pages 打红X的解决方法

建一个Maven项目转为web项目的时候,这里总有这么多文件,而且还会有一个Error Pages的错红的红叉,看着很不爽. 虽然项目中没有出现过错误,感觉是个错误,解决方法如下.原来这是eclips ...

- radio(单选框)/checkbox(复选框) 美化

由于某种原因,可能需要对单选框(radio)或复选框(checkbox)进行美化,那么直接修改样式是行不通,要实现就需要添加js,以下js依赖于jquery radio.js: function ra ...

- Python的语句---钱中平

python中的两种语句:1.if条件控制语句 格式: if: a = int(input("请输入第一个数:"))b = int(input("请输入第二个数:&quo ...

- JS实现表格隔行变色

用到的鼠标事件:(1)鼠标经过 onmouseover:(2)鼠标离开 onmouseout 核心思路:鼠标经过 tr 行的时候,当前行会改变背景颜色,鼠标离开的时候去掉背景颜色. 注意:第一行(th ...

- js 创建节点 以及 节点属性 删除节点

case 'copy': var B1 = document.getElementById("B1"); //获得B1下的html文本 var copy_dom = documen ...

- qtmaind.lib(qtmain_win.obj) : error LNK2019: 无法解析的外部符号 __imp_CommandLineToArgvW,该符号在函数 WinMain 中被引用

报错:qtmaind.lib(qtmain_win.obj) : error LNK2019: 无法解析的外部符号 __imp_CommandLineToArgvW,该符号在函数 WinMain 中被 ...

- CSS 内边距 padding 属性

CSS padding 属性定义元素边框与元素内容之间的空白区域. ㈠padding(填充) ⑴当元素的 padding(填充)内边距被清除时,所释放的区域将会受到元素背景颜色的填充. ⑵单独使用 p ...

- https://stackblitz.com/github/cwiki-us-angular/cwiki-us-angular-app 导入后如何添加到自己的项目

将 https://stackblitz.com/github/cwiki-us-angular/cwiki-us-angular-app 导入到界面后,如何将这个项目添加到自己的项目里面. 然后再自 ...

- Python3学习笔记(十三):装饰器

装饰器就是一个闭包,它的主要作用是在不改变原函数的基础上对原函数功能进行扩展. 我们先来写一个简单的函数: from time import sleep def foo(): print(" ...