AD7928

实验室板子soc-de1自带的7928芯片,下面记录一下它的参数

吞吐速率 : 1MSPS

吞吐速率 : 是指ADC器件单位时间内能处理的任务数或输出结果的数量。单位:SPS(Samples per second)

通信协议·:SPI协议 四根线 SCLK DIN SOUT CS_N

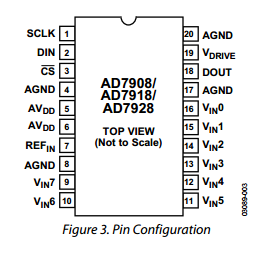

引脚配置和功能描述:

SCLK 串行时钟

DIN 数据输入,在SCLK的下降沿写入寄存器

CS_n 片选控制,在低电平时,数据有效

REFin AD7928的基准电压输入。

Vin0至Vin7 模拟输入0到模拟输入7.通过控制ADD2到ADD0来选择通道,输入电压范围0~REFin 或者 0~2REFin

DOUT 数据输出。AD7928的转换结果在SCLK的下降沿逐个输出。输出的数据流包含一个前置的0和3个地址位

然后是12个转换数据位(MSB优先)。输出的数据可以是二进制或者二进制的补码。

控制寄存器

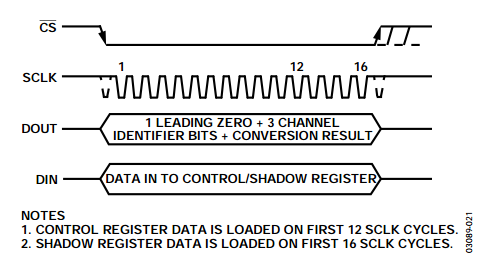

每次数据传输需要16个串行时钟,只有在前12个SCLK的下降沿,提供的信息才会写入被控制的寄存器。MSB在前

WRITE : 1 后续的11位写入寄存器 0 则不写入

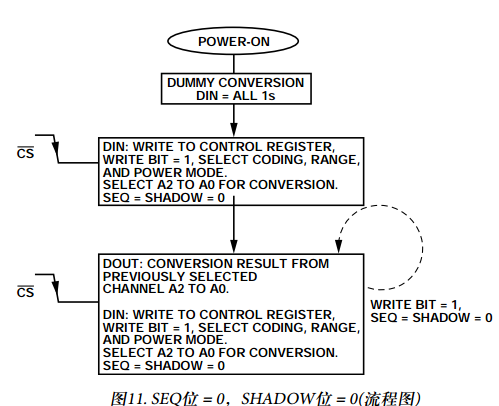

SEQ,SHADOW : 0 0 的话,序列功能未被使用,每次转换的通道由上一次的通道地址ADD2 ~ ADD0决定。

PM1,PM0 : 1 1 正常工作

RANGE : 0 则模拟输入的范围为 0 ~ 2XREFin 1则0~REFin

CODING : 0为二进制的补码方式,1则标准的二进制

下面给AD9854的时序控制图

驱动程序

/*----------------------------------------------------------------------- Date : 2017-08-01

Description : Design for AD7928. -----------------------------------------------------------------------*/ module ad7928

(

//global clock

input clk, //system clock

input rst_n, //sync reset //ad7928 interface

output reg sclk_ad,

output reg din, //逻辑输入

input dout, //逻辑输出

output reg cs_n, //片选使能端 //user interface output reg [:] ad_data // ); //--------------------------------

//Funtion : 10M 分频

parameter CLK_10M = 'd5;

reg [:] cnt_clk; always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_clk <= 'd0;

else if(cnt_clk >= CLK_10M - 'b1)

cnt_clk <= 'd0;

else

cnt_clk <= cnt_clk + 'b1;

end wire clk_10m_value = (cnt_clk >= CLK_10M - 'b1) ? 1'b1 : 'b0; //--------------------------------

//Funtion : ad7928 参数定义

parameter SPI_DATA = 'b100_000_11_0001_0000;

parameter ONE_S = 'd10;//_000_000; //--------------------------------

//Funtion : spi state

reg [:] spi_state;

reg [:] cnt_wait;

reg [:] ad_ser_data;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

spi_state <= 'd0;

ad_ser_data <= 'd0;

cnt_wait <= 'd0;

sclk_ad <= 'd0;

din <= 'd0;

cs_n <= 'd0;

end

else if(clk_10m_value)

begin

case(spi_state)

//上电等待

'd0 :

begin

if(cnt_wait >= ONE_S - 'b1)

spi_state <= 'd1;

else

cnt_wait <= cnt_wait + 'b1;

end 'd1 :

begin

sclk_ad <= 'b1;

cs_n <= 'b1;

spi_state <= 'd2;

ad_ser_data <= 'd0;

end 'd2 :

begin

cs_n <= 'b0;

spi_state <= 'd3;

end

//

'd3 :

begin

din <= SPI_DATA[];

spi_state <= 'd4;

end 'd4 :

begin

sclk_ad <= 'b0;

spi_state <= 'd5;

end

//

'd5 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd6;

end 'd6 :

begin

sclk_ad <= 'b0;

spi_state <= 'd7;

end

//

'd7 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd8;

end 'd8 :

begin

sclk_ad <= 'b0;

spi_state <= 'd9;

end

//

'd9 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd10;

end 'd10 :

begin

sclk_ad <= 'b0;

spi_state <= 'd11;

end

//

'd11 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd12;

end 'd12 :

begin

sclk_ad <= 'b0;

spi_state <= 'd13;

end

//

'd13 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd14;

ad_ser_data <= dout; //[7]

end 'd14 :

begin

sclk_ad <= 'b0;

spi_state <= 'd15;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd15 :

begin

sclk_ad <= 'b1;

ad_ser_data <= ad_ser_data + dout; //[6]

din <= SPI_DATA[];

spi_state <= 'd16;

end 'd16 :

begin

sclk_ad <= 'b0;

spi_state <= 'd17;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd17 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd18;

ad_ser_data <= ad_ser_data + dout; //[5]

end 'd18 :

begin

sclk_ad <= 'b0;

spi_state <= 'd19;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd19 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd20;

ad_ser_data <= ad_ser_data + dout; //[4]

end 'd20 :

begin

sclk_ad <= 'b0;

spi_state <= 'd21;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd21 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd22;

ad_ser_data <= ad_ser_data + dout; //[3]

end 'd22 :

begin

sclk_ad <= 'b0;

spi_state <= 'd23;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd23 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd24;

ad_ser_data <= ad_ser_data + dout; //[2]

end 'd24 :

begin

sclk_ad <= 'b0;

spi_state <= 'd25;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd25 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd26;

ad_ser_data <= ad_ser_data + dout;//[1]

end 'd26 :

begin

sclk_ad <= 'b0;

spi_state <= 'd27;

ad_ser_data <= ad_ser_data << 'b1;

end

//

'd27 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd28;

ad_ser_data <= ad_ser_data + dout;//[0]

end

'd28 :

begin

sclk_ad <= 'b0;

spi_state <= 'd29;

end

//

'd29 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd30;

end

'd30 :

begin

sclk_ad <= 'b0;

spi_state <= 'd31;

end

//

'd31 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd32;

end

'd32 :

begin

sclk_ad <= 'b0;

spi_state <= 'd33;

end

//

'd33 :

begin

sclk_ad <= 'b1;

din <= SPI_DATA[];

spi_state <= 'd34;

end 'd34 :

begin

sclk_ad <= 'b0;

spi_state <= 'd1;

end default : ;

endcase

end

end //--------------------------------

//Funtion : ad_data

//reg [7:0] ad_data; always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

ad_data <= 'd0;

else if(spi_state == 'd34)

ad_data <= ad_ser_data;

end endmodule

AD7928的更多相关文章

随机推荐

- Ubuntu下Tomcat初始配置

1.下载tomcat安装包 从tomcat官方网站http://tomcat.apache.org下载安装包,然后解压到某个目录,比如: ~/opt/apache-tomcat-7.0.63官方文档中 ...

- Java IO学习笔记二

Java IO学习笔记二 流的概念 在程序中所有的数据都是以流的方式进行传输或保存的,程序需要数据的时候要使用输入流读取数据,而当程序需要将一些数据保存起来的时候,就要使用输出流完成. 程序中的输入输 ...

- 就是要你懂Java中volatile关键字实现原理

原文地址http://www.cnblogs.com/xrq730/p/7048693.html,转载请注明出处,谢谢 前言 我们知道volatile关键字的作用是保证变量在多线程之间的可见性,它是j ...

- RabbitMQ系列教程之三:发布/订阅(Publish/Subscribe)

(本教程是使用Net客户端,也就是针对微软技术平台的) 在前一个教程中,我们创建了一个工作队列.工作队列背后的假设是每个任务会被交付给一个[工人].在这一部分我们将做一些完全不同的事情--我们将向 ...

- SQL Server事务的隔离级别和锁

背景 当用户并发尝试访问同一数据的时,SQL Server尝试用锁来隔离不一致的数据和使用隔离级别查询数据时控制一致性(数据该如何读取),说起锁就会联想到事务,事务是一个工作单元,包括查 ...

- .NET Core 2.0 Preview2 发布汇总

前言 关于 ASP.NET Core 2.0 的新功能可以查看我的这篇博客. 这篇文章是 Priview2中的一些改进. .NET Core 2.0 - Preview2 Azure 的改进 Dock ...

- Kafka 源代码分析之LogSegment

这里分析kafka LogSegment源代码 通过一步步分析LogManager,Log源代码之后就会发现,最终的log操作都在LogSegment上实现.LogSegment负责分片的读写恢复刷新 ...

- 【Android Developers Training】 21. 创建一个可变动的UI

注:本文翻译自Google官方的Android Developers Training文档,译者技术一般,由于喜爱安卓而产生了翻译的念头,纯属个人兴趣爱好. 原文链接:http://developer ...

- XML 新手入门基础知识(复制,留着自己看)

如果您是 XML 新手,本文将为您介绍 XML 文档的基础结构,以及创建构造良好的 XML 需要遵循的规则,包括命名约定.正确的标记嵌套.属性规则.声明和实体.您还可以从本文了解到 DTD 和 sch ...

- 移动端Touch事件基础

1.三个常用的移动端事件 ontouchstart 手指按下时触发 ontouchmove 手指移动时触发 ontouchend 手动抬起时触发 注意:这些事件当作事件属性使用时,不兼容谷歌浏览器. ...