转载:关于JESD204B转换器与FPGA匹配的设计关键点

http://www.dzsc.com/data/2014-11-27/107442.html

随着更多的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA供应商多年来一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC和DAC不能通过这些高速串行接口进行配置,就是说FPGA与转换器无法与任何常用标准接口,利用高串行-解串(SERDES)带宽。

JESD204B接口针对支持更高速转换器不断增长的带宽需求而开发,以填补该空白。作为第三代串行数据链路标准,JESD204B提供更高的最大通道速率(每通道高达12.5 Gbps),支持确定延迟和谐波帧时钟。该接口借助兼容开放市场FPGA解决方案且可扩展的高性能转换器,可轻松传输大量待处理的数据。

大多数信号处理系统首先是通过其模拟或RF频率、动态范围和采样速率进行定义,以建立转换器选择标准。然而,当与FPGA匹配进行数据处理时,无论如何都不能忽视对转换器数字接口的考量。只要了解新型JESD204B接口并牢记一些高级考量因素,那么为您的FPGA选择合适的JESD204B转换器其实并不难。以下是一些关于JES204B转换器与FPGA匹配的常见问题及解答。重点说明采用这款新型串行接口进行转换器设计时的关键点。

FPGA对于JESD204B需要多少速度?

通常,设计人员实际上是问JESD204B与转换器接口应用中FPGA需要支持的收发器线路速率。收发器是FGPA中的高速串行接口,其可以发送或接收数据及恢复内嵌时钟。收发器主要作为高速数据端口,与功能无关。但如果在其周围配置合适的固件,它们可以为许多不同的接口协议提供

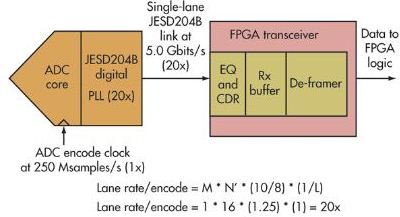

数字支持。例如,FPGA收发器可以充当并行至串行发射器或串行至并行接收器(图1)。

图1.例如,FPGA收发器可以充当并行至串行发射器或串行至并行接收器。

对于JESD204B这样的高速串行接口,FPGA收发器可以在系统中以两种方式发挥作用。当FPGA支持ADC外部数据下游采集时,它是作为串行数据接收器。当收发器接收数据时,它将高速串行流转换为并行帧数据,在FPGA中进一步完成下游处理。将数据从串行格式转换到并行格式前,需要用到自适应增益控制(AGC)、均衡(EQ)和时钟/数据恢复(CDR)功能。

当FPGA向DAC输送数据时,它会执行发射器功能。作为发射器,它将形成帧数据,并通过高速接口串行发送出去。预加重功能(后续会谈到)放大该信号,以使传输数据尽可能更完整。

通常情况下,系统的模拟采样速率或更新速率将间接决定JESD204B接口上的FPGA收发器线路速率。转换器的时钟或编码速率通过锁相环(PLL)倍频来实现JESD204B位速率。转换器支持的最大线路速率可能不是系统所需,而应当通过已知的倍频器进行调节。

图2显示了一个采用250 MSPS编码时钟的单一(M = 1)16位(N' = 16)ADC,它在20倍编码时钟速率(5 Gbps)下通过单一JESD204B通道(L = 1)发送数据。该运算包括8位/10位编码开销。转换器采用与250 MSPS不同的编码时钟,输出通道速率会相应地向上或向下调节至20倍的当前编码时钟速率。

图2.采用250 MSPS编码时钟的单一16位ADC可以通过单一JESD204B通道在5.0 Gbps速率下输出采样数据。本例中,JESD204B通道速率是编码时钟频率的20倍。

哪些转换器特性可用于延长系统中的JESD204B链路,并仍能保持优异的数据完整性?

JESD204B规范列出了符合20cm传输线路要求的标准。印刷电路板(PCB)走线材料的物理特性对于信号在传输期间会遇到何种衰减起主导作用。然而,多数转换器和FPGA上的有源通道补偿技术有助于提高链路性能。

转换器或FPGA发射器输出可以提高串行数据的高带宽部分,同时保持低带宽部分不变。该技术被称为预加重。由于低通信号衰减首先影响信号的高带宽部分(上升和下降时间),预加重有助于提高串行信号传输距离。

对于接收器也一样,DAC或FPGA可以向输入信号提供自动增益控制和EQ,以提高传输线路末端可见信号的高频部分。该技术通常具有不同的增益和均衡器设置,以帮助根据系统需求优化数据恢复。除了均衡阶段,Xilinx还提供内部探测工具,从而将在FPGA中见到的数据眼形象化(图3)。

图3.在ADC至FPGA的JESD204B传输线路中转换器/发射器的预加重,放大了信号的高带宽部分,同时接收器/FPGA的均衡可恢复衰减信号。Xilinx的内部眼扫描工具可对FPGA中的眼进行内部探测。

针对转换器还能做些什么处理,以减少发送给或来自于FPGA的数据量?

为了减小FPGA的计算负担,一些转换器供应商在整个转换器解决方案中添加了数字处理部分。一些信号处理系统只需使用经滤波的信号带宽部分。发射和处理送至或来自FPGA的全带宽数据是一种开销负担,完全没有必要。

例如,ADC可实现数字下变频(DDC)功能,可以有效地将将每四个模拟采样中的第一个发送给FPGA.数字滤波数据可在JESD204B接口上使用更低的数据速率,并且无需在FPGA上配置DDC时钟。

相反,DAC插值功能可以允许仅使用1/4数据速率,将数据从FPGA发送至DAC,并且使用复杂算法对四个采样中的其余三个进行数字插值。DAC插值方式仅可以传输数据的一个子集,然后在采用模拟格式输出前在转换器中完全组装。

我的FPGA需要支持多少SERDES通道/转换器?

无论您的链路是采用单一转换器还是多个转换器,转换器接与FPGA接口的JESD204B通道数与线路速率、转换器采样速率、数据包效率直接相关。虽然转换器可以提供四条JESD204B通道,但以1/2最大转换器采样速率运行的系统可能仅需使用两条通道。每个转换器可依不同的设计来实现不同的JESD204B通道数、速度和数据包。可查看转换器数据手册,看看什么选项最适合您的应用。

我能够将多个转换器与单一FPGA实现同步吗?

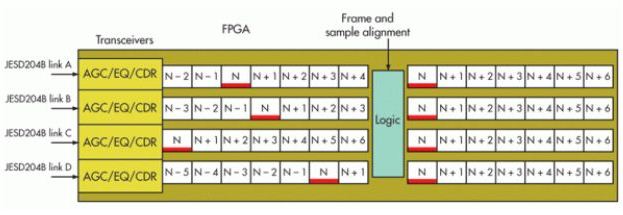

是的,这可以做到,只要FPGA支持的通道数足以满足应用所需。多ADC系统的主要难点之一是对齐采样信号,这些信号在从模拟至数字采样过程中具有不同的延迟时间。JESD204B接口对系统参考信号(SYSREF)有相应规定。这有助于为系统中的各转换器创立确定的延迟时间,从而为多

转换器同步提供解决方案。由于JESD204B上采用数据帧,来自于多个ADC的数据帧就可以在FPGA的后处理步骤中对齐。这样就可以校正转换器和FPGA收发器之间的延迟不匹配。

同样,FPGA在将数据发送至多个DAC前,可以先将数据进行帧对齐。这是考虑到那些需要通过单一或几个FPGA来同步多个转换器的系统。一些转换器供应商还在正式技术规格外提供额外的同步功能,用于标注特定采样。如果您的系统需要多转换器同步,需尽量减少转换器连接的JESD204B通道数,并选择最强性能的FPGA.

JESD204B协议中规定,需对齐来自于多个ADC、具有不同延迟的采样数据从而在FPGA中实现同步。图4显示了来自多个链路的帧数据或标记的样本如何针对同步处理进行重对齐。

我的应用需要怎样的FPGA布速来处理数据?

JESD204B接口采用嵌入式时钟来进行高速串行数据传输。然而,FPGA需要更慢的参考时钟作为主时钟来处理数据。FPGA系列和产品的布速决定这一功能。考虑FPGA需选择哪种方式处理转换器数据相当重要。例如,负责采集周期性离散数据集至存储器的应用,和全速连续处理并发送数据的应用,这两者可能需要不同的FPGA布速。

如何让JESD204B在FPGA上工作?

该问题的另一种表达可能是“我应当从FPGA制造商那里获得JESD204B固件的知识产权(IP)还是自己开发?” Xilinx等FPGA供应商均提供用于JESD204、JESD204A和JESD204B接口的自主IP解决方案。这些解决方案可能略有差异,这取决于JESD204的产品换代以及FPGA产品的收发器速度。

确保尽早完成转换器选型,明确您的系统中需要采用的FPGA形式和相关IP.选型时应当考虑使用哪家FPGA供应商的产品、使用哪一代JESD204、FPGA的系列和型号,以及您内部实现IP所需的技术代码编写能力。

一些JESD204B转换器可能需要特殊的额外应用层,或是围绕IP的代码“包装器”,这基本上是一套独有的固件指令。如果是这种情况,转换器供应商应当确认并提供应用代码以连接FPGA IP.应当在数据手册中列明需要哪些内容来支持JESD204B转换器链路。一些转换器制造商还开发了一种在他们的器件和FPGA固件间进行彻底验证测试的电池,以证明产品的稳定性。

转换器使用具有收发器“频率洞”的FPGA时会出现问题吗?

一些FPGA产品支持运行过程中存在间隙(无法使用已知的频率范围)的收发器。这会使JESD204B通道频率规划更复杂一点,但仍在可控范围内。针对转换器采样速率和JESD204B通道速率进行频率规划是使频率远离收发器间隙的关键。

大多数转换器系统通常都有固定的采用频率。需要对偶然的独特应用进行支持的情况只是少数。根据系统转换器的固定采样速率和之前讨论的JESD204B速率倍频器,系统设计人员可以确定收发器频率间隙是否会对系统造成问题。

即使发现期望的通道频率刚好在间隙范围内,仍需查看转换器数据手册,看看是否有另一些选项可用来调整通道速率。例如,可以改变方程中的一些其他变量,如通道数量或JESD204B采用分辨率信息,来提高或降低频率曲线,以避开收发器频率间隙。

图4.JESD204B协议中规定,对齐来自于多个ADC、具有不同延迟的采样数据从而在FPGA中实现同步。来自多个链路的帧数据或标记的样本可针对同步处理进行重对齐。

小结

新型转换器与JESD204B之类的FPGA接口较为复杂,使其显得难于处理,此时分解关键系统需求至关重要。必须了解采样速率和JESD204B通道速率倍频器。根据IP支持、收发器数、收发器速度和频率间隙等因素来进行规划和选择合适的FGPA产品,有助于正确选择转换器。通过重点关注一些与FPGA相匹配的高级标准,可简化选择合适的JESD204B转换器的过程。

转载:关于JESD204B转换器与FPGA匹配的设计关键点的更多相关文章

- Xilinx FPGA 的PCIE 设计

写在前面 近两年来和几个单位接触下来,发现PCIe还是一个比较常用的,有些难度的案例,主要是涉及面比较广,需要了解逻辑设计.高速总线.Linux和Windows的驱动设计等相关知识. 这篇文章主要针对 ...

- FPGA中计数器设计探索

FPGA中计数器设计探索,以计数器为32位为例: 第一种方式,直接定义32位计数器. reg [31:0]count; quartus ii 下的编译,资源消耗情况. 85C模型下的时钟频率. 0C模 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA Asynchronous FIFO设计思路(2)

FPGA Asynchronous FIFO设计思路(2) 首先讨论格雷码的编码方式: 先看4bit的格雷码,当MSB为0时,正向计数,当MSB为1时,即指针已经走过一遍了,最高位翻转,此时的格雷码是 ...

- FPGA Asynchronous FIFO设计思路

FPGA Asynchronous FIFO设计思路 将一个多位宽,且在不停变化的数据从一个时钟域传递到另一个时钟域是比较困难的. 同步FIFO的指针比较好确定,当FIFO counter达到上限值时 ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 【转载】使用Pandas进行数据匹配

使用Pandas进行数据匹配 本文转载自:蓝鲸的网站分析笔记 原文链接:使用Pandas进行数据匹配 目录 merge()介绍 inner模式匹配 lefg模式匹配 right模式匹配 outer模式 ...

- 转载:基于HALCON的模板匹配方法总结

转载链接: http://blog.csdn.net/b108074013/article/details/37657801 很早就想总结一下前段时间学习HALCON的心得,但由于其他的事情总 ...

- 小梅哥FPGA数字逻辑设计教程——基于线性序列机的TLC5620型DAC驱动设计

基于线性序列机的TLC5620型DAC驱动设计 目录 TLC5620型DAC芯片概述: 2 TLC5620型DAC芯片引脚说明: 2 TLC5620型DAC芯片详细介绍: 3 TLC ...

随机推荐

- P1865 A % B Problem

(一道很水的题) (反正我第一眼看的时候也是这么想的) 题目背景 题目名称是吸引你点进来的 实际上该题还是很水的 题目描述 区间质数个数 输入输出格式 输入格式: 一行两个整数 询问次数n,范围m 接 ...

- linux内存源码分析 - 内存回收(整体流程)

本文为原创,转载请注明:http://www.cnblogs.com/tolimit/ 概述 当linux系统内存压力就大时,就会对系统的每个压力大的zone进程内存回收,内存回收主要是针对匿名页和文 ...

- BZOJ4061/Gym100624F CERC2012 Farm and Factory 最短路、切比雪夫距离

传送门--BZOJCH 传送门--Vjudge 设\(f_i\)表示\(i\)到\(1\)号点的最短距离,\(g_i\)表示\(i\)到\(2\)号点的最短距离,\(s_i\)表示\(n+1\)号点到 ...

- C# zip -ICSharpCode.SharpZipLib

利用第三方组件 ICSharpCode.SharpZipLib download from: https://github.com/icsharpcode/SharpZipLib using S ...

- JavaEE学习之JPA中配置文件persistence.xml

下面是我从网上找到的关于JPA配置文件persistence.xml的相关描述: <?xml version="1.0" encoding="UTF-8" ...

- Project Tungsten:让Spark将硬件性能压榨到极限(转载)

在之前的博文中,我们回顾和总结了2014年Spark在性能提升上所做的努力.本篇博文中,我们将为你介绍性能提升的下一阶段——Tungsten.在2014年,我们目睹了Spark缔造大规模排序的新世界纪 ...

- 史上最全面的Neo4j使用指南

Neo4j图形数据库教程 Neo4j图形数据库教程 第一章:介绍 Neo4j是什么 Neo4j的特点 Neo4j的优点 第二章:安装 1.环境 2.下载 3.开启远程访问 4.测试 第三章:CQL 1 ...

- DOM操作 JS事件 节点增删改查

--------------------------习惯是社会的巨大的飞轮和最可贵的维护者.——威·詹姆斯 day 49 [value属性操作] <!DOCTYPE html><ht ...

- Mysql乱码问题总结

这两天研究了下Mysql的字符集编码和排序规则,有个很典型的问题就是乱码问题.所以小记一下. http://www.jianshu.com/p/4c6a27542df4 http://blog.csd ...

- H5 video标签的属性

35-video标签 video标签的属性 src: 用于告诉video标签需要播放的视频地址 autoplay: 用于告诉video标签是否需要自动播放视频 controls: 用于告诉video标 ...