Chipscope使用

作者:桂。

时间:2017-08-07 06:47:31

链接:http://www.cnblogs.com/xingshansi/p/7297482.html

前言

Chipscope在FPGA调试中被用来观察内部信号,程序里加入Chipscope相当于有了数字示波器。

本文主要记录Chipscope的基本操作,以及如何借助MATLAB对Chipscope的数据进行分析。

一、Chipscope使用

A-Chipscope简介

参考:ug029_ChipScope Pro 11.4 Software and Cores。

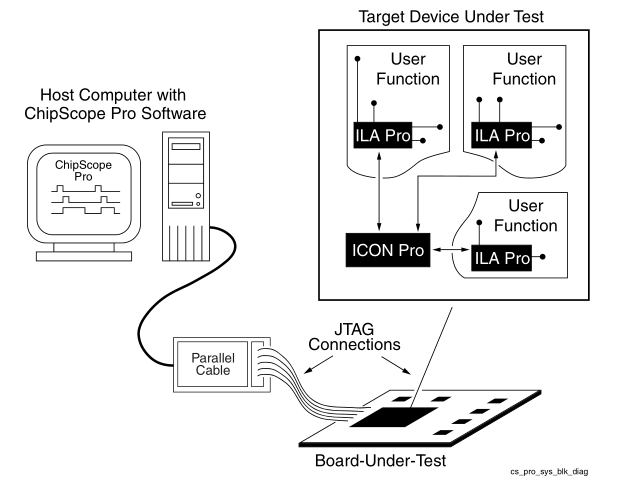

Chipscope只要一个JTAG(Joint Test Action Group)口,就可以访问到FPGA内部的所有信号。

核心:两个关键Core+Analyzer

Core-ILA:集成逻辑分析仪。连接信号,触发条件和触发时钟;

Core-ICON:是Analyzer和ILA联络的桥梁。只有一个,ICON负责管理多个ILA,提供通过JTAG口访问多个ILA的途径;

Analyzer:Chipscope的信号GUI界面

附加:

IBA(Integrated Bus Analyzer):用来Debug IBM coreconnect总线;

ATC(Agilent Trace Core):Agilent为Xilinx FPGA开发的支持片外采样数据存储的设备。

B-Chipscope Pro Core Inserter流程

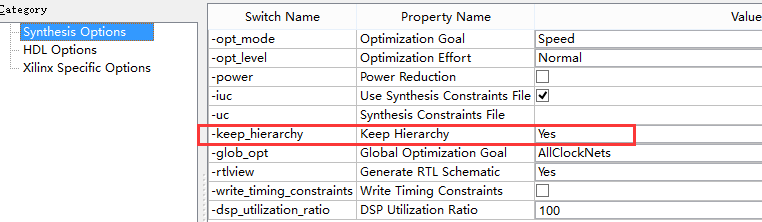

1)保留设计层次

XST 缺省设置是将设计打平以取得好的综合效果,因此需要设置:Synthesize XST → process properties:

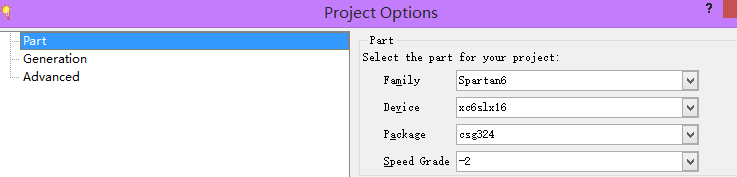

2)选择对应芯片

Core Generator —— New project —— 选择存放目录,并设置Part,如果指定语言需要设置Generation,语言默认VHDL,以S6为例:

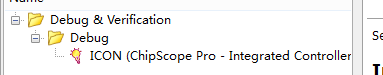

3)ICON设置

双击:

点击:Generate,完成最基本的ICON设置

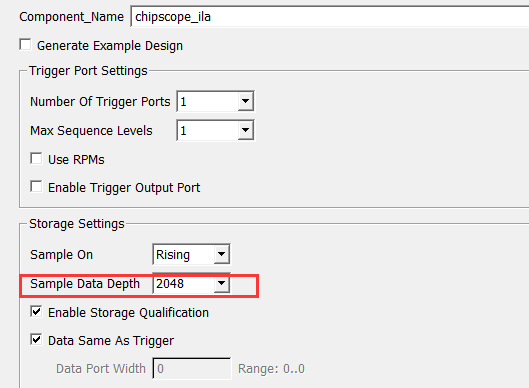

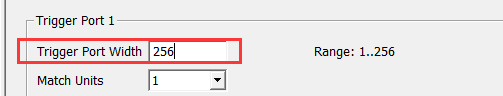

4)ILA设置

双击:

参数可人为设定,

触发端口数量最大为256

点击:Generate.

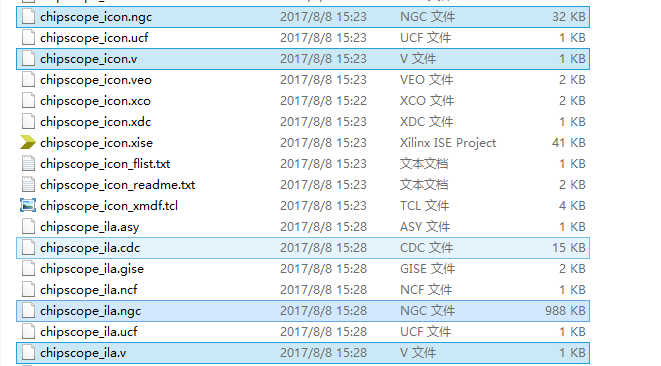

这样一来,便完成了ICON与ILA核的设置,如果工程中需要用到Chipscope,不必每次都要生成,只需将其中四个文件拷贝到对应工程目录下即可。

综合后的网表文件:*.ngc以及对应的工程*.v,ICON与ILA各两个,共四个文件:

其中两个*.v文件:

ila:

`timescale 1ns/1ps module chipscope_ila(

CONTROL,

CLK,

TRIG0) /* synthesis syn_black_box syn_noprune=1 */; inout [35 : 0] CONTROL;

input CLK;

input [255 : 0] TRIG0; endmodule

icon:

`timescale 1ns/1ps module chipscope_icon(

CONTROL0) /* synthesis syn_black_box syn_noprune=1 */; inout [35 : 0] CONTROL0; endmodule

Chipscope相当于内部的示波器,有了工具如何调用呢?利用Analyze(本质是GUI界面)即可。

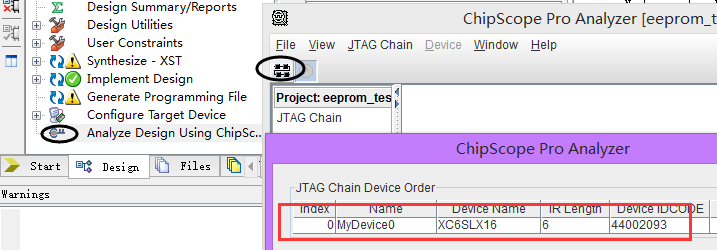

5)调用Analyze

打开Analyzer,通常可以自动识别芯片,点击OK。

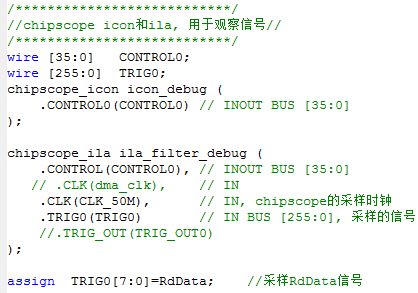

工程中,Rddata描述:

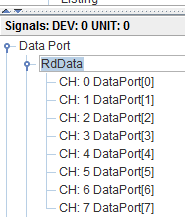

在Analyzer中设置:选中0~7,move to bus,new bus:

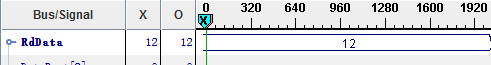

点击三角运行 :

:

即可抓取EEPROM写入FPGA的输入Rddata:

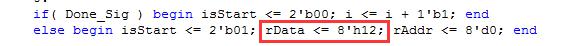

这与写入IIC总线的数据是一致的:

二、借助MATLAB对Chipscope的数据进行分析

通常希望从多个角度分析数据,因此考虑将Chipscope的数据导入MATLAB。

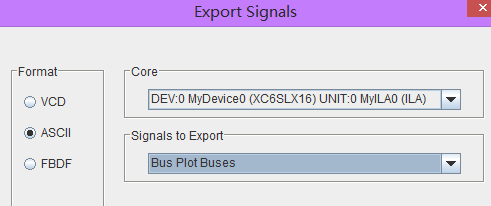

File —— Export:

输入存储的文件名,如test.prn;

利用MATLAB指令读取:xlLoadChipScopeData(‘test.prn’);

Chipscope使用的更多相关文章

- 56.ISE综合,在chipscope信号列表看不到

代码写好后,进行逻辑综合,在chipscope上添加被触发的信号时,发现有些在信号列表里看不到,这是因为这些信号没有参与到逻辑电路设计中,产生不想关的电路,综合器会默认优化资源. 还有一种情况是,对于 ...

- 41.使用Chipscope时如何防止reg_wire型信号被优化掉

随着FPGA设计复杂程度越来越高,芯片内部逻辑分析功能显得越来越重要.硬件层次上的逻辑分析仪价格十分昂贵,而且操作比较复杂.目前,FPGA芯片的两大供应商都为自己的FPGA芯片提供了软件层面上的逻辑分 ...

- Chipscope 仿真VmodCAM IIC程序

Chipscope 仿真VmodCAM IIC程序: 目的:熟悉EDK中建立chipscope 注意:zedboard使用digilent USB下载时,chipscope不能和SDK同时使用,否则芯 ...

- vivado中如何使用chipscope

如何使用chipscope 参考: https://www.cnblogs.com/liujinggang/p/9813863.html Xilinx FPGA开发实用教程---徐文波 田耘 1.Ch ...

- 【设计经验】2、ISE中ChipScope使用教程

一.软件与硬件平台 软件平台: 操作系统:Windows 8.1 开发套件:ISE14.7 硬件平台: FPGA型号:XC6SLX45-CSG324 二.ChipScope介绍 ChipScope是X ...

- ISE中的Force Process Up-to-Date功能:ISE中如何在未综合实现的前提下打开ChipScope ?

ISE中如何在未综合实现的前提下双击Analyze Design Using ChipScope打开ChipScope ? 有时,你正在ISE中调试程序,在ChipScope中看到了现象,顺手修改了程 ...

- 使用ChipScope Pro调试硬件

chipscope_icon提供与其他ChipScope内核的通信 chipscope_opb_iba促进传统片上外设总线(OPB)事务的监控 chipscope_plb_iba便于监控处理器本地总线 ...

- 怎样才能使用ChipScope 加入被优化掉的信号

在调试过程中常常遇到的一个问题就是,xilinx工具在逻辑综合的过程中,将自己RTL代码中的很多变量都优化掉了,使得调试的抓信号的过程很纠结.以下是解决方法: 1.右键synthesis,在综合选项里 ...

- ChipScope Pro Inserter - "ERROR:NgdBuild:924 - bidirect pad net '<oDRAM0_A>' is driving non-buffer primitives

解决方案: Using a IOBUF signal as a trigger for the ILA Inserter flow will cause a NGDBuild error. These ...

随机推荐

- Aliasing input/output properties

angular @input alias别名的使用. https://angular.io/guide/template-syntax#aliasing-io https://stackoverflo ...

- [CSS] Pseduo

#self aside li{ list-style-type: none;padding:5px;border-bottom: 1px solid #ccc;} #self aside li:las ...

- Java8新特性 - Lambda表达式 - 基本知识

A lambda expression is an unnamed block of code (or an unnamed function) with a list of formal param ...

- linux 用户管理,用户权限管理,用户组管理

linux 用户管理,用户权限管理,用户组管理 一:ls -l 命令 解释 第个d表示是目录,如果是文件是-,如果是连接是l 第2到4个 rwx 表示创建者的操作权限 r 读,w 写,x 执行 第5到 ...

- iOS日期加减

- (NSDate *)jsDateFromBeginDate:(NSDate *)beginDate todays:(int)days { NSDate *dateTemp = [[NSDate a ...

- 虚拟机下linux迁移造成MAC地址异常处理办法

虚拟机下linux迁移造成MAC地址异常处理办法 Linux无法启用网卡:Device eth0 has different MAC address than expected,ignoring解决 ...

- cordova 强制竖屏

orentation的默认值是default 可使用的值有:default, landscape (横屏), portait (竖屏) orentation可以将设备锁定方向,不受设备旋转影响. 方案 ...

- Eclipse 批量创建多级文件夹

Eclipse 批量创建多级文件夹 CreateTime--2018年3月8日08:23:24 Author:Marydon 1.选中要建立文件夹的父级目录-->右键-->New--& ...

- java 打包war包

jar -cvf news.war news war包放在Tomcat webApp中可以自动解压.

- MySQL Desc指令相关

MySQL Desc指令相关 2011-08-09 11:25:50| 分类: my基本命令 |举报 |字号 订阅 1.desc tablename; 例如 :mysql> desc jo ...