关于INTEL FPGA设计工具DSP Builder

一段时间以来,MathWorks一直主张使用Matlab和Simulink开发工具进行基于模型的设计,因为好的设计技术使您能够在更短的时间内开发更高质量的复杂软件。基于模块的设计采用了数学和可视化的方法,通过整个开发过程中使用的系统级建模(从初始设计到设计分析,仿真,自动代码生成、开发和验证)来开发复杂的控制和信号处理系统。这些模块是由框图,文本程序和其他图形元素组成的可执行规范。基于模型的设计鼓励对比其他设计方法更广泛的设计空间的快速探索,因为您可以在设计周期的早期更快地迭代设计。而且,由于这些模型是可执行的,所以验证成为每一步开发过程中不可或缺的一部分。

面向英特尔® FPGA 的 DSP Builder 是一款数字信号处理 (DSP) 设计工具,通过MathWorks* Simulink* 环境中,对英特尔 FPGA 的支持, 通过按下不同按钮生成 DSP 算法的 HDL 代码。该工具可使用 MATLAB 函数和 Simulink 模型生成可合成的优质 VHDL/Verilog 代码。生成的 RTL 代码可用于英特尔 FPGA 编程,广泛适用于雷达设计、无线和有线通信设计、医学成像和电机控制等应用。

该工具在现有的 Simulink 库中添加了额外的库块,其中包括面向英特尔 FPGA 的 DSP Builder 高级模块集和面向英特尔 FPGA 的 DSP Builder 标准模块集。建议使用面向英特尔 FPGA 的 DSP Builder高级模块集进行全新的设计。

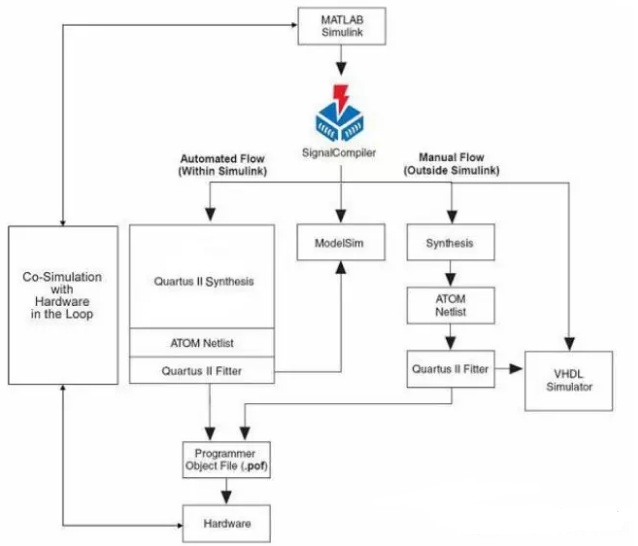

下图所示为Intel FPGA DSP Builder 系统级设计流程。

主要特性:

从高等级的示意图到针对英特尔 FPGA 优化的低等级 VHDL

使用矢量处理来执行高性能的定点和浮点 DSP,例如复杂的 IEEE 754 单精度浮点

将设计一键迁移到英特尔 Arria® 10 和英特尔 Stratix® 10 设备上的英特尔的硬浮点 DSP 模块。

通过 ALU 折叠从扁平的数据速率设计中构建定制的 ALU 处理器架构

高级合成优化,自动流水线插入和平衡,以及目标硬件映射

灵活的“白盒”快速傅立叶变换 (FFT) 工具包,具有开放的库和模块层次结构,可支持用户构建定制的 FFT

使用设计人员制定的系统时钟约束自动实现流水线、时分多路复用/分折和时序收敛

访问高级 math.h 函数和多通道数据

为所有设计生成资源利用率表,而无需使用英特尔 Quartus Prime 软件进行编译

自动为英特尔 Quartus Prime 软件、Timing Analyzer、Platform Designer(原 Qsys)以及 ModelSim-Intel FPGA 版本生成项目或脚本。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

关于INTEL FPGA设计工具DSP Builder的更多相关文章

- 基于INTEL FPGA硬浮点DSP实现卷积运算

概述 卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波.而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络.本参考设计主要介绍如何基于INTEL 硬浮点的DS ...

- 【转载】如何在FPGA设计环境中添加加时序约束

转自:http://bbs.ednchina.com/BLOG_ARTICLE_198929.HTM 如何在FPGA设计环境中加时序约束 在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序 ...

- OpenCL设计优化(基于Intel FPGA SDK for OpenCL)

1.首先了解Intel FPGA SDK for OpenCL实现OpenCL的设计组件,包括: kernels, global memory interconnect, local memory, ...

- DSP builder安装指南(以9.1为例) 转自http://www.cnblogs.com/sleepy/archive/2011/06/28/2092362.html

DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了DSP设计周期.已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及 ...

- FPGA设计思想与技巧(转载)

题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD来的,首先对整理者表示感谢.这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一 ...

- FPGA设计中的电源管理(转载)

过去,FPGA设计者主要关心时序和面积使用率问题.但随着FPGA不断取代ASSP和ASIC器件,设计者们现正期望能够开发低功耗设计,在设计流程早期就能对功耗进行正确估算,以及管理和对与FPGA相关的各 ...

- 每天进步一点点------ISE 12.4的FPGA设计基本流程

基于ISE 12.4的FPGA设计基本流程 ISE是使用XILINX的FPGA的必备的设计工具,它可以完成FPGA开发的全部流程,包括设计输入.仿真.综合.布局布线.生成BIT文件.配置以及在线调试等 ...

- Intel FPGA Clock Region概念以及用法

目录 Intel FPGA 的Clock Region概念 Intel 不同系列FPGA 的Clock Region 1. Clock Region Assignments in Intel Stra ...

- FPGA开发工具套餐搭配推荐及软件链接 (更新于2020.03.16)

一.Xilinx(全球FPGA市场份额最大的公司,其发展动态往往也代表着整个FPGA行业的动态) (1) Xilinx官方软件下载地址链接: https://china.xilinx.com/supp ...

随机推荐

- 024——VUE中filter的使用

<!DOCTYPE html> <html> <head> <meta charset="UTF-8"> <title> ...

- hdu4115

题解: 2-sat 对于bob出的每一张牌,alice显然只有两种选择 然后对于每一个限制,连边 判断是否可行 代码: #include<cstdio> #include<cmath ...

- kmplayer加速播放视频(转)

转自微博:http://blog.sina.com.cn/shaguazhu1213 KMPlayer控制播放速度的快捷方式 (2011-11-12 10:51:56) 标签: 杂谈 分类: 编程之旅 ...

- java中的一些执行顺序,代码块,静态,构造,成员。。。。(转的)

Java初始化顺序(转来的) 1在new B一个实例时首先要进行类的装载.(类只有在使用New调用创建的时候才会被java类装载器装入) 2,在装载类时,先装载父类A,再装载子类B3,装载父类A后,完 ...

- PHP错误Parse error: syntax error, unexpected end of file in test.php on line 12解决方法

出现这个错误的原因就是语法错误,肯定是PHP程序的书写不规范造成,PHP语句标识符错了,没有在php.ini中开启短标签!八成是这个原因,啊啊啊! 今天在写PHP程序的时候总是出现这样的错误:Pars ...

- 每周荐书:Kotlin、分布式、Keras(评论送书)

每周荐书:Kotlin.分布式.Keras(评论送书) 感谢大家对每周荐书栏目的支持,先公布下上周中奖名单 法式三文鱼 名优秀评论可以免费获得此书. Kotlin实战 首著席卷而来 Android ...

- tensorflow windows

conda create -n py35 python=3.5 activate py35 pip install --ignore-installed --upgrade https://stora ...

- [Python] dict字典的浅复制与深复制

Python中针对dict字典有两种复制: (1)浅复制:利用 copy() 或者 dict() :复制后对原dict的内部子对象(方括号[]内元素)进行操作时,由浅复制得到的dict会受该操作影响 ...

- java android 读写三菱PLC 使用TCP/IP 协议

本文将使用一个Github开源的组件库技术来读写三菱PLC和西门子plc数据,使用的是基于以太网的TCP/IP实现,不需要额外的组件,读取操作只要放到后台线程就不会卡死线程,本组件支持超级方便的高性能 ...

- 第23课 #error和#line使用分析

#error的用法: 示例程序: #include <stdio.h> #ifndef __cplusplus #error This file should be processed w ...