协议——VGA

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。不支持热插拔,不支持音频传输。对于一些嵌入式VGA显示系统,可以在不使用VGA显示卡和计算机的情况下,实现VGA图像的显示和控制。VGA显示器具有成本低、结构简单、应用灵活的优点。对于一名FPGA工程师,尤其是视频图像的方向的学习者,VGA协议是必须要掌握的。

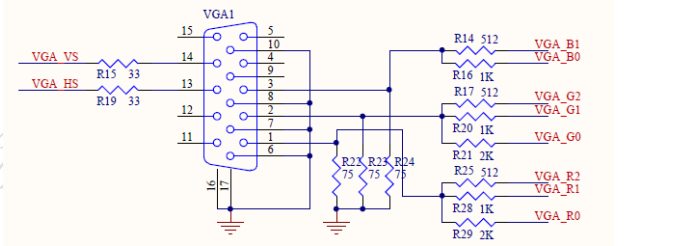

一、外部接口

由电路图可以看到,VGA并没有特殊的外部芯片,我们需要关注的其实只有5个信号:HS行同步信号,VS场同步信号,R红基色,G绿基色,B蓝基色。下面慢慢解释这些信号。

二、色彩原理

经过九年义务教育的我们都应该听过三基色,还给老师了的那就在再复习一下。三基色是指通过其他颜色的混合无法得到的“基本色”由于人的肉眼有感知红、绿、蓝三种不同颜色的锥体细胞,因此色彩空间通常可以由三种基本色来表达。这是色度学的最基本原理,即三基色原理。三种基色是相互独立的,任何一种基色都不能有其它两种颜色合成。红绿蓝是三基色,这三种颜色合成的颜色范围最为广泛。我们的RGB信号真是三基色的运用,对这三个信号赋予不同的数值,混合起来便是不同的色彩。

设计RGB信号时,既可以R信号、G信号和B信号独立的赋值,最后连到端口上,也可以直接用RGB当做一个整体信号,RGB信号在使用时的位宽有三种常见格式,以你的VGA解码芯片的配置有关。

1. RGB_8,R:G:B = 3:3:2,即RGB332

2. RGB_16,R:G:B = 5:6:5,即RGB565

3. RGB_24,R:G:B = 8:8:8,即RGB888

三、扫描方式

VGA显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。因此我们一般都采用逐行扫描的方式。

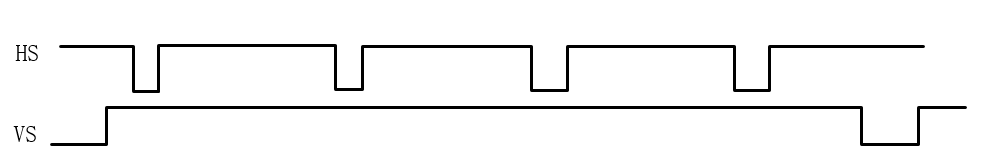

扫描原理如下所示:

四、行场信号

一开始看这个时序图可能看不懂,它是把行场信号绘制在同一张图里,说明行场信号的控制是相似的,只是时间参数不一样而已。如果展开的话,其实时序是这样的:

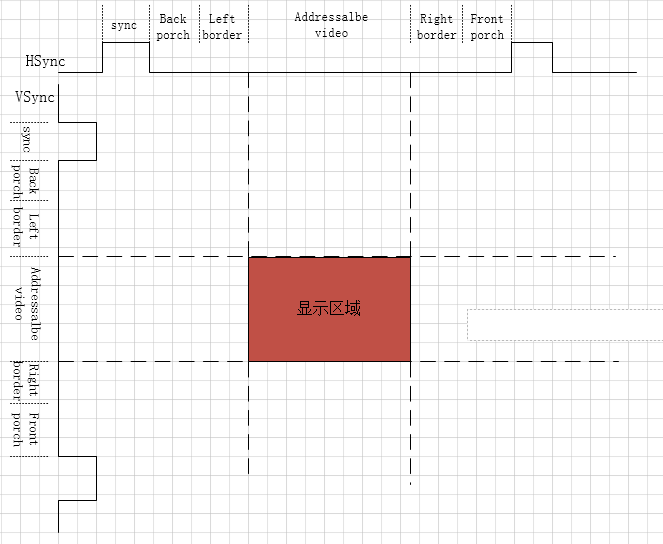

这样就清楚了,大致是若干个HS信号才组合而成一个VS,如果在一副图片中,那正确的时序表示方式应该如下图这样。

现在稍稍解释一下这些参数。SYNC是“信号同步”,Back proch和Left border常常加在一起称为“显示后沿”,Addressable video为“显示区域”,Right porder和Front porch常常加在一起称为“显示前沿”,一个时序其实就是先拉高一段较短的“信号同步”时间,然后拉低一段很长的时间,这就是一个回合。同时需要注意,其实也可以完全相反。即先拉低一段时间“信号同步”时间,然后拉高一段很长的时间。

具体这些时间参数是怎么来的呢?且看下文。

五、规格参数

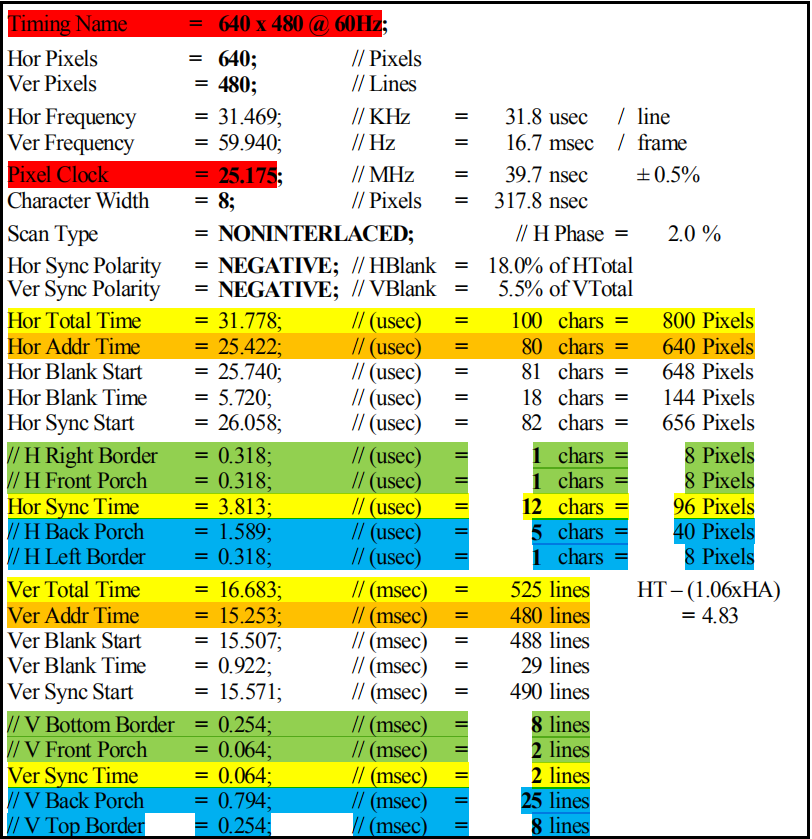

直接拿数据手册说话!

以上是 640x480 @60Hz 的规格参数表,对着这个表即可确定时间。如果为了嫌麻烦,也可以先计算好写在代码里。

//**************************************************************************

// *** 名称 : VGA_driver.v

// *** 作者 : xianyu_FPGA

// *** 博客 : https://www.cnblogs.com/xianyufpga/

// *** 日期 : 2019-06-26

// *** 描述 : VGA驱动模块,pixel_req和pixel_x、pixel_y信号一般不同时使用

//************************************************************************** module VGA_driver

//========================< 端口 >==========================================

(

//system ----------------------------------------

input wire clk , //时钟,25Mhz

input wire rst_n , //复位,低电平有效

//vga_display -----------------------------------

input wire [:] pixel_data , //得到图像数据

output wire pixel_req , //请求图像数据

output wire [ :] pixel_x , //请求显示区域横坐标

output wire [ :] pixel_y , //请求显示区域纵坐标

//vga output ------------------------------------

output reg vga_de , //VGA接口使能

output wire vga_hsync , //VGA接口行信号

output wire vga_vsync , //VGA接口场信号

output wire [:] vga_data //VGA接口rgb数据信号

);

//========================< 参数 >==========================================

//640x480 @60Hz 25Mhz -----------------------------------------

parameter H_TOTAL = ; //行扫描周期

parameter H_ADDR = ; //行有效数据

parameter H_RIGHT_BORDER = ;

parameter H_FRONT_PORCH = ;

parameter H_FRONT = H_RIGHT_BORDER + H_FRONT_PORCH ; //行显示前沿

parameter H_SYNC = ; //行同步

parameter H_BACK_PORCH = ;

parameter H_LEFT_BORDER = ;

parameter H_BACK = H_BACK_PORCH + H_LEFT_BORDER ; //行显示后沿

//-------------------------------------------------------------

parameter V_TOTAL = ; //场扫描周期

parameter V_ADDR = ; //场有效数据

parameter V_BOTTOM_BORDER = ;

parameter V_FRONT_PORCH = ;

parameter V_FRONT = V_BOTTOM_BORDER + V_FRONT_PORCH ; //场显示前沿

parameter V_SYNC = ; //场同步

parameter V_BACK_PORCH = ;

parameter V_TOP_BORDER = ;

parameter V_BACK = V_BACK_PORCH + V_TOP_BORDER ; //场显示后沿

//========================< 信号 >==========================================

reg [ :] cnt_h ;

wire add_cnt_h ;

wire end_cnt_h ;

reg [ :] cnt_v ;

wire add_cnt_v ;

wire end_cnt_v ;

//==========================================================================

//== 行、场计数

//==========================================================================

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_h <= ;

else if(add_cnt_h) begin

if(end_cnt_h)

cnt_h <= ;

else

cnt_h <= cnt_h + ;

end

end assign add_cnt_h = ;

assign end_cnt_h = add_cnt_h && cnt_h==H_TOTAL-; always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_v <= ;

else if(add_cnt_v) begin

if(end_cnt_v)

cnt_v <= ;

else

cnt_v <= cnt_v + ;

end

end assign add_cnt_v = end_cnt_h;

assign end_cnt_v = add_cnt_v && cnt_v==V_TOTAL-;

//==========================================================================

//== VGA display

//==========================================================================

//vga请求

assign pixel_req = (cnt_h >= H_SYNC + H_BACK - ) && (cnt_h < H_SYNC + H_BACK + H_ADDR - ) &&

(cnt_v >= V_SYNC + V_BACK ) && (cnt_v < V_SYNC + V_BACK + V_ADDR )

? : ;

//vga坐标

assign pixel_x = pixel_req ? (cnt_h - (H_SYNC + H_BACK - 'b1)) : 10'd0;

assign pixel_y = pixel_req ? (cnt_v - (V_SYNC + V_BACK - 'b1)) : 10'd0;

//==========================================================================

//== VGA output

//==========================================================================

always @(posedge clk) begin

vga_de <= pixel_req;

end assign vga_hsync = (cnt_h < H_SYNC) ? : ;

assign vga_vsync = (cnt_v < V_SYNC) ? : ; assign vga_data = vga_de ? pixel_data : 'b0; endmodule

六、实例讲解

最近使用的开发板带了一个TFT屏,分辨率为480x272,其显示原理和VGA接口完全相同,因此拿这个屏幕编写一段程序看看。

//==========================================================================

// --- 名称 : TFT_driver.v

// --- 作者 : xianyu_FPGA

// --- 日期 : 2019-01-03

// --- 描述 : TFT显示屏控制器,分辨率480x272,显示三个竖着的彩条

//========================================================================== module TFT_driver

//=====================<端口声明>===========================================

(

//input -------------------------------------

input wire clk , //时钟,9Mhz

input wire rst_n , //复位,低电平有效

//user interfaces ---------------------------

output wire TFT_req , //输出请求信号

input wire [:] data , //得到图像数据

//output ------------------------------------

output wire TFT_clk , //TFT像素时钟

output wire TFT_de , //TFT使能

output wire TFT_pwm , //TFT背光控制

output wire TFT_hsync , //TFT行同步信号

output wire TFT_vsync , //TFT场同步信号

output reg [:] TFT_rgb //TFT像素输出

);

//=====================<参数定义>===========================================

//480x272 @60 9Mhz --------------------------

parameter H_TOTAL = ; //行扫描周期

parameter H_ADDR = ; //行有效数据

parameter H_FRONT = ; //行显示前沿

parameter H_SYNC = ; //行同步

parameter H_BACK = ; //行显示后沿

parameter V_TOTAL = ; //场扫描周期

parameter V_ADDR = ; //场有效数据

parameter V_FRONT = ; //场显示前沿

parameter V_SYNC = ; //场同步

parameter V_BACK = ; //场显示后沿 //=====================<信号定义>===========================================

//行场信号

reg [:] cnt_h ;

wire add_cnt_h ;

wire end_cnt_h ;

reg [:] cnt_v ;

wire add_cnt_v ;

wire end_cnt_v ;

reg TFT_en ;

wire red_area ;

wire green_area ;

wire blue_area ; //--------------------------------------------------------------------------

//-- 行、场计数

//--------------------------------------------------------------------------

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_h <= ;

else if(add_cnt_h) begin

if(end_cnt_h)

cnt_h <= ;

else

cnt_h <= cnt_h + ;

end

end assign add_cnt_h = ;

assign end_cnt_h = add_cnt_h && cnt_h==H_TOTAL-; always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_v <= ;

else if(add_cnt_v) begin

if(end_cnt_v)

cnt_v <= ;

else

cnt_v <= cnt_v + ;

end

end assign add_cnt_v = end_cnt_h;

assign end_cnt_v = add_cnt_v && cnt_v==V_TOTAL-; //--------------------------------------------------------------------------

//-- TFT请求信号和使能信号,注意时序的对齐

//--------------------------------------------------------------------------

assign TFT_req = (cnt_h >= H_SYNC + H_BACK - ) && (cnt_h < H_SYNC + H_BACK + H_ADDR - ) &&

(cnt_v >= V_SYNC + V_BACK ) && (cnt_v < V_SYNC + V_BACK + V_ADDR )

? : ; always @(posedge clk) begin

TFT_en <= TFT_req;

end //--------------------------------------------------------------------------

//-- 行场信号

//--------------------------------------------------------------------------

assign TFT_hsync = (cnt_h < H_SYNC) ? : ;

assign TFT_vsync = (cnt_v < V_SYNC) ? : ; //--------------------------------------------------------------------------

//-- 其他信号

//--------------------------------------------------------------------------

assign TFT_clk = clk;

assign TFT_de = TFT_en;

assign TFT_pwm = rst_n; //--------------------------------------------------------------------------

//-- rgb信号

//--------------------------------------------------------------------------

//assign TFT_rgb = TFT_en ? data : 0; always @(*) begin

if(TFT_en) begin if(red_area) begin //红色区域

TFT_rgb <= 'b11111_000000_00000;

end

else if(green_area) begin //绿色区域

TFT_rgb <= 'b00000_111111_00000;

end

else if(blue_area) begin //蓝色区域

TFT_rgb <= 'b00000_000000_11111;

end end

else begin //非显示区域

TFT_rgb <= ;

end

end assign red_area = cnt_h >= (H_SYNC + H_BACK) && cnt_h < (H_SYNC + H_BACK + H_ADDR*/) &&

cnt_v >= (V_SYNC + V_BACK) && cnt_v < (V_SYNC + V_BACK + V_ADDR);

assign green_area = cnt_h >= (H_SYNC + H_BACK) && cnt_h < (H_SYNC + H_BACK + H_ADDR*/) &&

cnt_v >= (V_SYNC + V_BACK) && cnt_v < (V_SYNC + V_BACK + V_ADDR);

assign blue_area = cnt_h >= (H_SYNC + H_BACK) && cnt_h < (H_SYNC + H_BACK + H_ADDR*/) &&

cnt_v >= (V_SYNC + V_BACK) && cnt_v < (V_SYNC + V_BACK + V_ADDR); endmodule

这个工程还包括顶层top模块,pll分频模块,这些就不展示了。还一点是接口处的user interfaces的信号没有使用到,而是自己通过代码赋的值。工程最终正常运行,显示出从左到右的三个竖彩条,其效果如下所示:

七、后记

这样只是简单的使用了VGA,最终还是要以显示视频或图像为目标,这就涉及到模块之间的交互问题,下次再总结吧!

参考资料:

[1]开源骚客.VGA系列之一:VGA显示驱动篇

[2]NingHeChuan.基于FPGA的VGA显示静态图片

[3]威三学院FPGA教程

[4]袁玉卓, 曾凯锋, 梅雪松. FPGA自学笔记:设计与验证[M]. 北京航空航天出版社, 2017.

协议——VGA的更多相关文章

- Verilog HDL那些事_建模篇笔记(实验九:VGA驱动)

1.了解VGA协议 VGA协议有5个输入信号,列同步信号(HSYNC Signal),行同步信号(VSYNC Signal),红-绿-蓝,颜色信号(RGB Signal). 一帧屏幕的显示是由行从上至 ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- 高清VGA编码器|上海视涛科技

VGA编码器(E200)简介 高清VGA编码器是上海视涛科技出品的高性能VGA编码产品.该VGA编码器是上海视涛科技完全自主研发,并适用于VGA信号的编码采集及网络传输的专用硬件设备.可兼容各厂家的N ...

- VGA DVI HDMI区别

VGA,DVI,HDMI是目前常用的3种不同显示接口的名称.在树莓派的边缘既有HDMI的接口,也有RCA的接口,而显示器上也是既有DVI,又有VGA.上个月买连接线,没有仔细检查买了一根HDMI对VG ...

- HDMI接口与协议

深入了解HDMI接口 一.HDMI接口的工作原理这张图是HDMI接口的架构示意图.从左边的信号源中你可以看到,HDMI接口的信源可以是任何支持HDMI输出的设备,而接入端也可以是任何带有HDMI输 入 ...

- 屏幕分辨率(QQVGA、QVGA、VGA、XGA、WXGA、WUXGA和WSXGA+)

TFT屏幕 TFT ( Thin Film Transistor 薄膜晶体管) ,是有源矩阵类型液晶显示器(AM-LCD)中的一种,TFT在液晶的背部设置特殊光管,能够“主动的”对屏幕上的各个独立的象 ...

- 单色VGA显示verilogHDL通用代码

今天做VGA,真是拼凑了好久啊.唉,总算完成了. 本来想偷懒移植,最后还是自己写的代码. //2015/12/13 //designer : pengxiaoen //function : vga c ...

- VGA、DVI、HDMI、DP 接口介绍及优劣

VGA.DVI.HDMI.DP 接口介绍及优劣 随着日新月异的发展,就目前显卡上面常见的输出接口而言,我们所熟知的有以下几种: VGA.DVI.HDMI和DP (DisplayPort). 这四种 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

随机推荐

- 移动端touch触摸事件(滑动效果和手势操作)

一.定义 ①touch是移动端的触摸事件,而且是一组事件,主要有以下事件: touchstart 事件:当手指触摸屏幕的时候触发 touchmove 事件:当手指在屏幕来回滑动的时候触发 touche ...

- 使用jstack命令查看CPU高占用的问题记录

笔记: 1.top命令找出最高占用的进程(command为java) 2.查看高负载进程下的高负载线程:top -Hp [PID] (或 ps -mp PID -o THREAD,tid,time) ...

- 计蒜客 39279.Swap-打表找规律 (The 2019 ACM-ICPC China Shannxi Provincial Programming Contest L.) 2019ICPC西安邀请赛现场赛重现赛

Swap There is a sequence of numbers of length nn, and each number in the sequence is different. Ther ...

- 微信小程序组件化开发框架WePY

wepy-CLI 安装 npm install -g wepy-cli wepy init standard my-project https://github.com/Tencent/wepy 特性 ...

- 运行OpenGL红宝书第9版源码时Visual Studio提示“无法启动程序...ALL_BUILD。拒绝访问“的问题的解决办法

问题描述: OpenGL红宝书第9版源码采用CMake编译后,用相应的Visual Studio(如VS2012)打开“vermilion9.sln”解决方案,并运行时Visual Studio提示“ ...

- 关于qemu的二三事(1)————qemu的特殊参数之monitor

qemu作为一个十分重要的虚拟化工具,提供了丰富的功能/参数来支持虚拟化的各种操作. 下面仅就monitor这个参数或者说是功能来结合自己的实际体验来做个简要介绍. 如何进入qemu的monitor模 ...

- python笔记之按文件名搜索指定路径下的文件

1.搜索文件名中以指定的字符串开头(如搜索dll,结果中含有dll a,dll abc等) 我的目录下有dll a.txt和dll.txt文件 其中a文件夹下还有这两个文件 我希望通过python选择 ...

- Mac下的IDEA快捷键

快捷键 功能 Option + enter 打开提示 Command + / 注释方式是“行注释”:可以注释当前行.取消当前行的注释 注释选中的内容.取消选中行的注释 Option + Command ...

- 【Java】Swagger快速入门

Swagger 简介 Swagger 是一套基于 OpenAPI 规范构建的开源工具,可以帮助我们设计.构建.记录以及使用 Rest API.Swagger 主要包含了以下三个部分: Swagger ...

- 413(Request Entity Too Large)

场景,在现金速达后台上传图片的时候,fetch请求报错,图片虽然不大,只有几百kb但是需要转成bese64传给后台, 413(Request Entity Too Large) 一开始以为是fetch ...