(原创)defparam的应用(Verilog,CPLD/FPGA)

1.Abstract

在同一个模块被多次例化的时候,改变参数构建不同的硬件实体是一个很好的选择。特别是今天帮一个朋友调试一个比较复杂的逻辑,深有体会。这个也是一个小技巧,回来也查了许多资料,强化了一下这方面的知识。前几天也做了一个这样的例子,可以拿过来作为验证一下。

2.Content

2.1 语法说明

defparam 的语法说明如下:

defparam ParameterName = Constant Expression,

ParameterName = ConstantExpression;

使用范围:module < Valid Place > endmodule

综合问题:一般情况下是不可综合的。

2.2 使用说明

跟其他的赋值语句是一样的,这里值得说明一下的是 ParameterName 这个表达式。直接在本模块中的参数,直接写名字就可以了,前提是这个名字已经存在。例如:最开始想用12小时制来表示 paramter TIME = 12; 某个情况下,需要改成24小时制,可以用 defparam TIME = 24; 实现。改变已经例化后的模块中的参数,就得需要明确写出了,用英文小数点(.)表示层次逻辑关系。比如,在M0子模块中有一个TIME参数,预先在设计之前是使用的是12小时制,现在想在主模块中将它更改至24小时制,就可以用 defparam M0.TIME = 24; 就可以了。最后值得注明的一点是 默认是使用的无符号整数型,某些场合需要对它进行位宽限制,以避免因位宽导致的问题(不过,这样的问题在编译的时候,编译器会友善的给出警告提示)。

2.3 实际验证

一种较好的测试方法就是先用原理图编辑好文件,然后让系统自动地将原理图文件转换成为Verilog文件,通过对比最后的生成结果来对比就很容易理解了。

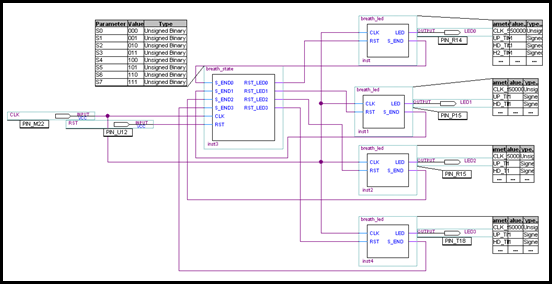

拿以前的那个超级流水灯作为测试(http://www.cnblogs.com/hechengfei/p/4115087.html)。将所有的文件都生成各自对应的符号文件,然后再在顶层block块将各个模块手工的连接起来,修改每个子呼吸灯的下降时间DN_TIME参,使它们不相同,以便在后边的文件生成测试。

FIG2.1 顶层block块

FIG2.1 顶层block块

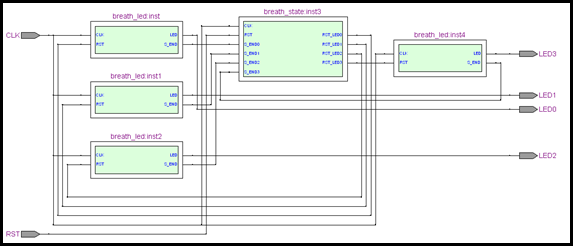

编译通过以后,用RTL视图看看计算机的连线是否和预期的一样。

FIG2.2 综合后的RTL视图

FIG2.2 综合后的RTL视图

可以知道,这个是和预期的相同,只是最后的输出引脚不是总线方式罢了,这个原因是因为在原理图中没有将它作为一个总线看待,功能是和原来的一样。当然,为了更加可靠一些,我把最后的文件烧录在FPGA板中,观察实际的现象。

最后就是将这个原理图文件转换成Verilog文件。看看软件将这些参数是怎样与模块设置的参数一一对应的。

// Copyright (C) 1991-2009 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details. // PROGRAM "Quartus II"

// VERSION "Version 9.1 Build 222 10/21/2009 SJ Full Version"

// CREATED "Sun Nov 23 15:07:47 2014" module breath(

CLK,

RST,

LED3,

LED2,

LED1,

LED0

); input CLK;

input RST;

output LED3;

output LED2;

output LED1;

output LED0; wire SYNTHESIZED_WIRE_0;

wire SYNTHESIZED_WIRE_1;

wire SYNTHESIZED_WIRE_2;

wire SYNTHESIZED_WIRE_3;

wire SYNTHESIZED_WIRE_4;

wire SYNTHESIZED_WIRE_5;

wire SYNTHESIZED_WIRE_6;

wire SYNTHESIZED_WIRE_7; breath_led b2v_inst(

.CLK(CLK),

.RST(SYNTHESIZED_WIRE_0),

.LED(LED0),

.S_END(SYNTHESIZED_WIRE_3));

defparam b2v_inst.CLK_50M = 50000000;

defparam b2v_inst.DN_TIME = 1;

defparam b2v_inst.H2_TIME = 1;

defparam b2v_inst.HD_TIME = 1;

defparam b2v_inst.S0 = 2'b00;

defparam b2v_inst.S1 = 2'b01;

defparam b2v_inst.S2 = 2'b10;

defparam b2v_inst.S3 = 2'b11;

defparam b2v_inst.UP_TIME = 1; breath_led b2v_inst1(

.CLK(CLK),

.RST(SYNTHESIZED_WIRE_1),

.LED(LED1),

.S_END(SYNTHESIZED_WIRE_4));

defparam b2v_inst1.CLK_50M = 50000000;

defparam b2v_inst1.DN_TIME = 2;

defparam b2v_inst1.H2_TIME = 1;

defparam b2v_inst1.HD_TIME = 1;

defparam b2v_inst1.S0 = 2'b00;

defparam b2v_inst1.S1 = 2'b01;

defparam b2v_inst1.S2 = 2'b10;

defparam b2v_inst1.S3 = 2'b11;

defparam b2v_inst1.UP_TIME = 1; breath_led b2v_inst2(

.CLK(CLK),

.RST(SYNTHESIZED_WIRE_2),

.LED(LED2),

.S_END(SYNTHESIZED_WIRE_5));

defparam b2v_inst2.CLK_50M = 50000000;

defparam b2v_inst2.DN_TIME = 3;

defparam b2v_inst2.H2_TIME = 1;

defparam b2v_inst2.HD_TIME = 1;

defparam b2v_inst2.S0 = 2'b00;

defparam b2v_inst2.S1 = 2'b01;

defparam b2v_inst2.S2 = 2'b10;

defparam b2v_inst2.S3 = 2'b11;

defparam b2v_inst2.UP_TIME = 1; breath_state b2v_inst3(

.S_END0(SYNTHESIZED_WIRE_3),

.S_END1(SYNTHESIZED_WIRE_4),

.S_END2(SYNTHESIZED_WIRE_5),

.S_END3(SYNTHESIZED_WIRE_6),

.CLK(CLK),

.RST(RST),

.RST_LED0(SYNTHESIZED_WIRE_0),

.RST_LED1(SYNTHESIZED_WIRE_1),

.RST_LED2(SYNTHESIZED_WIRE_2),

.RST_LED3(SYNTHESIZED_WIRE_7));

defparam b2v_inst3.S0 = 3'b000;

defparam b2v_inst3.S1 = 3'b001;

defparam b2v_inst3.S2 = 3'b010;

defparam b2v_inst3.S3 = 3'b011;

defparam b2v_inst3.S4 = 3'b100;

defparam b2v_inst3.S5 = 3'b101;

defparam b2v_inst3.S6 = 3'b110;

defparam b2v_inst3.S7 = 3'b111; breath_led b2v_inst4(

.CLK(CLK),

.RST(SYNTHESIZED_WIRE_7),

.LED(LED3),

.S_END(SYNTHESIZED_WIRE_6));

defparam b2v_inst4.CLK_50M = 50000000;

defparam b2v_inst4.DN_TIME = 4;

defparam b2v_inst4.H2_TIME = 1;

defparam b2v_inst4.HD_TIME = 1;

defparam b2v_inst4.S0 = 2'b00;

defparam b2v_inst4.S1 = 2'b01;

defparam b2v_inst4.S2 = 2'b10;

defparam b2v_inst4.S3 = 2'b11;

defparam b2v_inst4.UP_TIME = 1; endmodule

可以看出,除去defparam的语句部分,其他的就跟原来的差不多了。可以得出的结论是原理图的参数设置就是通过defparam语句对应的。

这样,在以后遇到需要改变参数的文件,就可以考虑使用 defparam 了。补充一点的就是为了使逻辑更加的通用,将电路的一些参数进行仔细分析,然后将那些可变的参数提取出来,用 paramter 的方式声明一下,然后使用。

3.Conclusion

defparam 对一些需要电路相同,而参数不尽相同的逻辑设计很有帮助,将它作为一个小知识点掌握和累积起来。

4.Reference

[1] Verilog 数字系统设计教程(第二版) 夏宇闻

5.Platform

1). Quartus II Version 9.1 Build 222

(原创)defparam的应用(Verilog,CPLD/FPGA)的更多相关文章

- CPLD/FPGA厂商概述 .

随着可编程逻辑器件应用的日益广泛,许多IC制造厂家涉足PLD/FPGA领域.目前世界上有十几家生产CPLD/FPGA的公司,最大的三家是:ALTERA,XILINX,Lattice,其中ALTERA和 ...

- cpld fpga 区别

cpld fpga 区别 系统的比较,与大家共享: 尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种算法和 ...

- (原创)用Verilog实现一个参数化的呼吸灯(Verilog,CPLD/FPGA)

1.Abstract 观察到一个有趣的现象,每当把Apple笔记本合上的时候,那个白色的呼吸灯就会反复地由暗渐明,然后又由明渐暗,乍一看就像Apple笔记本在打盹休息一样,十分可爱!于是突发奇 ...

- (原创)基于FPGA的调光流水灯(Verilog,CPLD/FPGA)

1.Abstract 前几天做了一个呼吸灯,觉得确实挺有意思的:可惜的是只有一个灯管亮,板子上有四个灯,要是能让这些灯有序地亮起来,那应该更有趣味了!跟传统的一样,逻辑上做成一个流水灯的样式, ...

- (原创)task和function语法的使用讨论(Verilog,CPLD/FPGA)

1. Abstract function和task语句的功能有很多的相似之处,在需要有多个相同的电路生成时,可以考虑使用它们来实现.因为个人使用它们比较少,所以对它们没有进行更深的了解,现在时间比较充 ...

- 基于verilog的FPGA编程经验总结(XILINX ISE工具)

1.用ISE仿真的时候.所用变量一定要初始化. ISE默认初始量为"XXXXX", 而Quarters是默认为"00000"的, 其实实际上, 下到FPGA里后 ...

- [原创]免固件开发USB2.0 FPGA方案 速度40Mbyte/s+

USB 2.0接口,实测速度40Mbyte/s: 一个接口实现两种功能(USB2.0+FPGA配置): 免固件开发: 完整的FPGA代码,即拿即用: FPGA逻辑工程师开发USB接口福音: 平台可移植 ...

- 【黑金ZYNQ7000系列原创视频教程】06.ZYNQ来自FPGA的中断——按键中断实验

黑金论坛地址: http://www.heijin.org/forum.php?mod=viewthread&tid=36640&extra=page%3D1 爱奇艺地址: http: ...

- 三段式状态机 [CPLD/FPGA]

状态机的组成其实比较简单,要素大致有三个:输入,输出,还有状态. 状态机描述时关键是要描述清楚前面提高的几个状态机的要素,即如何进行状态转移:每个状态的输出是什么:状态转移是否和输入条件相关等. 有人 ...

随机推荐

- VM 虚拟机 Error 1324. The path My Documents contains a invalid chara 。

当安装VM(虚拟机)时,安装到一半时,提示:Error 1324. The path My Documents contains a invalid chara . 就是提示路径无效. 按下面的路径: ...

- Egret Wing3 FTP使用方法

FTP 挺实用的,不用自己去申请sinasea什么的免费空间来测试项目了. 添加FTP服务器配置 默认就行. 指定目录上传至FTP服务器 选择免费云测试空间.然后选择bin-release/web目录 ...

- Xshell

http://baike.baidu.com/link?url=5lc5IxVVauitYSbqlOXJBvrvM3qVfMhzz6x_xu2cOMb108Ln9Wk7iJ3f46vG0kBninKw ...

- <img>标签

<img src="w3school.jpg" width="104" height="142" />注释:图像的名称和尺寸是以 ...

- Gradle basic

1. execute default file (build.gradle) gradlew 2. execute another file gradlew -b [filename] 3. bas ...

- NSPredicate谓词

NSPredicate——谓词(is) 作用:判断条件表达式的求值返回真或假的过程 使用步骤: . 定义NSPredicate对象并指定条件 . 调用谓词的evaluateWithObject方法判断 ...

- iOS7.0适配问题

self.navigationController.navigationBar.translucent = YES,导航栏透明 extendedLayoutIncludesOpaqueBars = Y ...

- NGUI 使用UITable(或UIGrid)注意事项

在ScrollView显示区域中,若Item数量不足以超出显示区域,有可能不是贴着ScrollView最边缘位置显示!这个时候可以按如下方法调整: 因为实际情况中,往ScrollView中添加Item ...

- 使用Servlet实现图片下载

package chensi.com; import java.io.FileInputStream; import java.io.IOException; import java.net.URLE ...

- WKWebView与Js (OC版)

OC如何给JS注入对象及JS如何给IOS发送数据 JS调用alert.confirm.prompt时,不采用JS原生提示,而是使用iOS原生来实现 如何监听web内容加载进度.是否加载完成 如何处理去 ...