lower power的IP设计

在IP的实现过程中,考虑lower power部分进行设计:

1)Partition the design来满足lower power的一些strategies,尤其是power gating和clock gating。

2)为power gating增加额外的逻辑。

3)设计clock和reset的strategy来配合lower power设计。

lower power memory可能需要好多mode:normal operating mode,retention mode,power off。

其中retention mode工作在一个低电压下,retain data。

针对power gating,在IP设计中需要注意:

1)区分power gating和power always on的block。

2)设计power controller控制power up和power down的sequence。(一般在IP外的一个aon模块中)

3)区分signal需要做isolate处理。

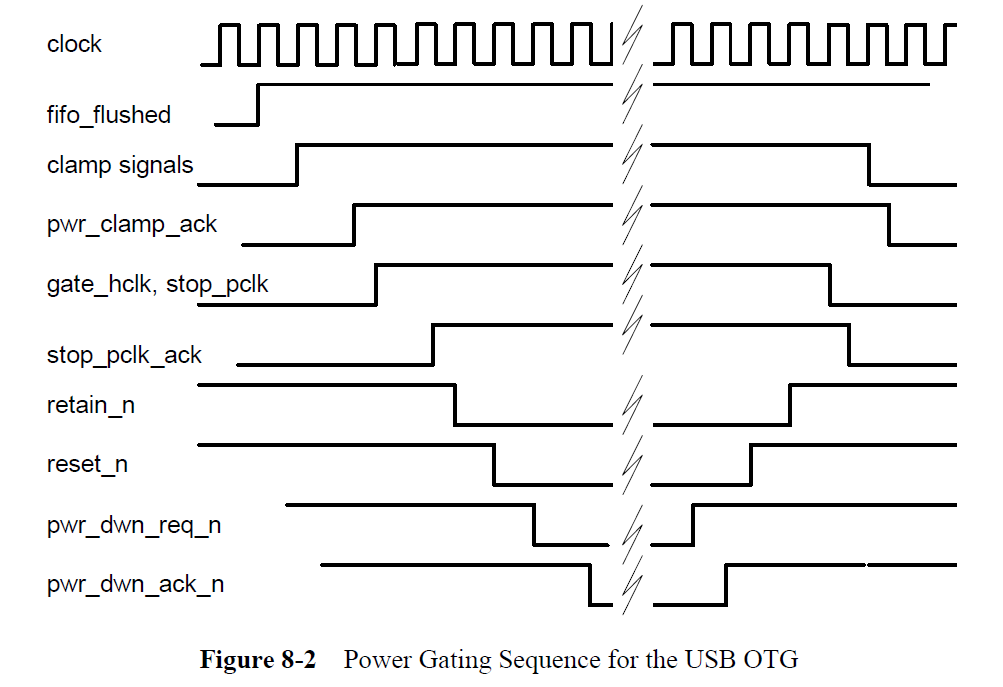

一般的power down和power up的sequence操作:

1)判断transaction和fifo都已为空。

2)停止clock。

3)针对isolate信号,进行clamp操作。

4)进retention操作。

5)复位IP。

6)关掉power。

上电过程中,会在clock之前进行一个rst,在经过clock的sync之后,才会被撤销。 异步复位的rst端口是电平触发,可以保证rst的成功。

但是仿真器中的X->0行为不确定。 掉电区域的clock,必须有一个clock的eb信号默认为有效,这样在上电后,可以保证有clock。

但是clock的频率需要再用该clock或者其他有电的clock进行配置。

rst的sync,只在存在cdc issue的问题上才会做。 同一个clock group上的clock,不需要做sync,不存在相位差。

上电过程中很多其他的clock的enable信号也必须是默认有效的,或者bus上的clock的enable信号默认有效。

1)从pmu过来的rst会进行同步; 2)Bus相关的rst会由bus的clock来同步; 3)Module相关的rst会由自己的clock来同步;

在rtl的simulation过程中,在power down之后,force register的输出为X,来进行仿真。

在gate-simulation过程中,可以建立一个switching fabric的model来进行仿真,还可以得到power up/down时间。

一个power gating的IP的框图,其中的pwr_switch在综合后加入。

lower power的IP设计的更多相关文章

- Power Gating的设计(模块二)

针对lower power的验证,由cpf/upf来建模,包括: 1)power gating的功能模型(在power gate之后将output force为x) 2)isolation功能模型: ...

- Lower Power with CPF(三)

常用的一些Lower Power的策略: 1)Clock tree optimization and clock gating:在正常情况下clock信号会一直toggle at the maximu ...

- Lower Power with CPF(二)

CPF文件可以有两种组织方式:Flat CPF file or Hierarchical CPF file. 由于在大型的SoC设计中,一般都采用Hierarchical的形式,所以本文主要按这个方式 ...

- Power Gating的设计(概述)

Leakage power随着CMOS电路工艺进程,功耗越来越大. Power Domain的开关一般通过硬件中的timer和系统层次的功耗管理软件来进行控制,需要在一下几方面做trade-off: ...

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

本帖最后由 xinxincaijq 于 2013-1-9 10:27 编辑 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计 转自博客:http:// ...

- Lower Power with CPF(四)

CPF从Front-end到Back-end(RTL--GDSII)的整个流程: 1)Creating a CPF file:来在前端就建立lower power的规范. 2)检查CPF文件的正确性, ...

- lower power设计中的DVFS设计

Pswitch = Ceff * Vvdd^2*Fclk, Pshort-circuit = Isc * Vdd * Fclk, Pleakage = f(Vdd, Vth, W/L) 尽管对电压的s ...

- Power Gating的设计(架构)

switching network的层次: 一般选择flatted的形式,hierarchy的结构对voltage drop和performance delay有影响. Power network的结 ...

- Power Gating的设计(模块)

Switching Fabric的设计: 三种架构:P沟道的switch vdd(header switch),N沟道的switch vss(footer switch),两个switch. 但是如果 ...

随机推荐

- MyBatis3资料网址

官网: http://mybatis.github.io/mybatis-3/zh/index.html 资料: http://www.open-open.com/doc/list/112?o=d 整 ...

- Koala编译less

下载地址:http://koala-app.com/index-zh.html 用Koala可以用来编译less,软件也是简单明了,平时开着其他软件编辑less,只要打开Koala,勾选“自动编译”后 ...

- Magento PHP Extension "curl" must be loaded解决方法

我记得我第一次在xampp装magento的时候,进入后台时提示PHP Extension "curl" must be loaded 在网页上查了下原因和解决方法,发现是mage ...

- magento csv导入

- SqlServer2008R2 如何插入多条数据

列id 为自增列 insert into Websites2values('Google','https://www.google.cm/','USA',1),('淘宝','https://www.t ...

- Selenium2学习-028-WebUI自动化实战实例-026-获取页面元素值或者元素属性值

在自动化脚本编写过程中,经常需要获取页面元素的文本进行判断,以便对于不同的文本进行不同的处理.比如:很多的购物网站,加入购物车的按钮是有多个状态的(加入购物车.到货通知.暂不销售等),那么在实际的操作 ...

- http://blog.csdn.net/littlechang/article/details/8642149

http://blog.csdn.net/littlechang/article/details/8642149

- stasm+三角剖分

- php 远程下载木马

function dlfile($file_url, $save_to) { $content = file_get_contents($file_url); file_put_contents($s ...

- 随机数产生random

随机数产生推荐用random(),在产生随机数前要添加种子srandom((unsigned int)time(NULL)). SYNOPSIS #include <stdlib.h> l ...