【转载】FPGA算法设计随笔

FPGA设计算法依次需要完成MATLAB浮点仿真 MATLAB定点仿真 verilogHDL定点运算以及数据对比的流程。其中浮点到定点的转换尤为重要,需要在数据表示范围和精度之间做出权衡。另外掌握定点运算规则是硬件实现算法的前提。这篇博文介绍了在用FPGA设计实现算法中的一些基础知识,比较全面。

介绍

FPGA是纯粹的硬件设计,当进行算法设计时,Verilog综合后的就是硬件逻辑电路。因此,进行算法设计时,算法设计中需要表示的数字用到的小数、符号、无穷大、整数、浮点数等等对应硬件来说都是一串0和1组合的数字。因此,当FPGA工程师设计算法时,需要对这些数字转换。一般转换为定点数值表示方式,在FPGA中实现定点数运算。具体用多长的位数表示定点,以及定点小数点放在那里,都需要根据具体设计中数值大小、需要表示的精度来确定。

这里主要介绍一下算法设计的主要过程和知识点,主要阐述下设计过程和用到的知识。不做具体深入细化,主要目的是记录下自己的学习过程,为想本人一样的初学者指个道,有不妥之处见谅,本人也是菜鸟。

一.算法设计基本知识

数字的表示

知道数值的表示方式是最基本的要求。主要的数值表示方式有原码、反码、补码;定点数、浮点数(单精度和双精度)。注意这些表示方式需要的位数和不同位中的具体实际含义。

二.算法设计前进行浮点仿真

为啥要浮点仿真呢。因为浮点是表示精度很高。而且matlab中默认的运算是双精度浮点型(double),这样浮点仿真得到的结果是最精确的。在以后的定点仿真和Verilog代码设计中的每一步结果都是以浮点对应步骤结果为参照进行的。

浮点仿真一般在MATLAB和C语言中进行。

##2.1浮点数表示方法

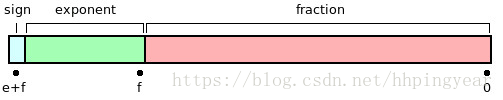

上面方框中表示的浮点数大小是:X=(-1)^sign * 1.fraction * 2^(exponent - bias)。

初学者这样看其实比较蒙圈,其实就是算术式X中sign和fraction直接由上图的fraction填充,1是固定的。Exponent转换为10进制放到X式子中。Bias在单精度表示法中是127,双精度中是1023。

对于32位单精度浮点数(float),sign是1位,exponent是8位(指数偏移量是127),fraction是23位。对于64位双精度浮点数(double),sign是1为,exponent是11位(指数偏移量是1023),fraction是52位。以32位单精度浮点数为例(float),其具体的转换规则是:首先把二进制小数(补码)用二进制科学计数法表示,比如上面给出的例子 1111101.001=1.111101001×26。符号位sign表示数的正负(0为正,1为负),故此处填0。exponent表示科学计数法的指数部分,请务必注意的是,这里所填的指数并不是前面算出来的实际指数,而是等于实际指数加上一个数(指数偏移),偏移量为2^(e-1)-1,其中e是exponent的宽度(位数)。对于32位单精度浮点数,exponent宽度为8,因此偏移量为127,所以exponent的值为133,即10000101。之后的fraction表示尾数,即科学计数法中的小数部分11110100100000000000000(共23位)。因此32位浮点数125.125D在计算机中就被表示为01000010111110100100000000000000。

2.2浮点仿真

最简便的浮点仿真是在MATLAB中进行,MATLAB默认数据是双精度,可以把需要计算的数据公式直接换成MATLAB程序,然后输入测试数据,观察输出的双精度结果用来指导下面的设计。

三.算法设计前进行定点仿真

在这一步骤需要将前面的MATLAB浮点仿真程序变换为MATLAB定点仿真程序。并逐步对照各个阶段的定点仿真结果,看偏差是多大。

3.1 定点表示

定点数:一种是规定小数点位置固定不变,称为定点数。

定点数的表示有Q、S两种方法。

Q格式

小数点位置不同,同一个二进制数可以表示不同的值。为了编程方便,我们通常在同一算法中使用固定的小数点位置。Q格式和S格式是用来表达一个二进制数中整数、小数分别有多少bit的一种表示格式。例如,我们用3bit表述整数部分,4bit表示小数部分,则这个数的格式为S3.4/Q4。

对于一个字长固定的处理器,另一种可行的表示格式是只表示小数部分。例如,当我们使用一个字长为16bit的处理器的时候,我们可以简单是说我们是使用Q15格式来表示小数。这里的Q15表示小数点右边有15bit,左边有1bit。同时Q15也等效于S1.15。

3.2定点数转换

假设存在浮点数x和定点数xq,则二者转化公式如下:

x转换为xq:xq = (int)x*2^Q;<下取整>

xq转换为x:x = (float)xq*2^(-Q)

Q表示从Q0-Q15之间的定标

举例: x = 0.5,Q = Q1,则xq = 0.5*2^1 = 1;

x = 0.5,Q = Q15,则xq = 16384。

假设xq = 100,Q=Q1,则x = 100*2^(-1) = 50.0;

xq = 512,Q = Q15,则x = 0.015625

3.3定点数运算的对标概念

定标的大小,影响着整数部分和小数部分的位数,定标的过程其实是在操作数动态范围和精度之间做权衡的过程。

设一个变量可能出现的最大绝对值为|max|,n为正整数,满足2^(n-1) < |max| < 2^n,则定标Q按如下规则选取最合适:

Q = 有效数据位 – n

对于32位的有符号数,数据有效位=31。如|max| = 2.75,选Q = 31 – 2 =29是最合适的。

两个定点数进行运算,它们的定标可能相同也可能不同,定标就是需要确定定点数加减乘除之前和之后的小数点位置。

我们知道,用十进制做两个数的加减和乘除过程如下:

加减法:先对位,后加减;

乘除法:先乘除,后取小数点。

而定点数之间的加减乘除,撇开符号位不谈,其过程是一样一样的:

加减法:先对标,后加减;

乘除法:先乘除,后定标。

3.2 MATLAB定点仿真

在这里,博文主要介绍一下MATLAB定点仿真用到的知识。MATLAB中有fixed-point-designer工具箱为设计者带来很大方便。大家可以阅读对应知识点。

https://ww2.mathworks.cn/products/fixed-point-designer.html

3.2.1 MATLAB浮点转定点函数—fi、quantizer函数

1、浮点数转换为定点数:

有两种方法:

(1)先量化再转化为二进制:a = 2.1345; b = quantizer([8 5]); c = num2bin(b, a);

(2)先确定定点数的格式再转换:a = 2.1345; b = numerictype(1,8,5); c = fi(a,b);用c.bin就可以查看c的二进制形式了。

2、 定点数(二进制)转化为浮点数(十进制):

先确定定点数的表示方式在用bin2num转换为十进制:d = quantizer([8 5]); e = bin2num(d,c),其中c为浮点转定点输出的数据。

3.2.2 整个程序的定点转换

通过上面的形式,将整个浮点下的算法转换为定点数对应的算法程序。并进行仿真验证。

四.讲定点仿真代码转换为Verilog语言

用Verilog实现定点运算是,需要做到小数点为在程序员心中。用Verilog语言实现加减乘除、对数、指数、开方、三角函数、双曲线函数运算等。

在这一节设计中,广大FPGA开发者可以参考下面网站很多很好的设计。

https://opencores.org/projects?lang=2&stage=0&license=0&wishbone_version=0

同时,MATLAB中有System Generator 2016.2工具和HLS(高层次综合可以直接将C语言转换为HDL语言),遗憾,这两个方法笔者也是初学。

五.对Verilog进行仿真

最后一步,就是对Verilog代码进行仿真。将前面定点MATLAB程序的定点数据输入到Verilog程序中,对应进行仿真,进行数据比对。

【转载】FPGA算法设计随笔的更多相关文章

- 基于FPGA的HDTV视频图像灰度直方图统计算法设计

随着HDTV的普及,以LCD-TV为主的高清数字电视逐渐进入蓬勃发展时期.与传统CRT电视不同的是,这些高清数字电视需要较复杂的视频处理电路来驱动,比如:模数转换(A/D Converter).去隔行 ...

- FPGA/CPLD设计思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

- 用GA算法设计22个地点之间最短旅程-R语言实现

数据挖掘入门与实战 公众号: datadw 相关帖子 转载︱案例 基于贪心算法的特征选择 用GA算法设计22个地点之间最短旅程-R语言实现 ----------------------------- ...

- FPGA基础设计(四):IIC协议

很多数字传感器.数字控制的芯片(DDS.串行ADC.串行DAC)都是通过IIC总线来和控制器通信的.不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kb ...

- OOP: One pont of view of OOP与基于算法设计的区别

..摘自<C++网络编程 卷1:运用ACE和模式消除复杂性> <C++ Network Programming Volume 1 Mastering Complexity with ...

- Python数据结构与算法设计总结篇

1.Python数据结构篇 数据结构篇主要是阅读[Problem Solving with Python]( http://interactivepython.org/courselib/static ...

- FPGA重要设计思想

FPGA重要设计思想 1.速度和面积互换原则.以面积换速度可以实现很高的数据吞吐率,其实串/并转换.就是一种以面积换速度的思想 2.乒乓操作. 3.串/并转换的思想. 高速数据处理的重要技巧之一. ...

- 算法设计和数据结构学习_5(BST&AVL&红黑树简单介绍)

前言: 节主要是给出BST,AVL和红黑树的C++代码,方便自己以后的查阅,其代码依旧是data structures and algorithm analysis in c++ (second ed ...

- Data Structure 之 算法设计策略

1. 穷举法 基本思想:列举问题的所有可能解,并用约束条件逐一进行判定,找出符合约束条件的解. 穷举法的关键在于问题的可能解的列举和可能解的判别. 例如:凑数问题 2. 递归技术 定义:直接或间接调用 ...

随机推荐

- Kubernetes 笔记 04 架构是个好东西

本文首发于我的公众号 Linux云计算网络(id: cloud_dev),专注于干货分享,号内有 10T 书籍和视频资源,后台回复「1024」即可领取,欢迎大家关注,二维码文末可以扫. Hi,大家好, ...

- 一个 Vue & Node 的全栈小项目

约学 - 可以寻找一起自习的小伙伴的Web APP 一个基于 Vue & Node 的移动端全栈小项目 在线演示(请使用移动端查看效果) 源码地址: https://github.com/G- ...

- 安装ubuntu18.10并连接xshell6

emmmm万万没想到上一篇装的linux内核才3.10,装个ubuntu系统来继续自己的docker学习之旅. 话不多说,先下镜像,地址:http://mirrors.melbourne.co.uk/ ...

- PyCharm无法激活

如果你激活软件遇到问题 (Pycharm.GoLand.idea.phpstorm.webstorm.sublime.ultraEdit.win10等等) 比如: 激活框提示Key is invali ...

- 软件工程-构建之法 小学生四则运算的出题程序,android版本

内容中包含 base64string 图片造成字符过多,拒绝显示

- php_D3_“简易聊天室 ”实现的关键技术 详解

PHP+MySQL实现Internet上一个简易聊天室的关键技术 系统目标: 聊天室使用数据库汇集每个人的发言,并可将数据库内的发言信息显示在页面,让每个用户都可 ...

- Linux系统的数据写入机制--延迟写入

我们都知道,在Linux关机的之前都会要运行一个命令那就是sync,这个命令是同步的意思,那为什么要运行这个?而且之前的数据改变我们已经看见了,为什么还要运行这个命令?要回答这个问题就要说一下Linu ...

- mysql锁机制详解

前言 大概几个月之前项目中用到事务,需要保证数据的强一致性,期间也用到了mysql的锁,但当时对mysql的锁机制只是管中窥豹,所以本文打算总结一下mysql的锁机制. 本文主要论述关于mysql锁机 ...

- protobuf、LRU、sigleflight

今天咱一次讲3个吧,赶一下进度,好早点开始聊kubernetes! 从groupcache的项目目录结构看,我们今天要学习groupcachepb.lru.singleflight这3个package ...

- c# IO操作

今天我们主要讨论的IO的一些操作,首先我们先引入三个变量: /// <summary> /// 配置绝对路径 /// </summary> private static str ...