FPGA基础学习(9) -- 复位设计

一开始接触到FPGA,肯定都知道”复位“,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题。

1. 常见问题

自己在学习实践过程中,以及看到网友询问的,有关FPGA复位设计大概有以下几类问题:

- 我板子上没有设计按键复位怎么办?

- 怎么设计上电复位?不可能上电都要去按键吧

- 同步复位还是异步复位?各自优势是啥?

- 高电平复位还是低电平复位?

……

归根结底,就是怎样设计复位,我可能给不出完美的答案,但查阅了一些资料,总结了一些设计中考虑的因素,在加上参考文献,应该能解决99.9%的疑惑。

2. 常见的复位方式

我们习惯上通常使用的复位有三种方式:

硬件开关:复位信号接一个拨码开关或按键,或者RC电路

电源芯片:上电时候电源芯片产生,可以长时间维持,直到稳定。

控制芯片:控制芯片产生复位脉冲。

没有专门的电源或控制芯片,甚至连按键都忘记设计的情况下,有人提出可不可以拿内部计数器做一个所谓的上电“软”复位,如下代码所示,当cnt计数到一定的值时,产生一个复位脉冲信号。

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

begin

if(cnt < 23'd50_00000) //100ms

cnt <= cnt+1'b1;

else

cnt <= cnt;

end

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr0 <= 0;

rst_nr1 <= 0;

end

else if(cnt == 23'd50_00000)

begin

rst_nr0 <= 1;

rst_nr1 <= rst_nr0;

end

else

begin

rst_nr0 <= 0;

rst_nr1 <= 0;

end

end

没有设计外部硬件复位的同学又会反驳,我rst_n都没有!去掉复位,默认上电cnt = 0,可不可以?既然默认cnt = 0了,那其他所有的寄存器不都默认为0了吗?接着往下分析。

3. 合理的复位设计

从参考文献中得出有关复位设计的几条重要结论,有助于我们明确复位设计的方向,如下:

- 低电平复位并不是最合理的处理方式;

- 建议采用异步复位同步化(异步复位同步释放处理);

- 全局复位并不是最佳方式;

- 并不是所有时序电路都要加复位;

对上述结论分析,见后续总结。

3.1 复位电平

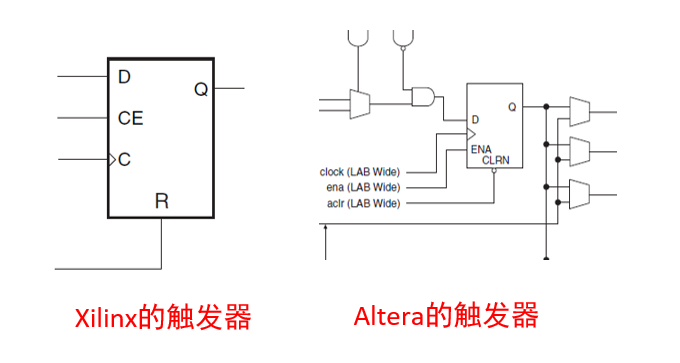

有关复位电平,实际上是跟FPGA芯片内部的触发器结构有关,在之前的博文有提到过。作为xilinx 7系列触发器,其 R 端口既可用作同步置位/复位端口,也可用作异步预设/清除端口,但无论哪种方式,都是高电平有效。Altera的是低电平有效。

当在7系列芯片上采用低电平复位,会有什么问题呢?如下:

如果RTL代码采用了低电平有效的复位模式,综合器将在复位信号驱动寄存器SR控制端之前的插入一个反相器(interver)。你必须使用一个查找表(look up table)来实现反向器,以利用LUT的输入端口。低电平有效的控制信号带来的额外的逻辑可能拉长了执行时间(runtime),将导致更低的FPGA资源利用率,也将影响时序和功耗。

到底我想说点什么呢?尽可能的在HDL代码或者实例化的模块中使用高电平有效的控制信号。如果在设计中,你不能够改变这些控制信号的极性,你需要在代码的顶层文件反转这些控制信号。采用这种方式描述电路的话,这些反向器将被吸收到I/O逻辑中,而不需要使用额外的FPGA逻辑、路径。

所以再次强调:复位电平的选择跟芯片结构有关!

3.2 异步复位同步化

异步复位同步化简单的说就是将异步复位信号在相关的时钟域模块中进行同步化处理。单纯的同步复位、异步复位以及其他的一些复位方式,都存在一些缺陷,比如抗噪声、存在亚稳态等问题,深入学习可以查阅相关文献。

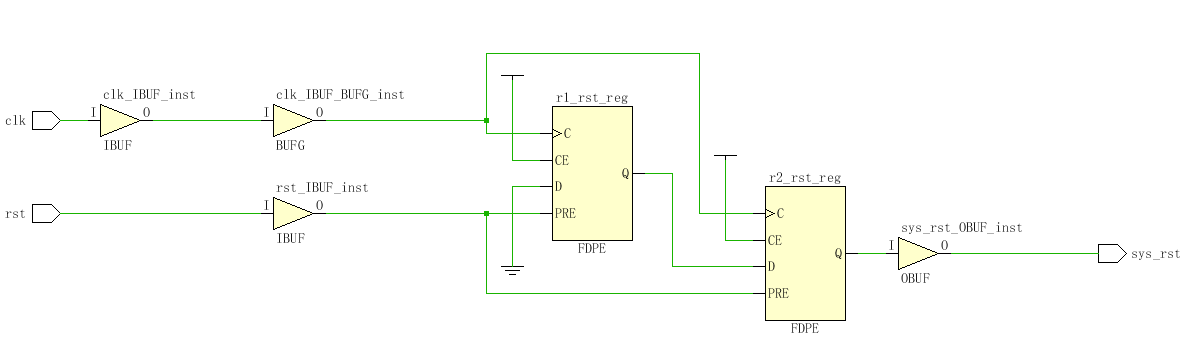

异步复位同步化处理的结构代码及schematic(xilinx 7系列)如下:

module rst_signal(

input clk,

input rst,

output sys_rst

);

reg r1_rst,r2_rst;

always@(posedge clk or posedge rst) begin

if(rst) begin

r1_rst <= 1'b1;

r2_rst <= 1'b1;

end else begin

r1_rst <= 1'b0;

r2_rst <= r1_rst;

end

end

assign sys_rst = r2_rst;

endmodule

可以看到,模块将系统输入的异步复位信号进行同步,产生了一个后续逻辑使用的同步化了的异步复位,随后即可将该复位信号sys_rst用于其他模块的复位。为了减少亚稳态对上述同步器中的两个寄存器的影响,这两个寄存器应该在FPGA中被放置的越靠近越好(相应的约束:set_property ASYNC_REG TRUE [get_cells [list r1_rst_reg r2_rst_reg]]),尽量减少布线延迟。

以上只是一个基本原理示意,在实际使用过程中还应注意以下两点:

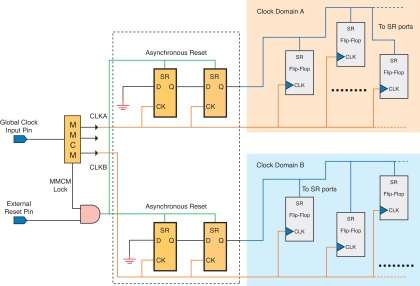

- 外部输入异步复位信号应该增加滤波和去抖处理;

- 在复位之前,确保由 MMCM 或PLL 生成的时钟是稳定且被锁定的;

- 将异步复位信号分别引入不同的时钟域进行同步化

综上,复位处理的原理图如下所示:

3.3 恰到好处的复位

看似简单的复位,实际上不简单,来系数复位的N宗罪:

- 复位网络需要占用布线资源;

- 导致其余信号的布线信号受到影响,降低了它们布线的自由度;

- 增加的布线网络往往需要使用更高速率的芯片;

- 复位网络占用大量布线资源,使得Place&Route的时间大大增加;

- 复位信号需要占用大量的逻辑资源;

- 复位信号需要使用触发器的专用复位管脚;

- 可操作的复位信号往往导致D触发器的输入前增加额外的门操作或专用的复位信号输入;

- 增大整个设计 的尺寸;

- 额外的逻辑消耗降低了系统的性能;

- 阻止了使用高效特征,如Xilinx FPGA特有的SRL16E 移位寄存器。

简单的说,复位的存在会对FPGA的综合面积产生影响,主要体现在两个方面:第一、在编写代买的时候,习惯给所有时序电路都加上复位信号,这样往往会导致资源无形的浪费;第二,没有合理的设计复位电路会产生额外的资源消耗。

什么时候可以叫复位呢?一般判断原则是:

类似于移位寄存器这类直通型电路,只起到一个传输信号的作用,本身不会对信号产生任何影响。其传输信号正确与否,在于其输入端的信号是否正确。因此,此类电路自身无需加复位信号,而只需再起输入端口加复位信号(也就是数据来源处的电路),以控制输入数据。

4. 补充

4.1 所谓的上电初始化

当一个Xilinx的FPGA芯片被重新配置时,每一个单元都将被初始化。在某种意义上讲,这是一个上电之后的“终极的”全局复位操作,因为它不仅仅是对所有的触发器进行了复位操作,还初始化了所有的RAM单元。随着Xilinx FPGA芯片内部的嵌入式RAM资源越来越多,这种“终极的”全局复位操作越来越有意义。对所有的RAM单元进行预定义,在软件仿真和实际操作中都是非常有帮助的,因为这样避免了在上电时采用复杂的启动顺序来清除存储单元内容的操作。

所以在xilinx平台,开篇的“软”复位,实际上是没有多大意义的。

综上,采用以上总结的复位处理方法,应该能解决99.9%的问题了。

参考文献

- 《wp272: Get Smart About Reset: Think Local, Not Global》;

- 《FPGA实战演练. 高级技巧篇》——王敏志编著;

- DC综合之CDC篇

- How do I reset my FPGA?

- Xilinx FPGA复位逻辑处理小结

- FPGA的复位方法几种方法

- 在FPGA开发中尽量避免全局复位的使用?

FPGA基础学习(9) -- 复位设计的更多相关文章

- FPGA基础学习(7) -- 内部结构之CLB

目录 1. 总览 2. 可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础学习(8) --内部结构之存储单元

目录 1. 基本结构 2. BRAM与DRAM的比较 3. BRAM的特点 4. Block Memory的使用 4.1 配置为RAM或ROM 4.2. 配置为FIFO 参考文献: 上一篇中提到了SL ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA基础学习(6) -- 原语

目录 1. IBUF和IBUFDS(IO) 2. IDDR(Input/Output Functions) 3. IBUFG和IBUFGDS(IO) 原语,即primitive.不同的厂商,原语不同: ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础设计(四):IIC协议

很多数字传感器.数字控制的芯片(DDS.串行ADC.串行DAC)都是通过IIC总线来和控制器通信的.不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kb ...

随机推荐

- Cocos2dx之touch事件

今天看了下ccocos2dx touch事件部分的源码,从CCTouch.CCTouchHandler和CCTouchDispatcher简单的做了分析和总结,先直接看源码吧! 1.CCTouch c ...

- Ubuntu14.04下FTP服务器的搭建配置 标签: ubuntuftp服务器虚拟机 2017-06-13 15:24 161人阅读 评

首先说明一下,我是在虚拟机中装的Ubuntu14.04,物理机是Win10,最初只是为了在两个系统间传输文件才在Ubuntu中安装了ftp服务器,从Windows端登陆其即可.最初也是按照网上的各种教 ...

- UVa 1608 Non-boring sequences (分治)

题意:给你一个长度为n序列,如果这个任意连续子序列的中都有至少出现一次的元素,那么就称这个序列是不无聊的,判断这个序列是不是无聊的. 析:首先如果整个序列中有一个只出过一次的元素,假设是第 p 个,那 ...

- 关于利用word发布文章到博客

目前大部分的博客作者在写博客这件事情上都会遇到以下3个痛点:1.所有博客平台关闭了文档发布接口,用户无法使用Word,Windows Live Writer等工具来发布博客.2.发布到博客或公众号平台 ...

- ScreenCapturePro2 for Joomla_3.4.7-ckeditor4x

1.1. 与Joomla_3.4.7整合-ck4 示例下载:Joomla_3.4.7, 1.1.1. 添加screencapture文件夹 路径:/media/screencapture 1. ...

- WordPaster2项目变化

1.1.1. jsp 1.引入json2.min.js 2.控件名称改为WordPasterManager 3.文件保存逻辑更新,直接使用控件生成的文件名称 1.1.2. asp.net 1.引入js ...

- unity小记

1.window下的Occlusion Culling是实现遮挡剔除效果,即不再摄像机里出现的物体使其不被渲染. 这样做要使物体为静态的,而且效果在设计时只在Occlusion面板下有效 2.wind ...

- cenos7切换阿里源

备份并安装base reop源 cd /etc/yum.repos.d sudo mv CentOS-Base.repo CentOS-Base.repo.bak 下载阿里源并配置 sudo wget ...

- @cms_content_list

[@cms_content_list typeId='1,2,3' count='18' orderBy='4' channelId='75' channelOption='0' dateFormat ...

- 15、Semantic-UI之导航

15.1 面包屑导航 在Semantic-UI中有多种样式实现面包屑导航,类似 / > 等. 示例:定义定义基础面包屑导航 <div class="ui container& ...