FPGA噪声干扰

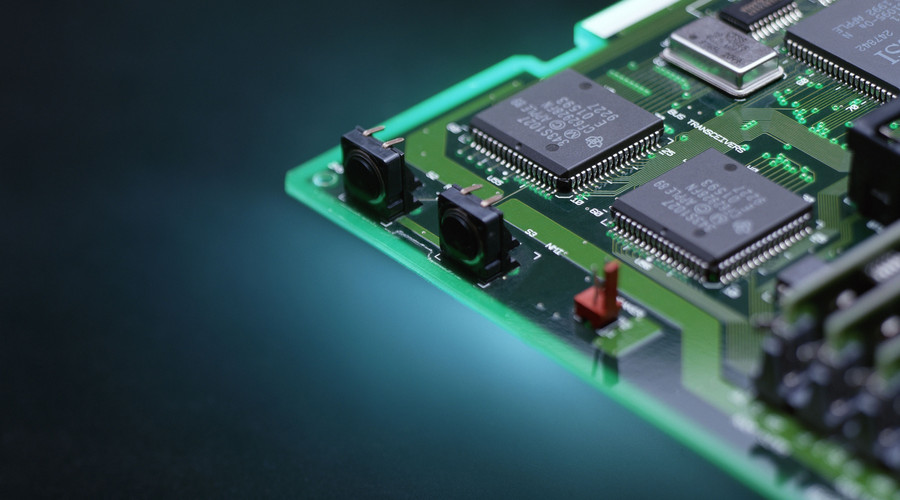

在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

1、信号线的等长

以SDRAM或者DDRII为例,数据线,命令线,地址线以及时钟线最好等长,误差不要超过500mil。

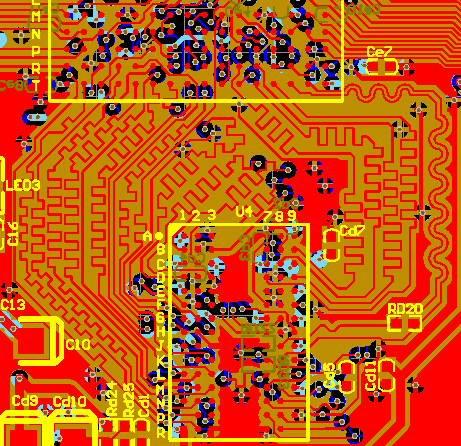

上图是FPGA与SDRAM布线,时钟频率设定为125M,为了等长可以走蛇形线。

蛇形走线虽然可以做到走线等长,但同时也占用更多的PCB面积。蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。

DDRII线路等长设计,最右边的弧度较大的走线为差分的时钟线,时钟线质量要求是比较高的。

布线是痛苦的,也是繁琐的,布不通时需要重新布线,不厌其烦的尝试,才能做出更好的效果。

2、电源芯片的选择

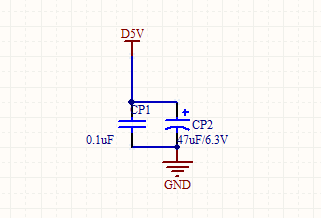

很多高速AD场合,开关电源并不合适,因为开关电源带来很多毛刺。大多数选择线性稳压电源。小编以ASM1117为例为大家介绍电源芯片中电容的使用。

5V电源输入端,应加容值较大的钽电容或者电解电容滤除电源的低频噪声,加104(0.1uF)瓷片电容滤除高频噪声。电源走线应适当加宽。

在PCB布线时,也应该在5V走线的末端加容值较大的电容。

以ASM1117-3.3降压为例,如下图:

如上图,1117的3.3输出走线往下走,那么电容CP5放在旁边是没有任何效果的,通常这种电容是104瓷片电容,这个电容的容值是一个非常好的容值,在电源滤波中效果非常好。

那么该如何布局?

如上图,此种布局,CP28以及 CP10放置,电容应当放在电源走线路径上。注意电容不能离芯片引脚太远,电容有滤波半径,超出某一范围,电容将起不到滤波效果。

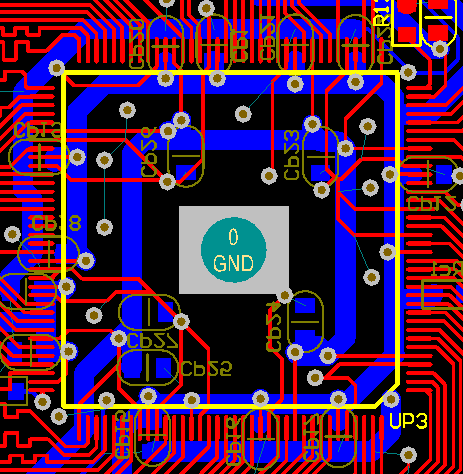

FPGA电源布线,根据多年布线经验以及产品稳定性,小编为大家推荐以下方案:

以QFP封装的FPGA为例,有三种电源,1.2V,2.5V,3.3V。布线时最好如上图效果,电源线之间最好隔开距离,FPGA电源引脚要加入104电容。

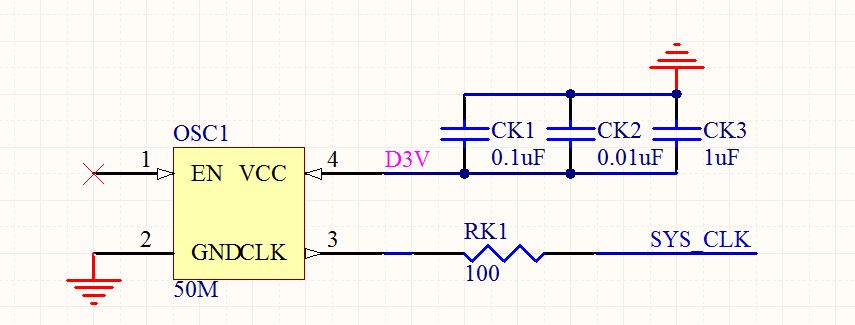

3、有源晶振布线

原理图设计如上,时钟输出端串入100~330欧姆的电阻,防止阻抗不匹配时时钟信号反射叠加。

有源晶振电源端加入103、104、105三种瓷片电容滤波,防止电源噪声和时钟之间的串扰。

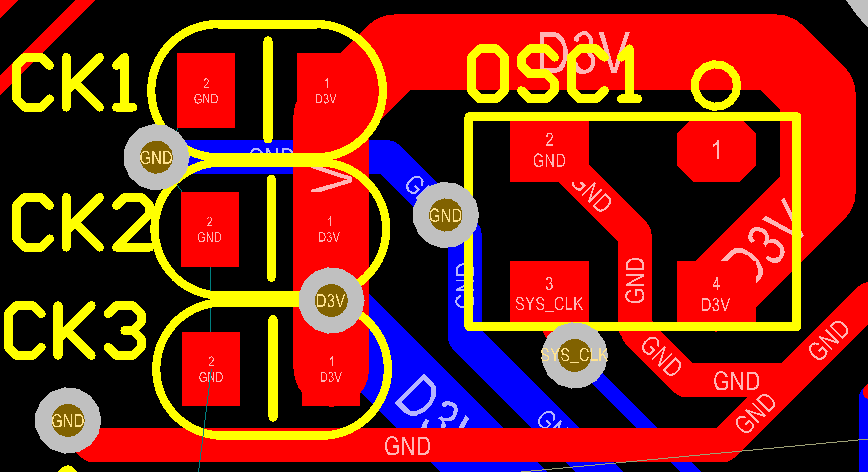

PCB布线时,上述效果时很糟糕的。晶振下面不应布线,电源走线应远离时钟线布线,并且中间加宽地线耦合,防止干扰。

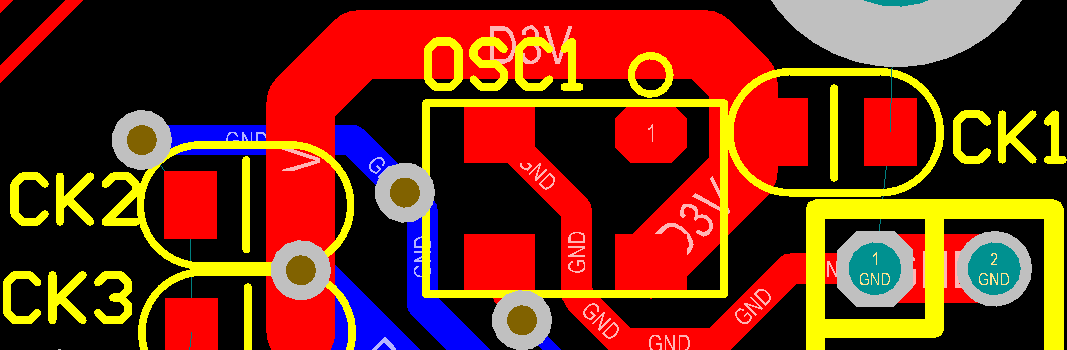

如上图布线,电源线避开时钟线,中间加入粗地线,注意有些地线不需要手动连接,放置地过孔,在铺铜(地网络)时,会自动加入。

此种方式放置电容亦可行。

FPGA噪声干扰的更多相关文章

- FPGA与simulink联合实时环路系列——实验三 按键key

实验三 按键key 实验内容 在FPGA的实验中,经常涉及到按键的使用,按键是必不可少的人机交互的器件之一,在这些实验中,有时将按键的键值读取显示到数码管.LCD或者是通过串口传送到PC的串口助手上进 ...

- FPGA与simulink联合实时环路系列——实验二LED

实验二LED 实验内容 在实验一的基础上,将simulink产生的测试信号输出到FPGA开发板上的LED灯进行显示,这里要在生成的硬件模型上进行修改,将传送到FPGA的信号输出到8个LED灯上,并且对 ...

- FPGA优化之高扇出

Fanout即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛.因此,在写代码时应尽量避免高扇出的情况.但是,在某些特殊情况下,受到 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- FPGA与simulink联合实时环路系列——实验一 测试

实验一 测试 实验内容 在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示.由此来测试整个硬件在环的功能是否正常,并且熟 ...

- FPGA与simulink联合实时环路系列—开篇

FPGA与simulink联合实时环路系列—开篇 作为网络上第一个开源此技术,笔者迫不及待地想将此技术分享出来,希望大家多多支持.笔者从2011年接触FPGA以来,从各个方面使用FPGA,无论是控制. ...

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

随机推荐

- LeetCode第[16]题(Java):3Sum Closest (和目标值最接近的三个数的和)——Medium

题目难度:Medium 题目: Given an array S of n integers, find three integers in S such that the sum is closes ...

- Webstorm常用快捷键备忘(Webstorm入门指南)

WebStorm 是jetbrains公司旗下一款JavaScript 开发工具.被广大中国JS开发者誉为“Web前端开发神器”.“最强大的HTML5编辑器”.“最智能的JavaSscript IDE ...

- Ajax-05 使用XMLHttpRequest和jQuery实现Ajax实例

需求: (django)使用XMLHttpRequest和jQuery实现Ajax加法运算 url.py: from django.conf.urls import url from hello im ...

- idea结合git使用

1.下载安装好git.exe2. 2.安装好以后在cmd输入git 3.在idea配置git环境 4.托管项目到码云 5.登录码云官网,地址就是你在码云注册的账号和密码

- windows7自动登录后锁定 & 其他VBS

首先设置自动登录(原已设置登录密码),在开始菜单搜索框输 入 “netplwiz” 按 回车,打开高级用户控制面板,然后取消对“要使用本机,用户需输入用户名和密码(E)”项的勾选,系统弹出窗口要求输入 ...

- ASP.NET学习路线图(转)

如果你已经有较多的面向对象开发经验,跳过以下这两步: 第一步 掌握一门.NET面向对象语言,C#或VB.NET 我强烈反对在没系统学过一门面向对象(OO)语言的前提下去学ASP.NET. ASP.NE ...

- h5启动原生APP总结

许久没有写博客了,最近有个H5启动APP原生页面的需求,中间遇上一些坑,看了些网上的实现方案,特意来总结下 一.需要判断客户端的平台以及是否在微信浏览器中访问 1.客户端判断 在启动APP时,Andr ...

- 【SQL查询】日期的转换_to_date/to_char

1. 日期转换为字符 select to_char(sysdate,'yyyy-MM-dd HH24:mi:ss') from dual; 2. 字符转换为日期 select to_date('200 ...

- c++指针初探

业余时间准备重温一下c++,因为在阅读Android源码到native层的时候感觉有点吃力,只是在大学时候很不用心的学过c++,所以重温下以便打好一些编程基础知识,本篇就很简单的对c++的指针做初步的 ...

- C#调用EasyPusher推送到EasyDarwin实现视频流中转

本文转自:http://www.cnblogs.com/kangkey/p/6772863.html 最近在公司项目中,遇到需要将内网的监控视频信息,在外网进行查看,最终通过查阅资料,发现EasyDa ...