基于CameraLink的逻辑综合和版图设计

前期接口设计用的是Vivado18.3+Modelsim10.6,逻辑综合及版图生成的环境是Ubuntu16,逻辑综合用的工具Design Compiler,生成版图用的工具是Encounter。

下面是关于我做的CameraLink接口的ASIC逻辑综合和版图设计流程,重点介绍了逻辑综合过程:

(1)CameraLink接口实现

(2)功能仿真

(3)逻辑综合

(4)布局布线及版图生成

(5)后仿真

1、CameraLink接口实现

1.1、接口设计

Camera Link标准技术是在National Semiconductor公司下的Channel Link标准技术下发展而来的。CameraLink标准在ChannelLink标准下的视频信号的基础上又多加了6对LVDS。在Camera Link Base/Medium/Full模式下,4对用于相机输入与图像采集卡输出的数据传输信号,另外2对用于拍摄相机设备和图像采集卡之间的异步串行通信。在标准的CameraLink接口中,数字图像相机信号分为:基于ChannelLink标准的视频图像数据(PortA-PortH)及使能信号(Fval、Lval、Dval及Spare)、相机控制LVDS信号对(CC1-CC4)、异步串行通信LVDS信号对(SerTFG、SerTC)。标准Camera Link协议一总定义10个端口,每一个端口都是8位。其中bit0被定义为最低位,bit7定义为最高位,而其中的视频图像数据信号端口又与相机的配置模式相关,相机的配置不同,Camera Link所用到的芯片数量就会不同,而且所用的Cameralink接口物理连接器的数量也会不同,具体如表1所示:

表1接口配置对应相应数值

|

Camera Link 接口配置 |

端口 |

数据位宽(Max) |

芯片 |

连接器 |

|

Base |

A~C |

28 |

1 |

1 |

|

Medium |

A~F |

56 |

2 |

2 |

|

Full |

A~H |

84 |

3 |

2 |

1.2、CameraLink数据输出具体实现

Camera Link接口配置选择为Base。而在Base模式下,可以使用1~3×8-bit、1~2×10-bit、1~2×12-bit、14-bit、16-bit及24-bitRGB的Bit assignments,而对于整个系统而言,将使用Base配置下28位总位宽的16-bit,以满足16位像素数据的输入要求。

在Base配置下,Camera Link的视频图像数据信号如表2所示:

表2 Base配置下的视频图像数据信号

|

视频图像数据信号 |

位数 |

描述 |

|

Date |

24 |

图像数据 |

|

FVAL |

1 |

帧有效信号 |

|

LVAL |

1 |

行有效信号 |

|

DVAL |

1 |

数据输出有效信号 |

|

SPARE |

1 |

备用信号 |

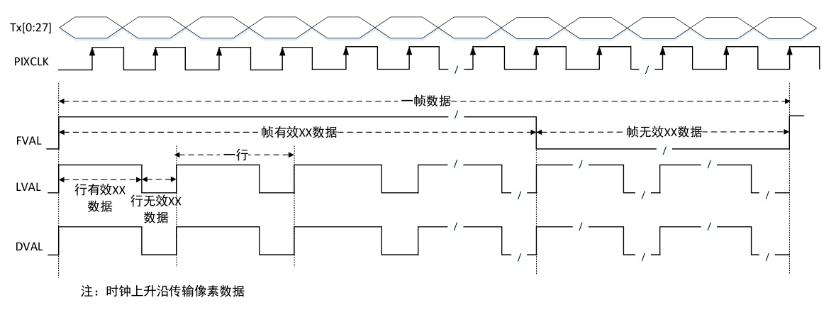

在Camera Link接口实现中,依据视频数据信号时序图来进行数据的传输,主时钟CLKcamera信号的上升沿采集数据,通过对FVAL、LVAL及DVAL的进行时序的操作,设计中选择了640×512的图像分辨率及帧频F帧频=100Hz的数据输出,为了实现100Hz帧频需要确定行有效像素时钟周期个数A=640和行无效时钟周期个数Q及帧无效时钟周期个数C,具体的的实现如下计算:F帧频= CLKcamera (MHz)/{512×(A+Q)+C},最后主控FPGA将12位并行数据信号和依据F帧频产生的FVAL、LVAL及DVAL送入Camera Link接口Camera Link视频数据信号时序如图1所示:

图1 Camera Link视频数据信号时序图

2、功能仿真

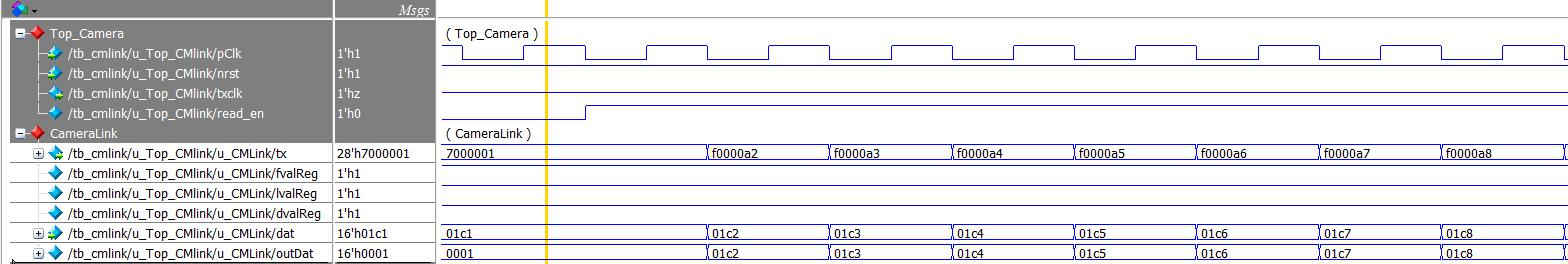

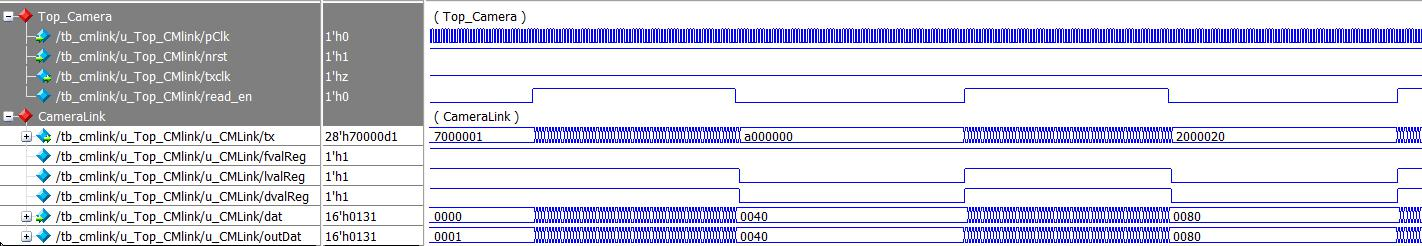

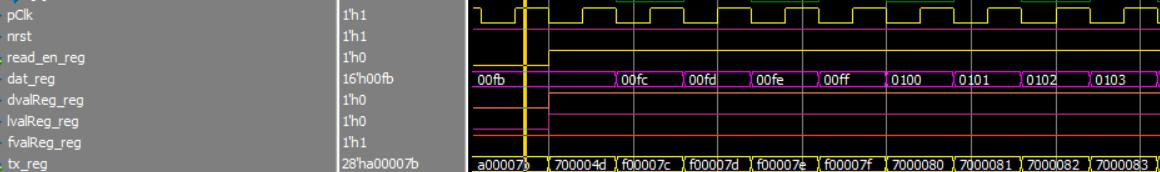

在Camera Link模块的仿真中,加载了CMLink_ctrl和CMLink模块,通过16 bit像素值dat信号输入至CMLink模块,结合camera_pause、empty、read_en使能等信号按照《Camera Link Specifications v2.0》手册将16 bit像素值信号转换至28 bit并行tx数据进行像素输出,如16’h01c2转换至28’hf0000a2。接口需要在视频帧有效信号fvalReg、行有效信号lvalReg及数据有效信号dvalReg处于高电平时进行像素数据的传输,其中fvalReg、dvalReg、lvalReg、dat、tx信号仿真如图2所示:

3、逻辑综合

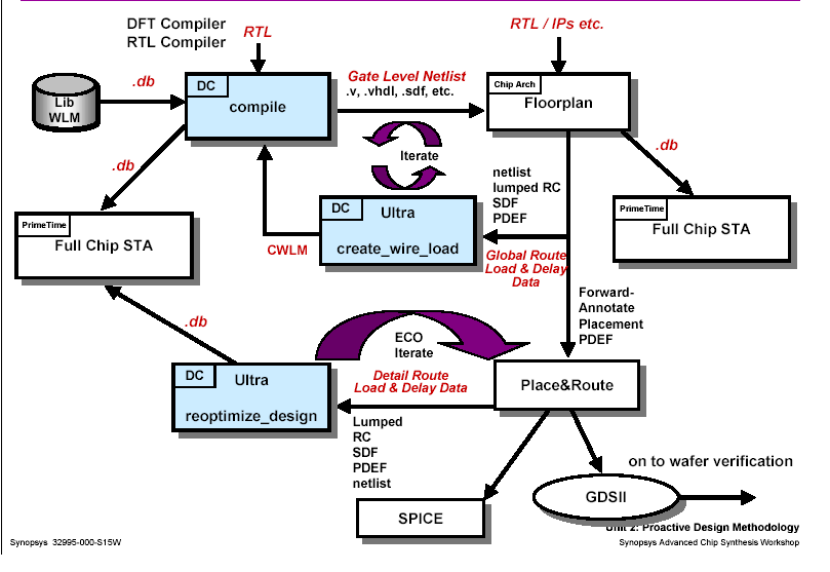

综合是完成从RTL代码到门级电路的转换。如果在综合时,链接了厂家的库文件,则门级电路使用的器件是厂家库文件中提供的器件。综合在整个IC设计中,起到的作用如图4所示。

图 4 综合在IC设计中的作用

3.1 综合的特性

3.1.1 综合是由约束驱动的

对于一个设计来说,在进行综合前,需要给这个设计加上约束,约束也就是综合的目标,综合工具会竭力满足约束,以实现综合的目标。约束可分为多方面,如时序方面的约束、面积方面的约束、环境属性方面的约束、驱动和负载方面的约束等。其中最重要的约束是对时钟等与时序相关的属性进行约束。在综合时,约束的各个方面可能存在一定的矛盾,如对速度和面积的约束,见图2所示。综合的过程就是找到一个最好的平衡点,满足各个方面的约束。

3.1.2 综合是基于path分析的

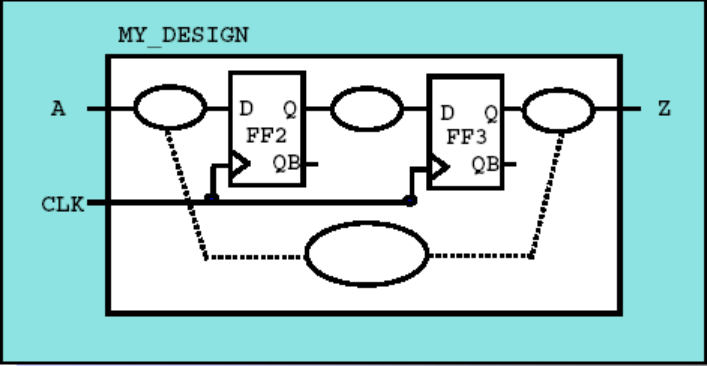

在整个综合的过程中,完成是基于path进行时序分析的,因此path的概念非常重要。何谓path?如下图5所示。

图 5 Timing Path的概念

Path是综合工具进行时序分析的基本单位。对于一条path而言,它的起点只能是输入端口,或者触发器/寄存器的时钟端;终点只能是输出端口,或者触发器/寄存器的数据输入端(对D触发器而言,就是D端)。

结合图3而言,其中共有4条path,分别为:

1) 输入端口A -> FF2的D端;

2) FF2的CK端-> FF3的D端;

3) FF3的CK端-> 输出端口Z;

4) 输入端口A -> 输出端口Z。

同一个时钟域多条path,组成一个组,称为path group。与任何时钟都没有关系的path也组成一个组,成为default path group。结合图3而言,有2个path group,其中path 2和path 3 属于时钟CK的path group,path 1和path 4属于default path group。

在计算一条path的延时信息时,是将这条path上所有线延时加上所有的器件单元延时。

3.2 综合的步骤

对于Design Compiler而言,综合的步骤如下:

1) 将需要进行综合的设计读入Design Compiler的内存中;

2) 对设计添加合适的约束;

3) 对设计进行综合优化;

4) 分析综合的结果是否满足要求;

5) 如果满足要求的话,保存综合的结果。

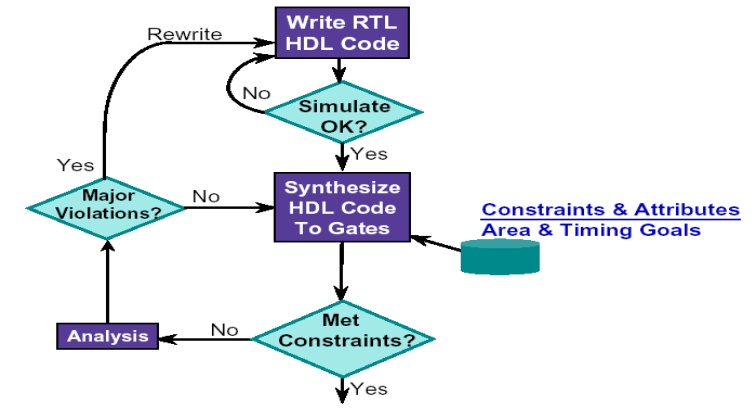

综合的主要过程也可以用图6进行表示。

图6 综合的主要过程

3.3 Design Compiler简介

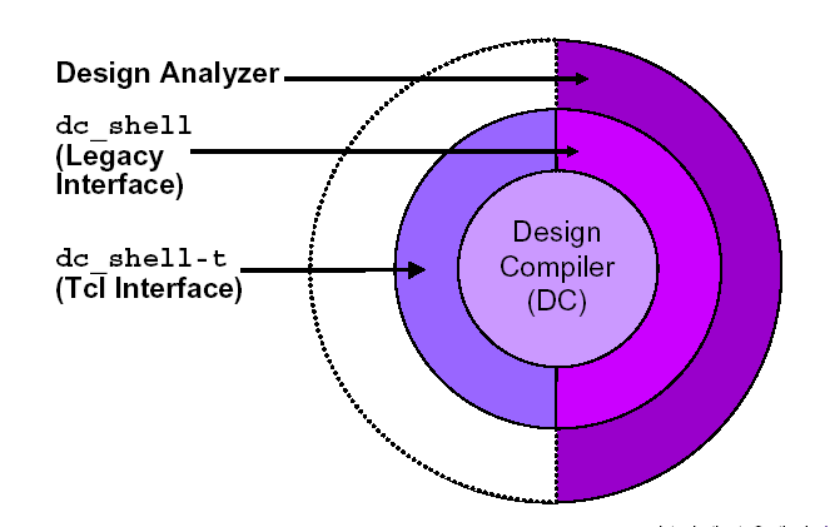

3.3.1 Design Compiler接口模式

Design Compiler是Synopsys公司推出的综合工具,在业界有较广泛的应用。

Design Compiler有三种接口方式:图形化接口、dc shell接口和dc shell tcl接口。

图7 Design Compiler的接口方式

对于初学者来说,建议使用图形化方式,便于使用,同时建议打开命令窗口,以便可以尽快熟悉Design Compiler的命令。图形化方式需要占用较多的内存资源,运行速度相对命令行方式来说较慢。

3.3.2 Design Compiler启动脚本文件

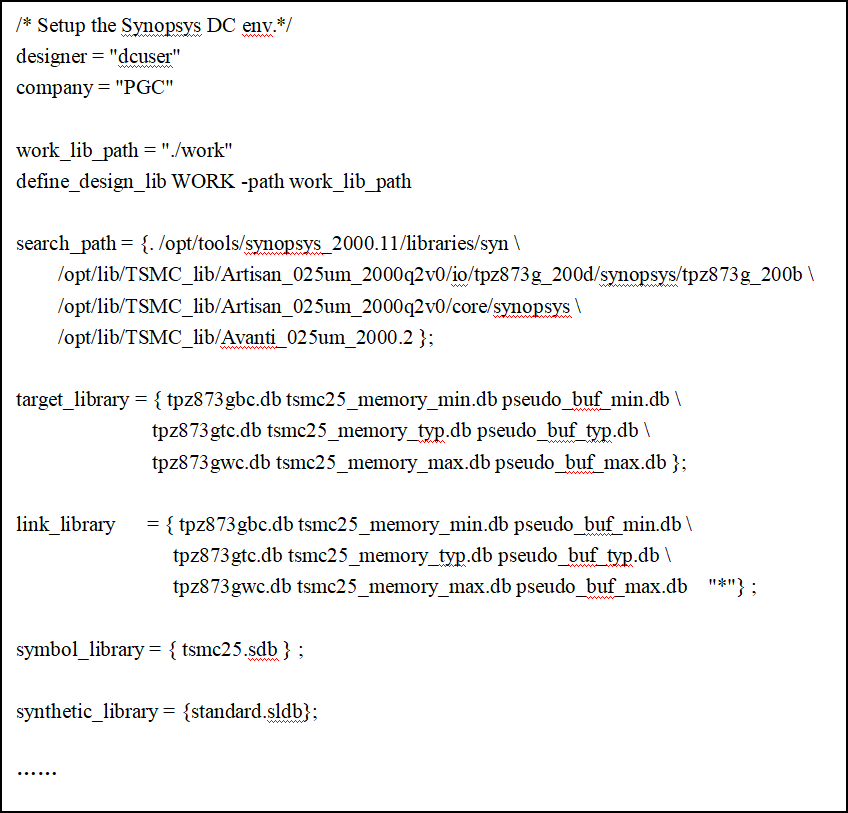

Design Compiler启动时需要执行一个启动脚本文件,该文件名为.synopsys_dc.setup。执行该脚本文件帮助DC链接指定的库文件,也就是综合需要使用的厂家库文件。库文件是由厂家提供的,而不是由Synopsys公司提供。

.synopsys_dc.setup文件可以放在下面三个目录下:

1)$SYSNOPSYS/admin/setup

2)用户的home目录

3)用户的当前工作目录

DC启动时搜索.synopsys_dc.setup文件的顺序为先查找用户的当前工作目录,然后查找用户的home目录,最后再查找$SYSNOPSYS/admin/setup目录。

若在用户的当前工作目录下存在.synopsys_dc.setup文件,则直接使用该文件启动DC。建议将.synopsys_dc.setup文件放在用户的当前工作目录下,方便使用和修改。.synopsys_dc.setup文件中需要为DC指定链接的库文件,这是通过设置target_library,link_library,symbol_library等保留字变量实现的。

target_library指定的库文件是DC在搭建电路时使用的库。在DC映射的过程中,会根据电路功能选择库中的器件,并在时序分析时,使用库中各器件的timing数据。link_library指定的库中包含HDL源代码所有单元的示例,综合使用的线载模型和工作环境模型。symbol_library指定的库用来将库中的器件用图形表示出来。下面是一个.synopsys_dc.setup文件的例子(节选其中部分内容)。

另外,为了能使用户当前工作目录的条理清晰,建议在DC的当前工作目录下,划分source、scripts、mapped和reports等子目录。在source子目录下存放RTL源代码,scripts目录下存放综合的各种约束文件,mapped目录下存放综合后的网表文件,reports目录下可以用来存放各种报告文件。

3.3.3 Partition的意义

Partition是把复杂的、规模较大的设计划分为多个规模适中的部分,以便综合时间不要过长,比较容易得到满足要求的综合结果。Partition应该在编写RTL代码前进行,在方案设计时就充分考虑模块的大小、模块间的连接等要素。只有这样才能够得到比较好的partition结果。综合中,能够对partition进行一定的调整,但效果有限。所以这里要强调,partition应该在编写RTL代码前进行。综合中进行partition的主要原则有:

1) 不要有组合逻辑穿过层次边界;

2) 每个层次边界,最好以寄存器做输出;

3) 不要有胶合逻辑(glue logic)穿过层次边界;

4) 限制每个块(block)的大小;

5) 把输入输出pad、时钟产生模块、JTAG模块和核心逻辑分开。

下面结合多个例子,说明partition的原则。

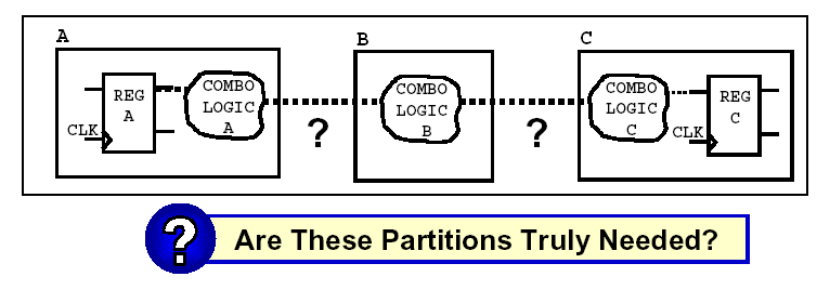

例1:

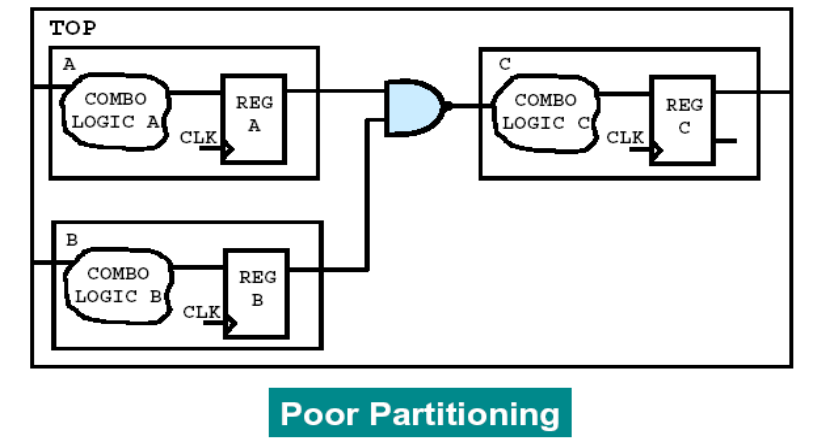

图8 Partition的原则(例1)-a

这个例子中,模块B是一个纯组合逻辑的电路,跨接在模块A和模块C之间,违背了原则1。另外模块A以组合逻辑输出做为层次的边界,违背了原则2。

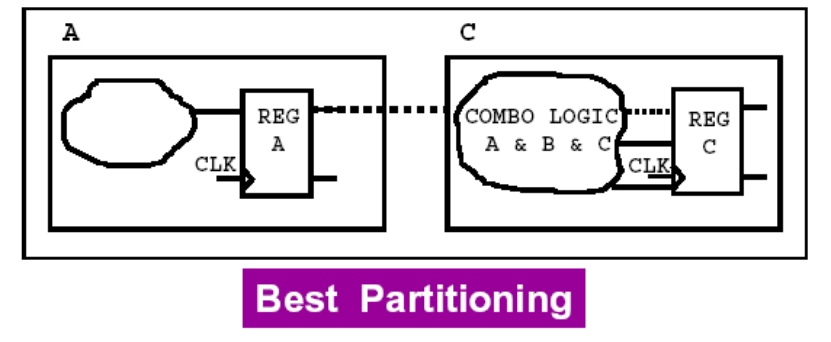

对于例1来说,较好的partition方式如下图所示。

图9 Partition的原则(例1)-b

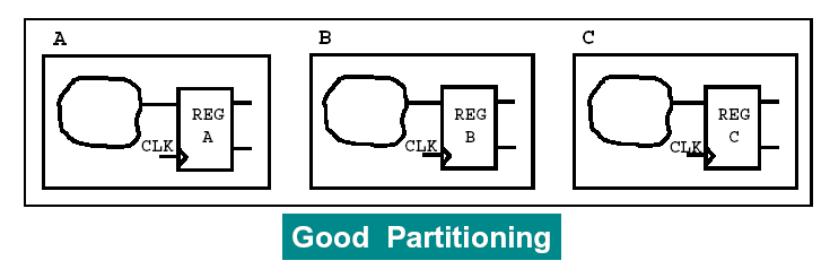

例2:每个模块都是以寄存器输出,满足原则2,所以是一个比较好的partition结果。

图10 Partition的原则(例2)

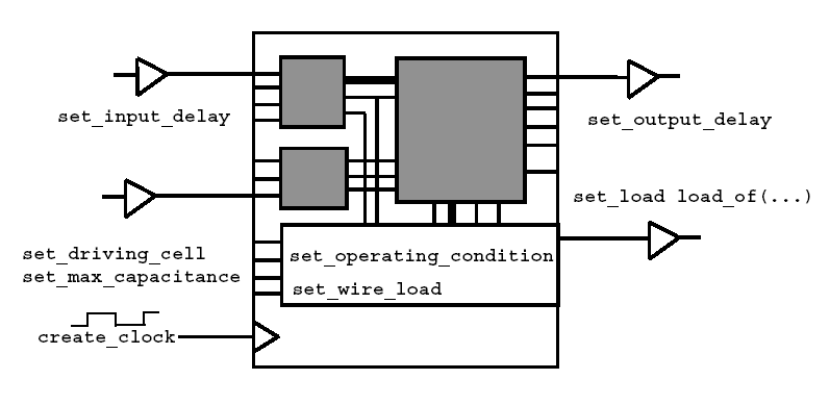

例3:在这个例子中,模块A、B、C间有一个两输入与非门,这个两输入与非门属于胶合逻辑,穿过了模块A、B、C的边界,违背了原则3。

图11 Partition的原则(例3)-a

对例3的修改方法如下图所示。

图12 Partition的原则(例3)-b

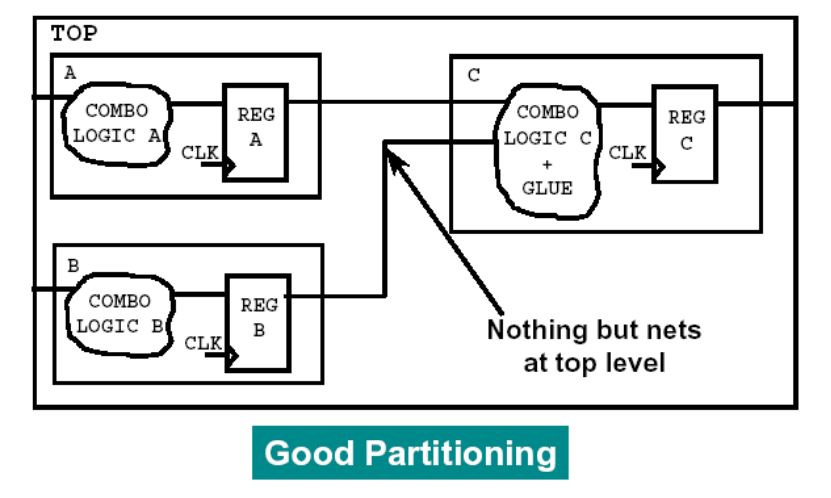

例4:这个例子中,时钟产生模块、异步逻辑模块、输入输出PAD、JTAG模块与核心逻辑模块CORE是划分开的,满足原则5,是个很好的partition。

图13 Partition的原则(例4)

3.3.4 约束文件

学习使用DC的命令,设置约束,是本教材的核心内容。

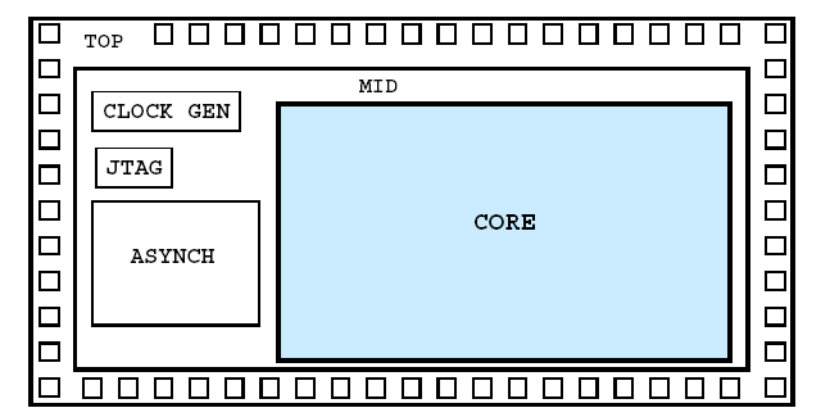

对一个需要进行综合的设计,如果不加任何约束就进行综合是没有任何意义的。只有加上了合理的约束后,综合算法才有目标,才能综合出满足需求的电路。对设计需要加上的所有约束、命令可以写入脚本(script)文件中,就成为约束文件。一般情况下,约束文件中应该包括以下内容,如下图14所示:

图14 约束文件的基本内容

其中主要有对时钟的定义,并定义时序方面的其他约束,如设置input delay,output delay等。对于输入信号、输出信号,还要考虑其驱动、负载问题,这是通过设置输入信号的driving cell,设置输出信号的load来实现的。工作条件对芯片性能的影响也是必须考虑的因素,需要设置operating condition。随着制造工艺的不断提升,线延时成为延时信息中越来越重要的部分,因此也要考虑设置线载模型。这些是主要的约束条件,在实际工作中,约束文件中还需要其他一些约束条件,详细情况见下面的章节。

3.3.5 综合策略和方法

3.3.5.1 自上而下的综合策略

自上而下综合的步骤一般包括:

1) 把整个设计读入DC的存储区中;

2) 解决多次实例的问题;

3) 对最高层模块加上合适的约束;

4) 综合

5) 评估综合的结果

6) 保存综合结果

这里需要注意多次实例化的问题。

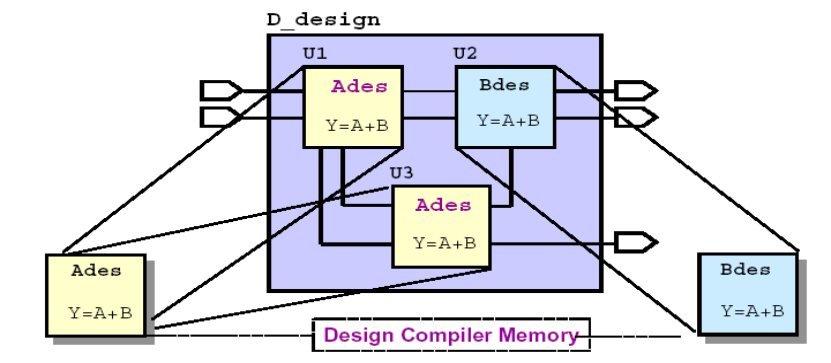

图15 设计中出现多次实例化

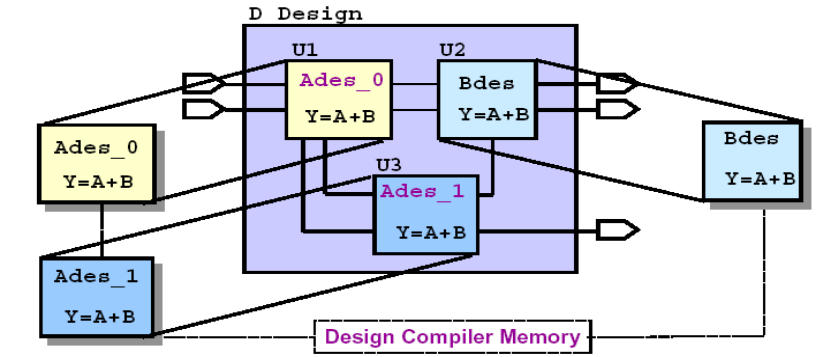

图15中,在D_design中子模块Ades被实例化了两次。在自上而下综合策略中,要解决其多次实例话问题,必须通过uniquify命令。执行该命令后,子模块Ades的每次实例化将对应唯一的一个design名,如图16所示,U1对应的design名为Ades_0,U3对应的design名为Ades_1。这样Ades_0和Ades_1综合出的结果有可能存在差异。

图16 uniquify解决多次实例化问题

下面是一个自上而下综合策略的例子(dc shell script模式),其中D_constraints.scr是约束文件,其中包括各种约束命令。

current_design D_design

include D_constraints.scr

uniquify

compile

自上而下策略对规模不大的设计是非常适用的,而且使用起来简单方便,不需要考虑模块之间的关系,因此花费的人工很少。但是另一方面,由于该策略需要把整个设计读入DC的memory,并进行综合,对于规模比较大的设计,会占用大量的系统资源,如CPU、memory等,综合时间也会非常长。

3.3.5.2 自下而上的综合策略

自下而上综合的步骤一般包括:

1) 把整个设计分成若干子块,对每个子块分别加约束,并进行综合;

2) 每个子块的综合结果必须满足其约束条件;

3) 对最顶层模块加约束条件;

4) 为综合过的每个子块设置dont touch属性

5) 综合;

6) 评估综合的结果

7) 保存综合结果

采用自下而上策略,非常容易解决多次实例化的问题。以图32为例,首先对Ades子模块加约束,并进行综合,检查Ades子模块的相关报告,当其满足所有约束条件时,为其设置dont touch属性,再对D_design模块加约束,进行综合即可。

下面是自下而上方式综合图32所示设计的script文件(dc shell tcl模式)

read_db unmapped/A_des.db

set current_design Ades

source Aconstraints.tcl

compile

read_db unmapped/D_design.db

link

set current_design D_design

set_dont_touch [get_design Ades]

source Dconstraints.tcl

compile

用compile+dont_touch这种方式也可以解决多次实例化问题,采用这种方式,子模块Ades只被综合了一次,U1和U3是对同一个Ades的实例化。自下而上综合策略通过分块综合的方法,可以综合非常大的设计,对综合的设计规模几乎没有限制。但这种方法需要编写多个约束文件,而且各个块之间的关系必须由工程师考虑,增加了人工。另外若各个子块满足各自的约束,而顶层模块无论怎样都不能满足约束条件时,需要再返回到子块的综合,重新规划子块的约束。

3.3.6 优化的参数选择

compile过程分为三个层次:结构层、逻辑层和门级层。

结构层是最高层次的综合、优化,主要完成选择合适的DesignWare,表达式的公共部分共享,资源共享和操作符的重新排序。这部分同coding style关系紧密。

逻辑层完成从GTECH单元到逻辑单元的优化。门级层最终完成组合逻辑和时序逻辑的映射。

3.3.6.1 Compile –map_effort

优化的努力程度是可选的(low、medium、high),默认情况是medium。建议对一个设计进行第一次综合时,采用默认值。选择high时会占用较多的CPU时间,而且不能保证解决所有问题。

3.3.6.2 Compile –incremental_mapping

-incremental_mapping选项只能对已经是门级电路的设计进行,这时不会再返回到GTECH,也就不再进行逻辑层的优化。使用这个选项时,优化的执行速度非常块。当timing分析时,出现的violation非常少,并且slack值较小时,建议使用这个选项。

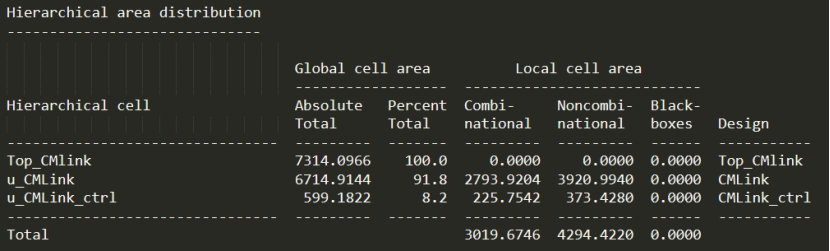

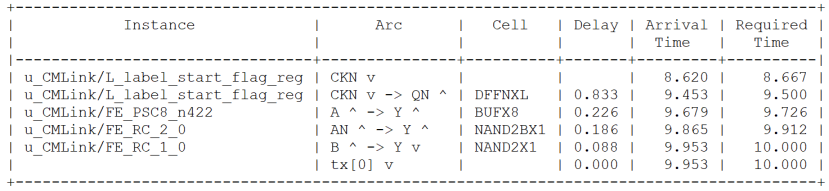

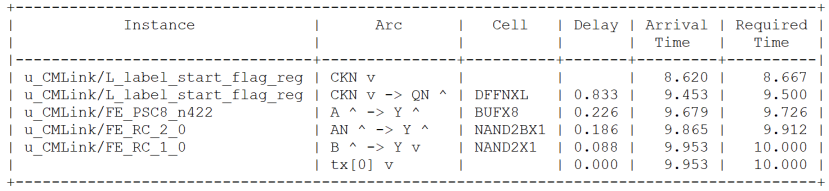

3.4 逻辑综合整个文档过程

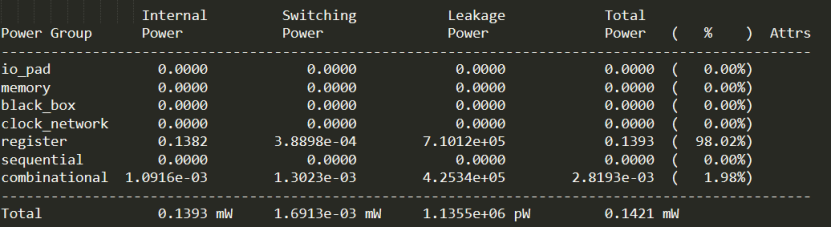

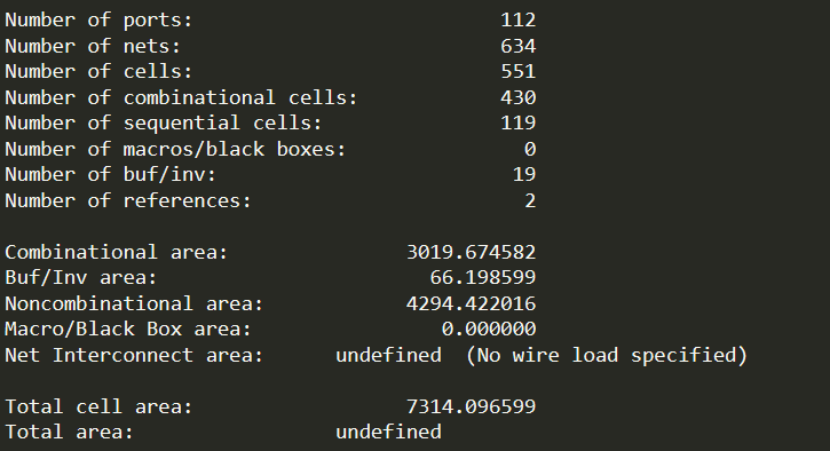

DC综合报告(功耗 面积 时许报告)

图17 DC综合报告

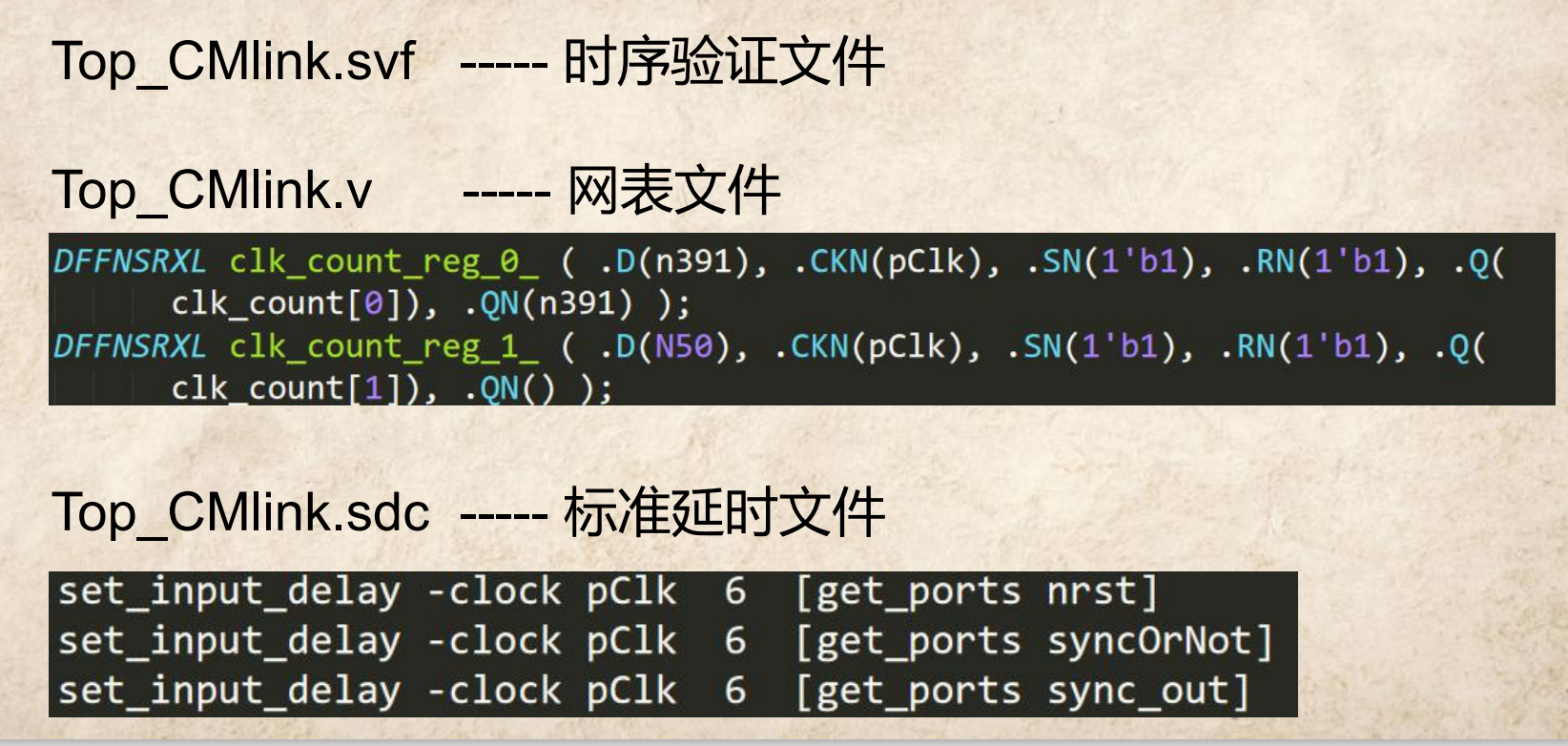

3.6 综合后重要文档

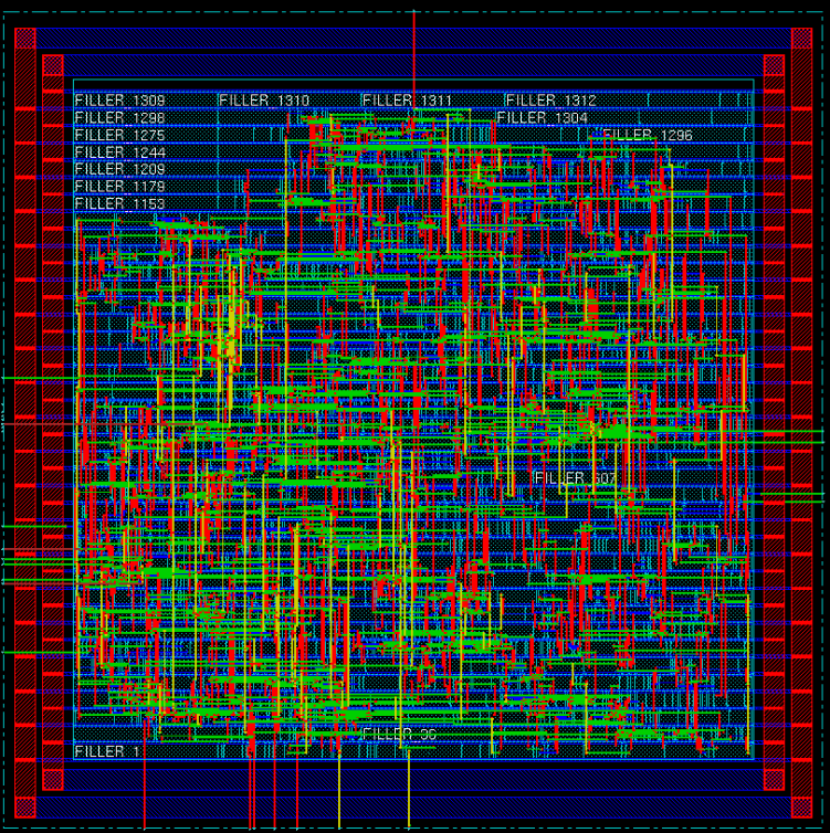

4、布局布线及版图生成

4.1 布局布线准备过程及实现

图18 版图设计后的功耗及时序报告

图19 CameraLink版图

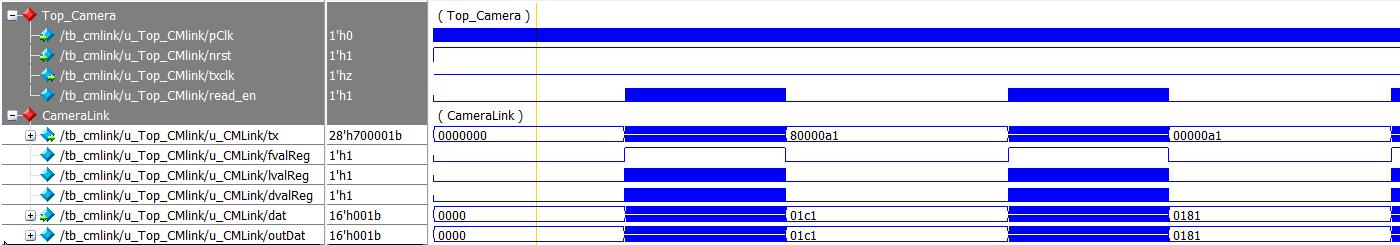

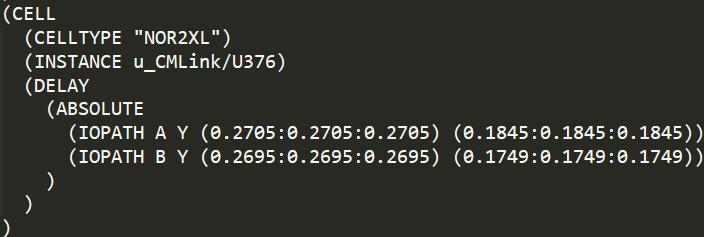

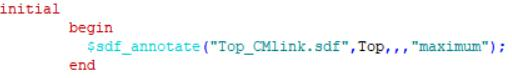

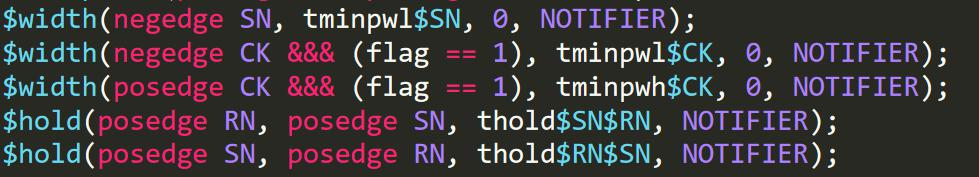

5、后仿真

在后仿过程中,触发器需要满足工艺库中的Hold和Setup时间,并在实际电路有延迟情况等等,可以通过对波形的对照来判断后仿真的仿真情况,但是最终是没有影响功能。

图 22 后仿图示

基于CameraLink的逻辑综合和版图设计的更多相关文章

- 基于ZigBee的家居控制系统的设计与应用

基于ZigBee的家居控制系统的设计与应用 PPT简介:http://pan.baidu.com/s/1i38PC6D 摘 要 智能家居是未来家居的发展方向,其利用先进的网络技术.计算机技术和无线通 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于Web在线考试系统的设计与实现

这是一个课程设计的文档,源码及文档数据库我都修改过了,貌似这里复制过来的时候图片不能贴出,下载地址:http://download.csdn.net/detail/sdksdk0/9361973 ...

- 白瑜庆:知乎基于Kubernetes的kafka平台的设计和实现

欢迎大家前往腾讯云+社区,获取更多腾讯海量技术实践干货哦~ 本文首发在云+社区,未经许可,不得转载. 自我介绍 我是知乎的技术中台工程师,现在是负责知乎的存储相关组件.我的分享主要基于三个,一个是简单 ...

- 基于Spring-Cloud的微服务框架设计

基于Spring-Cloud的微服务框架设计 先进行大的整体的框架整理,然后在针对每一项进行具体的详细介绍

- 基于Linux的智能家居的设计(3)

2 硬件设计 本课题的硬件设计包含主控制器.传输数据设计.数据採集设计.控制驱动设计.显示设计.门禁设计. 2.1 主控制器 依据方案三选择S3C6410主控芯片,S3C6410是由Samsung ...

- iOS 基于MVC设计模式的基类设计

iOS 基于MVC设计模式的基类设计 https://www.jianshu.com/p/3b580ffdae00

- 基于Linux的智能家居的设计(4)

3 开发环境的搭建 本次课题使用的开发环境比較特殊.没有一个现成的集成开发环境,需要自己一步一步的搭建开发环境,开发环境的搭建的过程十分复杂,并且假设没有这个开发环境本次课题就无法进行. 因此.在进 ...

- 基于S2SH开发病房管理系统的设计与实现 源码

基于S2SH开发病房管理系统的设计与实现: 开发环境: Windows操作系统 开发工具:Eclipse/MyEclipse+Jdk+Tomcat+MySQL数据库 运行效果图: 此源码经 ...

随机推荐

- P4718 [模板]Pollard-Rho算法

对一个大质数进行质因数分解 需要引用miller-robin来判素数 一直写的gcd居然挂掉了... 以后用__gcd了 #include <bits/stdc++.h> using na ...

- 【noi 2.6_9267】核电站(DP)

题意:n个数中不能同时选连续m个或以上,问方案数. 解法:f[i][j]表示从前i个中选,到第i个已经连续选了j个.j!=0时, =f[i-1][j-1] ; j=0时, =f[i-1][0~m-1 ...

- Codeforces Round #552 (Div. 3) C. Gourmet Cat (数学,模拟)

题意:你要带着你的喵咪一起去旅行,你的喵在星期\(1,4,7\)吃喵粮\(x\),在星期\(2,6\)吃喵粮\(y\),在星期\(3,5\)吃喵粮\(z\),你只有\(a\)个\(x\),\(b\)个 ...

- Codeforces Round #345 (Div. 1) A. Watchmen (数学,map)

题意:给你\(n\)个点,求这\(n\)个点中,曼哈顿距离和欧几里得距离相等的点对数. 题解: 不难发现,当两个点的曼哈顿距离等于欧几里得距离的时候它们的横坐标或者纵坐标至少有一个相同,可以在纸上画一 ...

- Smith Numbers POJ - 1142 暴力递归枚举

题意: 给你一个数x,把这个分解成素数之积(假设是x1*x2*x3),如果 x的每一数位的和 等于 x1每一数位的和加上x2每一数位的和加上x3每一数位的和,那么他就是题目要找的数 示例: ...

- CF1463-A. Dungeon

题意: 你面前有三个怪物,他们分别有a, b, c点血量.现在你可以指定一个怪物,用大炮向他们射击,之后该怪物就会掉一滴血.每七次射击就会使得炮弹威力加强一次,即第7, 14, 21次射击的时候炮弹威 ...

- k8s二进制部署 - harbor安装

harbor安装 # 目录说明: # /opt/src : 源码.文件下载目录 # /opt/release : 各个版本软件存放位置 # /opt/apps : 各个软件当前版本的软链接 [root ...

- While & For 循环

While 循环 可以将 While 循环称为 "条件循环" While 循环语法 # 条件为 true 就执行循环体代码,条件变为 false 循环结束 while 条件 do ...

- IFIX 目录结构

iFIX使用了许多目录存储程序和数据文件.用路径配置对话框来指定iFIX目录的位置和名称.可在SCU工具箱中单击"路径"按钮显示该对话框. 当iFIX安装后它将创建一个目录,该目录 ...

- 关于free和delete的使用

上一篇篇幅太长,这里再区分free和delete的用法. 两个同时存在是有它的原因的,我们前面说过,free是函数,它只释放内存,但不会调用析构函数,如果用free去释放new申请的空间,会因为无法调 ...