am335x mux配置

/****************************************************************

* am335x mux配置

*

* am335x的引脚复寄存器是CONTROL_MODULE Register(芯片手册Chapter 9)

* 本文主要分析板级文件中如何实现复用。

*

* 参考链接:

* http://blog.chinaunix.net/uid-29745891-id-4348350.html

*

* Tony Liu, 2016-4-30, Shenzhen

*****************************************************************/ MACHINE_START(AM335XEVM, "am335xevm")

/* Maintainer: Texas Instruments */

.atag_offset = 0x100,

.map_io = am335x_evm_map_io,

.init_early = am33xx_init_early,

.init_irq = ti81xx_init_irq,

.handle_irq = omap3_intc_handle_irq,

.timer = &omap3_am33xx_timer,

.init_machine = am335x_evm_init, ------+

MACHINE_END |

|

static void __init am335x_evm_init(void) <----+

{

am33xx_cpuidle_init();

am33xx_mux_init(board_mux); ---------------------------+

omap_serial_init(); |

am335x_evm_i2c_init(); |

omap_sdrc_init(NULL, NULL); |

usb_musb_init(&musb_board_data); |

|

omap_board_config = am335x_evm_config; |

omap_board_config_size = ARRAY_SIZE(am335x_evm_config); |

...... |

} |

|

static struct omap_board_mux board_mux[] __initdata = { |

AM33XX_MUX(XDMA_EVENT_INTR0, OMAP_MUX_MODE3 | AM33XX_PIN_OUTPUT), |

AM33XX_MUX(I2C0_SDA, OMAP_MUX_MODE0 | AM33XX_SLEWCTRL_SLOW | |

AM33XX_INPUT_EN | AM33XX_PIN_OUTPUT), |

AM33XX_MUX(I2C0_SCL, OMAP_MUX_MODE0 | AM33XX_SLEWCTRL_SLOW | |

AM33XX_INPUT_EN | AM33XX_PIN_OUTPUT), |

{ .reg_offset = OMAP_MUX_TERMINATOR }, |

}; |

|

#define AM33XX_MUX(mode0, mux_value) \ |

{ \ |

.reg_offset = (AM33XX_CONTROL_PADCONF_##mode0##_OFFSET), \ |

.value = (((mux_value) & AM33XX_INPUT_EN) ? (mux_value)\ |

: ((mux_value) | AM33XX_PULL_DISA)), \ |

} |

以I2C为例,对上面的宏进行展开 |

AM33XX_MUX(I2C0_SDA, OMAP_MUX_MODE0 | AM33XX_SLEWCTRL_SLOW | |

AM33XX_INPUT_EN | AM33XX_PIN_OUTPUT), |

{ |

.reg_offset = AM33XX_CONTROL_PADCONF_I2C0_SDA_OFFSET, |

.value = I2C0_SDA, OMAP_MUX_MODE0 | AM33XX_SLEWCTRL_SLOW | |

AM33XX_INPUT_EN | AM33XX_PIN_OUTPUT, |

} |

|

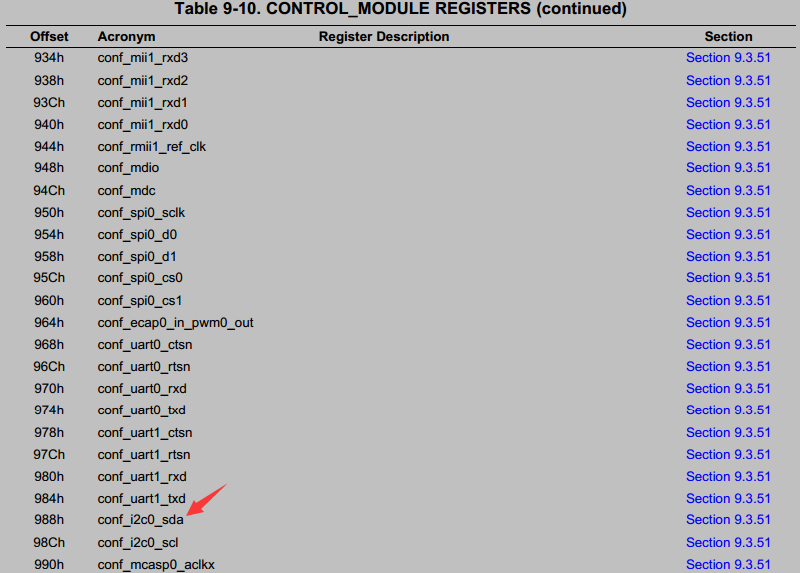

// I2C0_SDA在CONTROL_MODULE的地址 |

#define AM33XX_CONTROL_PADCONF_I2C0_SDA_OFFSET 0x0988 |

// arch/arm/mach-omap2/mux33xx.c |

int __init am33xx_mux_init(struct omap_board_mux *board_subset) <---+

{

return omap_mux_init("core", , AM33XX_CONTROL_PADCONF_MUX_PBASE, --+

AM33XX_CONTROL_PADCONF_MUX_SIZE, am33xx_muxmodes, |

NULL, board_subset, NULL); |

} |

//CONTROL_MODULE寄存器地址 |

#define AM33XX_CONTROL_PADCONF_MUX_PBASE 0x44E10000LU |

|

int __init omap_mux_init(const char *name, u32 flags, <------+

u32 mux_pbase, u32 mux_size,

struct omap_mux *superset,

struct omap_mux *package_subset,

struct omap_board_mux *board_mux,

struct omap_ball *package_balls)

{

struct omap_mux_partition *partition; partition = kzalloc(sizeof(struct omap_mux_partition), GFP_KERNEL);

if (!partition)

return -ENOMEM; partition->name = name;

partition->flags = flags;

partition->size = mux_size;

partition->phys = mux_pbase;

partition->base = ioremap(mux_pbase, mux_size);

if (!partition->base) {

pr_err("%s: Could not ioremap mux partition at 0x%08x\n",

__func__, partition->phys);

kfree(partition);

return -ENODEV;

} INIT_LIST_HEAD(&partition->muxmodes); list_add_tail(&partition->node, &mux_partitions);

mux_partitions_cnt++;

pr_info("%s: Add partition: #%d: %s, flags: %x\n", __func__,

mux_partitions_cnt, partition->name, partition->flags); omap_mux_init_package(superset, package_subset, package_balls);

omap_mux_init_list(partition, superset);

omap_mux_init_signals(partition, board_mux); return ;

}

// arch/arm/mach-omap2/mux33xx.c

/* 每个引脚最多右8中功能,都写在下面的结构体数组中

* 所有引脚复用配置都会和这个结构体数组进行比对

* 可以参考我上一篇文章am335x gpio中,关于配置引脚作为GPIO的部分

*/

#define _AM33XX_MUXENTRY(M0, g, m0, m1, m2, m3, m4, m5, m6, m7) \

{ \

.reg_offset = (AM33XX_CONTROL_PADCONF_##M0##_OFFSET), \

.gpio = (g), \

.muxnames = { m0, m1, m2, m3, m4, m5, m6, m7 }, \

} static struct omap_mux am33xx_muxmodes[] = {

_AM33XX_MUXENTRY(GPMC_AD0, ,

"gpmc_ad0", "mmc1_dat0", NULL, NULL,

NULL, NULL, NULL, "gpio1_0"),

_AM33XX_MUXENTRY(GPMC_AD1, ,

"gpmc_ad1", "mmc1_dat1", NULL, NULL,

NULL, NULL, NULL, "gpio1_1"),

_AM33XX_MUXENTRY(GPMC_AD2, ,

"gpmc_ad2", "mmc1_dat2", NULL, NULL,

NULL, NULL, NULL, "gpio1_2"),

_AM33XX_MUXENTRY(GPMC_AD3, ,

"gpmc_ad3", "mmc1_dat3", NULL, NULL,

NULL, NULL, NULL, "gpio1_3"),

_AM33XX_MUXENTRY(GPMC_AD4, ,

"gpmc_ad4", "mmc1_dat4", NULL, NULL,

NULL, NULL, NULL, "gpio1_4"),

_AM33XX_MUXENTRY(GPMC_AD5, ,

"gpmc_ad5", "mmc1_dat5", NULL, NULL,

NULL, NULL, NULL, "gpio1_5"),

_AM33XX_MUXENTRY(GPMC_AD6, ,

"gpmc_ad6", "mmc1_dat6", NULL, NULL,

NULL, NULL, NULL, "gpio1_6"),

_AM33XX_MUXENTRY(GPMC_AD7, ,

"gpmc_ad7", "mmc1_dat7", NULL, NULL,

NULL, NULL, NULL, "gpio1_7"),

_AM33XX_MUXENTRY(GPMC_AD8, ,

"gpmc_ad8", "lcd_data23", "mmc1_dat0", "mmc2_dat4",

NULL, NULL, NULL, "gpio0_22"),

_AM33XX_MUXENTRY(GPMC_AD9, ,

"gpmc_ad9", "lcd_data22", "mmc1_dat1", "mmc2_dat5",

"ehrpwm2B", NULL, NULL, "gpio0_23"),

_AM33XX_MUXENTRY(GPMC_AD10, ,

"gpmc_ad10", "lcd_data21", "mmc1_dat2", "mmc2_dat6",

NULL, NULL, NULL, "gpio0_26"),

_AM33XX_MUXENTRY(GPMC_AD11, ,

"gpmc_ad11", "lcd_data20", "mmc1_dat3", "mmc2_dat7",

NULL, NULL, NULL, "gpio0_27"),

_AM33XX_MUXENTRY(GPMC_AD12, ,

"gpmc_ad12", "lcd_data19", "mmc1_dat4", "mmc2_dat0",

NULL, NULL, NULL, "gpio1_12"),

_AM33XX_MUXENTRY(GPMC_AD13, ,

"gpmc_ad13", "lcd_data18", "mmc1_dat5", "mmc2_dat1",

NULL, NULL, NULL, "gpio1_13"),

_AM33XX_MUXENTRY(GPMC_AD14, ,

"gpmc_ad14", "lcd_data17", "mmc1_dat6", "mmc2_dat2",

NULL, NULL, NULL, "gpio1_14"),

_AM33XX_MUXENTRY(GPMC_AD15, ,

"gpmc_ad15", "lcd_data16", "mmc1_dat7", "mmc2_dat3",

NULL, NULL, NULL, "gpio1_15"),

_AM33XX_MUXENTRY(GPMC_A0, ,

"gpmc_a0", "mii2_txen", "rgmii2_tctl", "rmii2_txen",

NULL, NULL, NULL, "gpio1_16"),

_AM33XX_MUXENTRY(GPMC_A1, ,

"gpmc_a1", "mii2_rxdv", "rgmii2_rctl", "mmc2_dat0",

NULL, NULL, NULL, "gpio1_17"),

_AM33XX_MUXENTRY(GPMC_A2, ,

"gpmc_a2", "mii2_txd3", "rgmii2_td3", "mmc2_dat1",

NULL, NULL, "ehrpwm1A", "gpio1_18"),

_AM33XX_MUXENTRY(GPMC_A3, ,

"gpmc_a3", "mii2_txd2", "rgmii2_td2", "mmc2_dat2",

NULL, NULL, NULL, "gpio1_19"),

_AM33XX_MUXENTRY(GPMC_A4, ,

"gpmc_a4", "mii2_txd1", "rgmii2_td1", "rmii2_txd1",

"gpmc_a20", NULL, NULL, "gpio1_20"),

_AM33XX_MUXENTRY(GPMC_A5, ,

"gpmc_a5", "mii2_txd0", "rgmii2_td0", "rmii2_txd0",

"gpmc_a21", NULL, NULL, "gpio1_21"),

_AM33XX_MUXENTRY(GPMC_A6, ,

"gpmc_a6", "mii2_txclk", "rgmii2_tclk", "mmc2_dat4",

"gpmc_a22", NULL, NULL, "gpio1_22"),

_AM33XX_MUXENTRY(GPMC_A7, ,

"gpmc_a7", "mii2_rxclk", "rgmii2_rclk", "mmc2_dat5",

NULL, NULL, NULL, "gpio1_23"),

_AM33XX_MUXENTRY(GPMC_A8, ,

"gpmc_a8", "mii2_rxd3", "rgmii2_rd3", "mmc2_dat6",

NULL, NULL, "mcasp0_aclkx", "gpio1_24"),

_AM33XX_MUXENTRY(GPMC_A9, ,

"gpmc_a9", "mii2_rxd2", "rgmii2_rd2", "mmc2_dat7",

NULL, NULL, "mcasp0_fsx", "gpio1_25"),

_AM33XX_MUXENTRY(GPMC_A10, ,

"gpmc_a10", "mii2_rxd1", "rgmii2_rd1", "rmii2_rxd1",

NULL, NULL, "mcasp0_axr0", "gpio1_26"),

_AM33XX_MUXENTRY(GPMC_A11, ,

"gpmc_a11", "mii2_rxd0", "rgmii2_rd0", "rmii2_rxd0",

NULL, NULL, "mcasp0_axr1", "gpio1_27"),

_AM33XX_MUXENTRY(GPMC_WAIT0, ,

"gpmc_wait0", "mii2_crs", NULL, "rmii2_crs_dv",

"mmc1_sdcd", NULL, NULL, "gpio0_30"),

_AM33XX_MUXENTRY(GPMC_WPN, ,

"gpmc_wpn", "mii2_rxerr", NULL, "rmii2_rxerr",

"mmc2_sdcd", NULL, NULL, "gpio0_31"),

_AM33XX_MUXENTRY(GPMC_BEN1, ,

"gpmc_ben1", "mii2_col", NULL, "mmc2_dat3",

NULL, NULL, "mcasp0_aclkr", "gpio1_28"),

_AM33XX_MUXENTRY(GPMC_CSN0, ,

"gpmc_csn0", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio1_29"),

_AM33XX_MUXENTRY(GPMC_CSN1, ,

"gpmc_csn1", NULL, "mmc1_clk", NULL,

NULL, NULL, NULL, "gpio1_30"),

_AM33XX_MUXENTRY(GPMC_CSN2, ,

"gpmc_csn2", NULL, "mmc1_cmd", NULL,

NULL, NULL, NULL, "gpio1_31"),

_AM33XX_MUXENTRY(GPMC_CSN3, ,

"gpmc_csn3", NULL, NULL, "mmc2_cmd",

NULL, NULL, NULL, "gpio2_0"),

_AM33XX_MUXENTRY(GPMC_CLK, ,

"gpmc_clk", "lcd_memory_clk_mux", NULL, "mmc2_clk",

NULL, NULL, "mcasp0_fsr", "gpio2_1"),

_AM33XX_MUXENTRY(GPMC_ADVN_ALE, ,

"gpmc_advn_ale", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_2"),

_AM33XX_MUXENTRY(GPMC_OEN_REN, ,

"gpmc_oen_ren", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_3"),

_AM33XX_MUXENTRY(GPMC_WEN, ,

"gpmc_wen", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_4"),

_AM33XX_MUXENTRY(GPMC_BEN0_CLE, ,

"gpmc_ben0_cle", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_5"),

_AM33XX_MUXENTRY(LCD_DATA0, ,

"lcd_data0", "gpmc_a0", NULL, NULL,

NULL, NULL, NULL, "gpio2_6"),

_AM33XX_MUXENTRY(LCD_DATA1, ,

"lcd_data1", "gpmc_a1", NULL, NULL,

NULL, NULL, NULL, "gpio2_7"),

_AM33XX_MUXENTRY(LCD_DATA2, ,

"lcd_data2", "gpmc_a2", NULL, NULL,

NULL, NULL, NULL, "gpio2_8"),

_AM33XX_MUXENTRY(LCD_DATA3, ,

"lcd_data3", "gpmc_a3", NULL, NULL,

NULL, NULL, NULL, "gpio2_9"),

_AM33XX_MUXENTRY(LCD_DATA4, ,

"lcd_data4", "gpmc_a4", NULL, NULL,

NULL, NULL, NULL, "gpio2_10"),

_AM33XX_MUXENTRY(LCD_DATA5, ,

"lcd_data5", "gpmc_a5", NULL, NULL,

NULL, NULL, NULL, "gpio2_11"),

_AM33XX_MUXENTRY(LCD_DATA6, ,

"lcd_data6", "gpmc_a6", NULL, NULL,

NULL, NULL, NULL, "gpio2_12"),

_AM33XX_MUXENTRY(LCD_DATA7, ,

"lcd_data7", "gpmc_a7", NULL, NULL,

NULL, NULL, NULL, "gpio2_13"),

_AM33XX_MUXENTRY(LCD_DATA8, ,

"lcd_data8", "gpmc_a12", NULL, "mcasp0_aclkx",

NULL, NULL, "uart2_ctsn", "gpio2_14"),

_AM33XX_MUXENTRY(LCD_DATA9, ,

"lcd_data9", "gpmc_a13", NULL, "mcasp0_fsx",

NULL, NULL, "uart2_rtsn", "gpio2_15"),

_AM33XX_MUXENTRY(LCD_DATA10, ,

"lcd_data10", "gpmc_a14", NULL, "mcasp0_axr0",

NULL, NULL, NULL, "gpio2_16"),

_AM33XX_MUXENTRY(LCD_DATA11, ,

"lcd_data11", "gpmc_a15", NULL, "mcasp0_ahclkr",

"mcasp0_axr2", NULL, NULL, "gpio2_17"),

_AM33XX_MUXENTRY(LCD_DATA12, ,

"lcd_data12", "gpmc_a16", NULL, "mcasp0_aclkr",

"mcasp0_axr2", NULL, NULL, "gpio0_8"),

_AM33XX_MUXENTRY(LCD_DATA13, ,

"lcd_data13", "gpmc_a17", NULL, "mcasp0_fsr",

"mcasp0_axr3", NULL, NULL, "gpio0_9"),

_AM33XX_MUXENTRY(LCD_DATA14, ,

"lcd_data14", "gpmc_a18", NULL, "mcasp0_axr1",

NULL, NULL, NULL, "gpio0_10"),

_AM33XX_MUXENTRY(LCD_DATA15, ,

"lcd_data15", "gpmc_a19", NULL, "mcasp0_ahclkx",

"mcasp0_axr3", NULL, NULL, "gpio0_11"),

_AM33XX_MUXENTRY(LCD_VSYNC, ,

"lcd_vsync", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_22"),

_AM33XX_MUXENTRY(LCD_HSYNC, ,

"lcd_hsync", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_23"),

_AM33XX_MUXENTRY(LCD_PCLK, ,

"lcd_pclk", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_24"),

_AM33XX_MUXENTRY(LCD_AC_BIAS_EN, ,

"lcd_ac_bias_en", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_25"),

_AM33XX_MUXENTRY(MMC0_DAT3, ,

"mmc0_dat3", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_26"),

_AM33XX_MUXENTRY(MMC0_DAT2, ,

"mmc0_dat2", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_27"),

_AM33XX_MUXENTRY(MMC0_DAT1, ,

"mmc0_dat1", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_28"),

_AM33XX_MUXENTRY(MMC0_DAT0, ,

"mmc0_dat0", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_29"),

_AM33XX_MUXENTRY(MMC0_CLK, ,

"mmc0_clk", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_30"),

_AM33XX_MUXENTRY(MMC0_CMD, ,

"mmc0_cmd", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio2_31"),

_AM33XX_MUXENTRY(MII1_COL, ,

"mii1_col", "rmii2_refclk", "spi1_sclk", NULL,

"mcasp1_axr2", "mmc2_dat3", "mcasp0_axr2", "gpio3_0"),

_AM33XX_MUXENTRY(MII1_CRS, ,

"mii1_crs", "rmii1_crs_dv", "spi1_d0", "i2c1_sda",

"mcasp1_aclkx", NULL, NULL, "gpio3_1"),

_AM33XX_MUXENTRY(MII1_RXERR, ,

"mii1_rxerr", "rmii1_rxerr", "spi1_d1", "i2c1_scl",

"mcasp1_fsx", NULL, NULL, "gpio3_2"),

_AM33XX_MUXENTRY(MII1_TXEN, ,

"mii1_txen", "rmii1_txen", "rgmii1_tctl", NULL,

"mcasp1_axr0", NULL, "mmc2_cmd", "gpio3_3"),

_AM33XX_MUXENTRY(MII1_RXDV, ,

"mii1_rxdv", NULL, "rgmii1_rctl", NULL,

"mcasp1_aclx", "mmc2_dat0", "mcasp0_aclkr", "gpio3_4"),

_AM33XX_MUXENTRY(MII1_TXD3, ,

"mii1_txd3", NULL, "rgmii1_td3", NULL,

"mcasp1_fsx", "mmc2_dat1", "mcasp0_fsr", "gpio0_16"),

_AM33XX_MUXENTRY(MII1_TXD2, ,

"mii1_txd2", NULL, "rgmii1_td2", NULL,

"mcasp1_axr0", "mmc2_dat2", "mcasp0_ahclkx", "gpio0_17"),

_AM33XX_MUXENTRY(MII1_TXD1, ,

"mii1_txd1", "rmii1_txd1", "rgmii1_td1", "mcasp1_fsr",

"mcasp1_axr1", NULL, "mmc1_cmd", "gpio0_21"),

_AM33XX_MUXENTRY(MII1_TXD0, ,

"mii1_txd0", "rmii1_txd0", "rgmii1_td0", "mcasp1_axr2",

"mcasp1_aclkr", NULL, "mmc1_clk", "gpio0_28"),

_AM33XX_MUXENTRY(MII1_TXCLK, ,

"mii1_txclk", NULL, "rgmii1_tclk", "mmc0_dat7",

"mmc1_dat0", NULL, "mcasp0_aclkx", "gpio3_9"),

_AM33XX_MUXENTRY(MII1_RXCLK, ,

"mii1_rxclk", NULL, "rgmii1_rclk", "mmc0_dat6",

"mmc1_dat1", NULL, "mcasp0_fsx", "gpio3_10"),

_AM33XX_MUXENTRY(MII1_RXD3, ,

"mii1_rxd3", NULL, "rgmii1_rd3", "mmc0_dat5",

"mmc1_dat2", NULL, "mcasp0_axr0", "gpio2_18"),

_AM33XX_MUXENTRY(MII1_RXD2, ,

"mii1_rxd2", NULL, "rgmii1_rd2", "mmc0_dat4",

"mmc1_dat3", NULL, "mcasp0_axr1", "gpio2_19"),

_AM33XX_MUXENTRY(MII1_RXD1, ,

"mii1_rxd1", "rmii1_rxd1", "rgmii1_rd1", "mcasp1_axr3",

"mcasp1_fsr", NULL, "mmc2_clk", "gpio2_20"),

_AM33XX_MUXENTRY(MII1_RXD0, ,

"mii1_rxd0", "rmii1_rxd0", "rgmii1_rd0", "mcasp1_ahclkx",

"mcasp1_ahclkr", "mcasp1_aclkr", "mcasp0_axr3", "gpio2_21"),

_AM33XX_MUXENTRY(MII1_REFCLK, ,

"rmii1_refclk", NULL, "spi1_cs0", NULL,

"mcasp1_axr3", "mmc0_pow", "mcasp1_ahclkx", "gpio0_29"),

_AM33XX_MUXENTRY(MDIO_DATA, ,

"mdio_data", NULL, NULL, NULL,

"mmc0_sdcd", "mmc1_cmd", "mmc2_cmd", "gpio0_0"),

_AM33XX_MUXENTRY(MDIO_CLK, ,

"mdio_clk", NULL, NULL, NULL,

"mmc0_sdwp", "mmc1_clk", "mmc2_clk", "gpio0_1"),

_AM33XX_MUXENTRY(SPI0_SCLK, ,

"spi0_sclk", "uart2_rxd", "i2c2_sda", NULL,

NULL, NULL, NULL, "gpio0_2"),

_AM33XX_MUXENTRY(SPI0_D0, ,

"spi0_d0", "uart2_txd", "i2c2_scl", NULL,

NULL, NULL, NULL, "gpio0_3"),

_AM33XX_MUXENTRY(SPI0_D1, ,

"spi0_d1", "mmc1_sdwp", "i2c1_sda", NULL,

NULL, NULL, NULL, "gpio0_4"),

_AM33XX_MUXENTRY(SPI0_CS0, ,

"spi0_cs0", "mmc2_sdwp", "i2c1_scl", NULL,

NULL, NULL, NULL, "gpio0_5"),

_AM33XX_MUXENTRY(SPI0_CS1, ,

//"spi0_cs1", "uart3_rxd", NULL, "mmc0_pow",

"spi0_cs1", "uart3_rxd", "ecap1_in_pwm1_out", "mmc0_pow",

NULL, "mmc0_sdcd", NULL, "gpio0_6"),

_AM33XX_MUXENTRY(ECAP0_IN_PWM0_OUT, ,

"ecap0_in_pwm0_out", "uart3_txd", "spi1_cs1", NULL,

"spi1_sclk", "mmc0_sdwp", "xdma_event_intr2", "gpio0_7"),

_AM33XX_MUXENTRY(UART0_CTSN, ,

"uart0_ctsn", "uart4_rxd", "d_can1_tx", "i2c1_sda",

"spi1_d0", NULL, NULL, "gpio1_8"),

_AM33XX_MUXENTRY(UART0_RTSN, ,

"uart0_rtsn","uart4_txd", "d_can1_rx", "i2c1_scl",

"spi1_d1", "spi1_cs0", NULL, "gpio1_9"),

_AM33XX_MUXENTRY(UART0_RXD, ,

"uart0_rxd", "spi1_cs0", "d_can0_tx", "i2c2_sda",

NULL, NULL, NULL, "gpio1_10"),

_AM33XX_MUXENTRY(UART0_TXD, ,

"uart0_txd", "spi1_cs1", "d_can0_rx", "i2c2_scl",

NULL, NULL, NULL, "gpio1_11"),

_AM33XX_MUXENTRY(UART1_CTSN, ,

"uart1_ctsn", NULL, "d_can0_tx", "i2c2_sda",

"spi1_cs0", NULL, NULL, "gpio0_12"),

_AM33XX_MUXENTRY(UART1_RTSN, ,

"uart1_rtsn", NULL, "d_can0_rx", "i2c2_scl",

"spi1_cs1", NULL, NULL, "gpio0_13"),

_AM33XX_MUXENTRY(UART1_RXD, ,

"uart1_rxd", "mmc1_sdwp", NULL, "i2c1_sda",

NULL, "pr1_uart0_rxd_mux1", NULL, "gpio0_14"),

_AM33XX_MUXENTRY(UART1_TXD, ,

"uart1_txd", "mmc2_sdwp", NULL, "i2c1_scl",

NULL, "pr1_uart0_txd_mux1", NULL, "gpio0_15"),

_AM33XX_MUXENTRY(I2C0_SDA, ,

"i2c0_sda", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio3_5"),

_AM33XX_MUXENTRY(I2C0_SCL, ,

"i2c0_scl", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio3_6"),

_AM33XX_MUXENTRY(MCASP0_ACLKX, ,

"mcasp0_aclkx", "ehrpwm0a", NULL, "spi1_sclk",

"mmc0_sdcd", NULL, NULL, "gpio3_14"),

_AM33XX_MUXENTRY(MCASP0_FSX, ,

"mcasp0_fsx", NULL, NULL, "spi1_d0",

"mmc1_sdcd", NULL, NULL, "gpio3_15"),

_AM33XX_MUXENTRY(MCASP0_AXR0, ,

"mcasp0_axr0", NULL, NULL, "spi1_d1",

"mmc2_sdcd", NULL, NULL, "gpio3_16"),

_AM33XX_MUXENTRY(MCASP0_AHCLKR, ,

"mcasp0_ahclkr", NULL, "mcasp0_axr2", "spi1_cs0",

"ecap2_in_pwm2_out", NULL, NULL, "gpio3_17"),

_AM33XX_MUXENTRY(MCASP0_ACLKR, ,

"mcasp0_aclkr", NULL, "mcasp0_axr2", "mcasp1_aclkx",

"mmc0_sdwp", NULL, NULL, "gpio3_18"),

_AM33XX_MUXENTRY(MCASP0_FSR, ,

"mcasp0_fsr", NULL, "mcasp0_axr3", "mcasp1_fsx",

NULL, "pr1_pru0_pru_r30_5", NULL, "gpio3_19"),

_AM33XX_MUXENTRY(MCASP0_AXR1, ,

"mcasp0_axr1", NULL, NULL, "mcasp1_axr0",

NULL, NULL, NULL, "gpio3_20"),

_AM33XX_MUXENTRY(MCASP0_AHCLKX, ,

"mcasp0_ahclkx", NULL, "mcasp0_axr3", "mcasp1_axr1",

NULL, NULL, NULL, "gpio3_21"),

_AM33XX_MUXENTRY(XDMA_EVENT_INTR0, ,

"xdma_event_intr0", NULL, NULL, "clkout1",

"spi1_cs1", NULL, NULL, "gpio0_19"),

_AM33XX_MUXENTRY(XDMA_EVENT_INTR1, ,

"xdma_event_intr1", NULL, NULL, "clkout2",

NULL, NULL, NULL, "gpio0_20"),

_AM33XX_MUXENTRY(WARMRSTN, ,

"warmrstn", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(NMIN, ,

"nmin", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(TMS, ,

"tms", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(TDI, ,

"tdi", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(TDO, ,

"tdo", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(TCK, ,

"tck", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(TRSTN, ,

"trstn", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(EMU0, ,

"emu0", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio3_7"),

_AM33XX_MUXENTRY(EMU1, ,

"emu1", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio3_8"),

_AM33XX_MUXENTRY(RTC_PWRONRSTN, ,

"rtc_pwronrstn", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(PMIC_POWER_EN, ,

"pmic_power_en", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(EXT_WAKEUP, ,

"ext_wakeup", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(RTC_KALDO_ENN, ,

"rtc_kaldo_enn", NULL, NULL, NULL,

NULL, NULL, NULL, NULL),

_AM33XX_MUXENTRY(USB0_DRVVBUS, ,

"usb0_drvvbus", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio0_18"),

_AM33XX_MUXENTRY(USB1_DRVVBUS, ,

"usb1_drvvbus", NULL, NULL, NULL,

NULL, NULL, NULL, "gpio3_13"),

{ .reg_offset = OMAP_MUX_TERMINATOR },

};

手册中的描述举例:

寄存器参考手册:

am335x mux配置的更多相关文章

- am335x Lan8710a 双网口配置

一. 经过调试, LAN8710A在 am335x 上面需要使用 GMII的模式,设备树 pin mux配置如下: // 下面是工作模式的配置,在睡眠模式下是配成GPIO模式 162 cpsw_def ...

- AM335x(TQ335x)学习笔记——u-boot-2014.10移植

根据最近移植u-boot-2014.10至TQ335x,基于这样的假设am335x evm移植.不是很多地方需要改变. 因为TI的am335x evm开发了使用eeprom船上保存配置信息.它使用不同 ...

- AM335X启动(转)

AM335x启动 参考文件: 1.TI.Reference_Manual_1.pdf http://pan.baidu.com/s/1c1BJNtm 2.TI_AM335X.pdf http:// ...

- AM335x启动

参考文件: 1.TI.Reference_Manual_1.pdf http://pan.baidu.com/s/1c1BJNtm 2.TI_AM335X.pdf http://pan.baidu.c ...

- am335x system upgrade uboot nand boot(三)

在uboot 下初始化nand,一般需要做如下工作: 第一: 配置默认从NAND boot Index: include/configs/am335x_evm.h=================== ...

- [转]uboot中SPI Flash Booting配置

转自:https://e2echina.ti.com/question_answer/dsp_arm/sitara_arm/f/25/t/124834 最近和人一起调试SPI FLASH的配置问题,做 ...

- AM335X UBOOT(以UART为例分析UBOOT主要流程)

UBOOT2016.05 UART初始化及设置 SPL阶段 第一部分C函数 |- s_init //(arch/arm/cpu/armv7/am33xx/board.c) |- set_uart_mu ...

- am335x system upgrade kernel tf(五)

1 Scope of Document This document describes TF hardware design 2 Requiremen 2.1 Functi ...

- u-boot 学习系列 1 - SPL

u-boot这个东西从自我N年前使用到现在,变化好多,今天开始重新研究下,本系列的研究都是基于BeagleBoneBlack(bbb)开发板和 u-boot v201801版本的. SPL介绍 在源代 ...

随机推荐

- Android事件分发机制源代码分析

小小感慨一下,做android有一段时间了,一直以来都是习惯整理笔记存到有道笔记上,没有写博客的习惯. 以后逐步分类整理出来,也算"复习"一遍了 - _ - . android的事 ...

- Token:服务端身份验证的流行方案【转】

01- 身份认证 服务端提供资源给客户端,但是某些资源是有条件的.所以服务端要能够识别请求者的身份,然后再判断所请求的资源是否可以给请求者. token是一种身份验证的机制,初始时用户提交账号数据给服 ...

- java Webservice(一)HttpClient使用(一)

1.拳头之Get/Post拳头是最基本的一重武器,也是最重要的,好比练武之人必须先扎稳马步. java 代码 HttpClient httpclient=new HttpClient();//创建一个 ...

- HLJU 1046: 钓鱼(数据增强版) (贪心+优化)

1046: 钓鱼(数据增强版) Time Limit: 1 Sec Memory Limit: 128 MB Submit: 11 Solved: 3 [id=1046">Subm ...

- [sh]. 点的含义

. 的含义 当前目录 隐藏文件 任意一个字符 生效配置文件

- java NIO中的buffer和channel

缓冲区(Buffer):一,在 Java NIO 中负责数据的存取.缓冲区就是数组.用于存储不同数据类型的数据 根据数据类型不同(boolean 除外),提供了相应类型的缓冲区:ByteBufferC ...

- ViewPager滑动不畅及灵敏度的问题

在项目中用到了Android的ViewPager组件,可是发如今滑动的时候不是特别流畅,有些小的滑动无法响应,于是考虑进行优化. 一開始考虑改动ViewPager中的一些參数.比方mTouchSlop ...

- maven(6)------maven坐标分析

在不使用maven管理项目,直接使用IDE开发项目时,一个web项目中会涉及到很多技术, 比如struts2,hibernate,spring,mybatis等等,这个时候,我们就需要去各大官网下载不 ...

- 编写Spark的WordCount程序并提交到集群运行[含scala和java两个版本]

编写Spark的WordCount程序并提交到集群运行[含scala和java两个版本] 1. 开发环境 Jdk 1.7.0_72 Maven 3.2.1 Scala 2.10.6 Spark 1.6 ...

- JS转换HTML转义符,防止javascript注入攻击,亲测可用

function removeHtmlTab(tab) { return tab.replace(/<[^<>]+?>/g,'');//删除所有HTML标签 } functi ...