intel-FPGA的片内存储器问题

FPGA的片内有很多的存储器资源,可以配置成单端口的ROM、RAM和双端口的ROM、RAM,以及移位寄存器和FIFO等。在学习过程中,笔者遇到过几个小问题,总结如下:

片内是不是有ROM或者RAM?

个人观点:片内没有ROM或者RAM的,有的只是一些功能比较强大的存储器块,可以通过配置变成我们想要的功能。例如将RAM的wren端子和data端子直接接地,那么就变成了ROM。片内有的是一些M9K、M4K等等,M9K代表容量为9Kbits的存储器。

选择组成存储器的类型以及存储器块的最大深度?

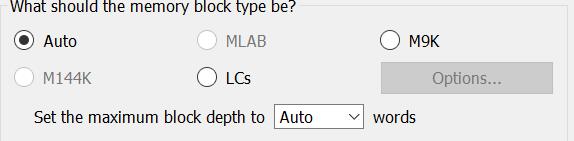

图1

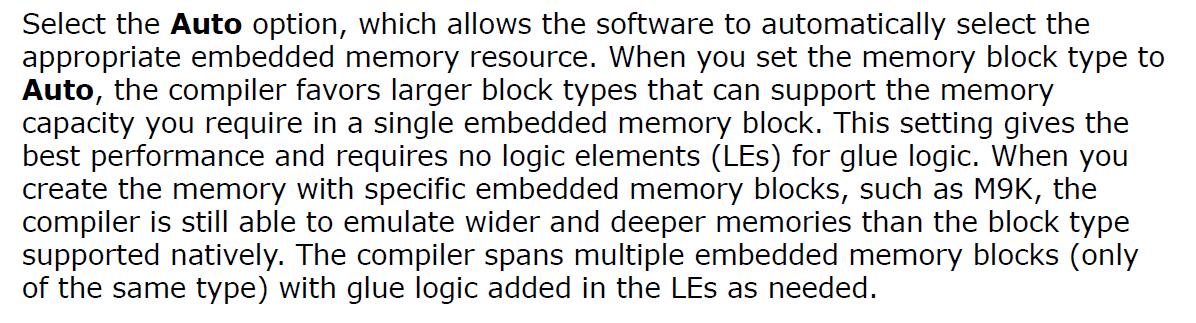

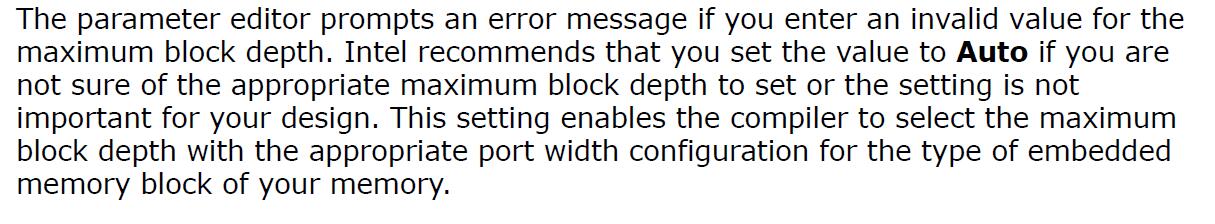

个人观点:对于这两个的话,建议选择“AUTO”。下图是官方给出的建议:

图2

图3

对于RAM和ROM模式,q输出段是否应该被寄存?

个人观点:其实寄存也好,不被寄存也好,结果只是输出的是不是会延迟一个时钟周期。但是笔者建议q应该被寄存一下。在RAM或者ROM中,地址被寄存,而最终的输出是用的组合逻辑进行输出,如果q被引用时也经过了大量的逻辑,那么存储器中的逻辑和被引用时的逻辑就会组成一个比较大的逻辑,整个设计的速度就会变慢。

对于RAM和ROM模式,是否应该引出rden信号?

个人观点:之前我在学习中,rden从来没有引出过,因为自己的设计自己知道,什么时候去读,只要正确的时序就可以了,近期接触到官方文档后,官方推荐引出rden信号,用于降低功耗。

图4

在RAM模式中,如果出现对于同一个地址进行读写会出现什么情况?

图5

个人观点:之前学习中,这个界面几乎从来没有关系过,直接都是略过,保持默认值不变。近期考虑这个问题,查看官方手册,此项可以选择New Data、Old Data和Donot Care,默认值是New Data。

这个问题可以分为两个方向考虑:

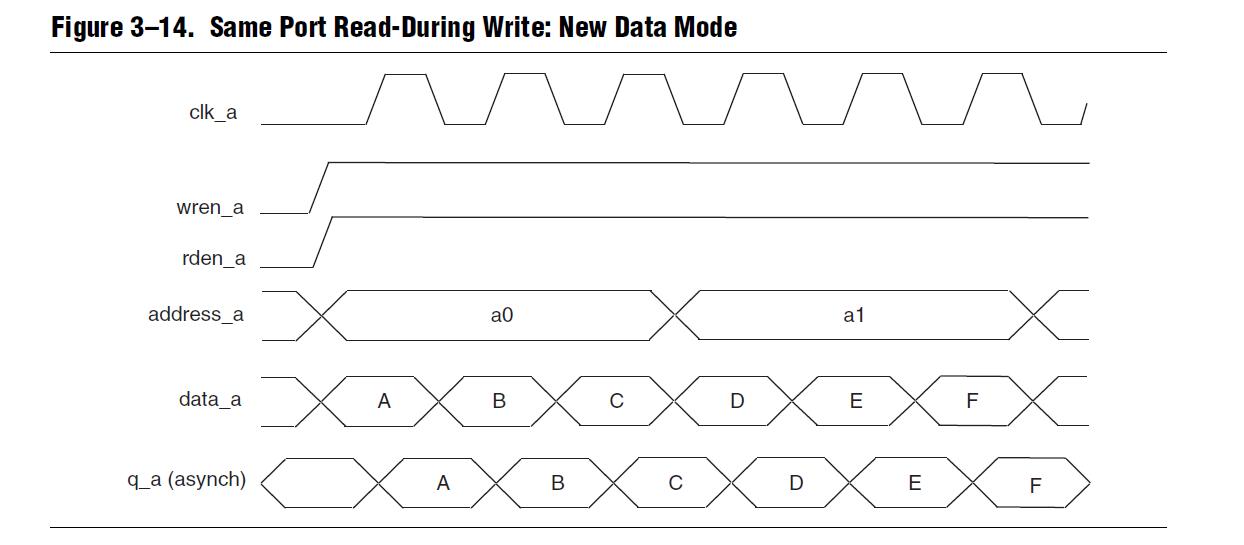

同一个端口同时读写,那么时序如下:

图6

图7

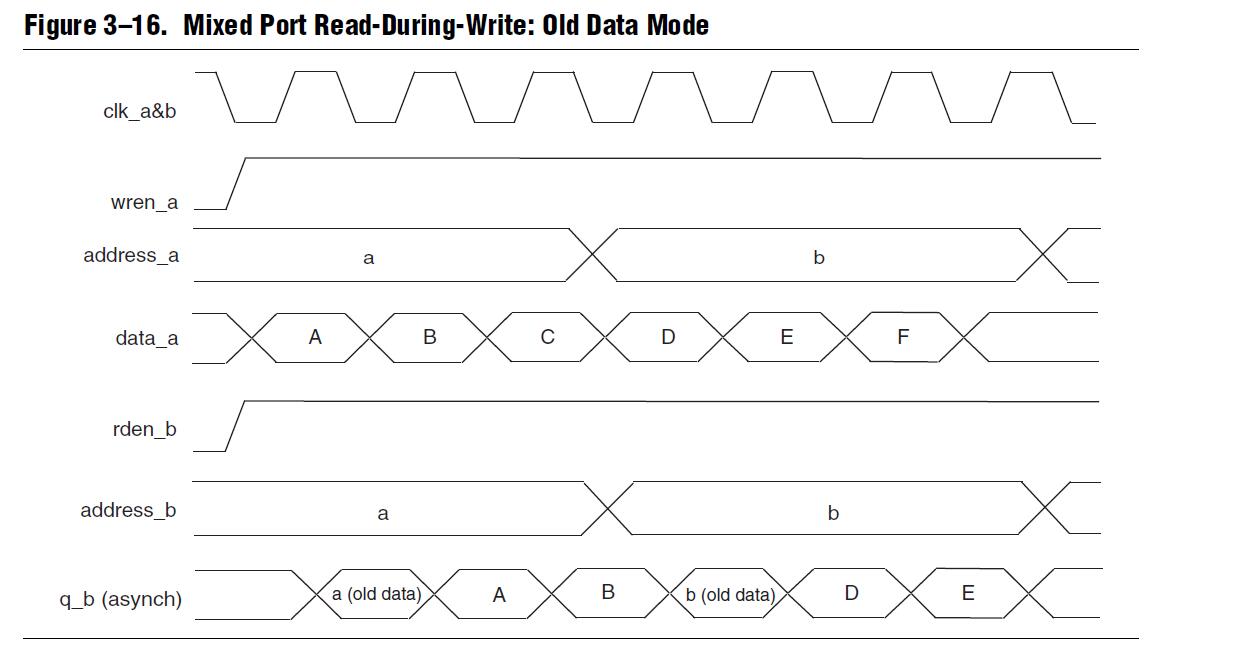

对于不同的端口来说,只有Old DATA,don’t care就不关心了。

图8

对于初始化文件.hex或者.mif文件,当存储器发生写入时,文件内容没有发生改变?

个人观点:.hex或者.mif文件并没有被下板,只是综合器在综合时,将文件中的内容读取出来,配置给存储器而已,本身文件和下板没有关系,所以在仿真也好,或者下板也好,对于存储器的写入并不会改变文件中的值。对于经常使用.txt初始化的设计者,结果也是一样的,.txt的内容并不会被改变。

使用reg [n-1:0] reg_name [m-1:0]定义存储器。

个人观点:此种方法是可以定义存储器的,但是经过笔者实际测试,不同的深度和位宽会影响综合器选择存储器块还是LE构成,并且会综合器在综合过程中会产生很多的警告。笔者在公司研发,使用此种方式进行存储器定义使用,被领导批评过。具体的原因有待发掘,在此,笔者建议设计者在设计时,如果要用到存储器,利用IPCore的插件向导完成还是比较好的。

笔者将上文中所用的存储器官方资料都放到了,QQ群:173560979群文件中,如果有需要的可以下载。

笔者水平有限,如果设计中,有什么不妥的地方,恳请大佬们指出来。

欢迎加好友探讨QQ(奋斗的小孩郝旭帅):746833924,QQ群:173560979。

intel-FPGA的片内存储器问题的更多相关文章

- 关于INTEL FPGA设计工具DSP Builder

一段时间以来,MathWorks一直主张使用Matlab和Simulink开发工具进行基于模型的设计,因为好的设计技术使您能够在更短的时间内开发更高质量的复杂软件.基于模块的设计采用了数学和可视化的方 ...

- 基于INTEL FPGA硬浮点DSP实现卷积运算

概述 卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波.而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络.本参考设计主要介绍如何基于INTEL 硬浮点的DS ...

- Intel FPGA Clock Region概念以及用法

目录 Intel FPGA 的Clock Region概念 Intel 不同系列FPGA 的Clock Region 1. Clock Region Assignments in Intel Stra ...

- OpenCL设计优化(基于Intel FPGA SDK for OpenCL)

1.首先了解Intel FPGA SDK for OpenCL实现OpenCL的设计组件,包括: kernels, global memory interconnect, local memory, ...

- Intel FPGA 专用时钟引脚是否可以用作普通输入,输出或双向IO使用?

原创 by DeeZeng FPGA 的 CLK pin 是否可以用作普通输入 ,输出或双向IO 使用? 这些专用Clock input pin 是否可以当作 inout用,需要看FPGA是否支 ...

- intel FPGA使用

https://www.altera.com/documentation/swn1503506366945.html https://files.cnblogs.com/files/shaohef/o ...

- intel FPGA CLKn pin 是否能直接进PLL?

原创 by DeeZeng FPGA的时钟需要从专用的时钟管脚输入,那CLKn 作为Single-End时钟pin时是否能直接进 PLL呢? 通过查看对应FPGA型号的手册,得出以下结论 1. Cyc ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 如何保证FPGA PCIe唤醒能满足PC的100ms 的时间要求(Autonomous Mode)?

原创By DeeZeng [ Intel FPGA笔记 ] PC 需要PCIe设备在 100ms 内启动,这样PC 才能扫描到PCIe 设备.对于 FPGA PCIe 板卡,同样也需要满足这个时间要 ...

- [RAM] FPGA的学习笔记——RAM

1.RAM——随机存取存储器, 分为SRAM和DRAM. SRAM:存和取得速度快,操作简单.然而,成本高,很难做到很大.FPGA的片内存储器,就是一种SRAM,用来存放程序,以及程序执行过程中,产生 ...

随机推荐

- Apache的配置详解

Apache的配置由httpd.conf文件配置,因此下面的配置指令都是在httpd.conf文件中修改. 主站点的配置(基本配置) (1) 基本配置: ServerRoot "/mnt/s ...

- excel展示

- PHP面试常用算法(推荐)

一.冒泡排序 基本思想: 对需要排序的数组从后往前(逆序)进行多遍的扫描,当发现相邻的两个数值的次序与排序要求的规则不一致时,就将这两个数值进行交换.这样比较小(大)的数值就将逐渐从后面向前面移动. ...

- 性能调优的本质、Spark资源使用原理和调优要点分析

本课主题 大数据性能调优的本质 Spark 性能调优要点分析 Spark 资源使用原理流程 Spark 资源调优最佳实战 Spark 更高性能的算子 引言 我们谈大数据性能调优,到底在谈什么,它的本质 ...

- Git在eclipse中的配置

1:git在eclipse中的配置 windows - >preferences->team->git->configuration 点击add Entry key值:输入 u ...

- python 获取当前目录,上级目录,上上级目录

import os print '***获取当前目录***' print os.getcwd() print os.path.abspath(os.path.dirname(__file__)) pr ...

- less使用总结

15年自学了 less ,可是一直没用,就忘记了.后来抱着提高 css 开发速度的目的,又去学习了 less ,学完马上用,效果立竿见影,记得也牢了.刚开始学习前,我们总会问自己一个问题,学习它有什么 ...

- django创建项目问题解决办法

问题描述: Python编程:从入门到实践第十八章18.1.6 ❶(ll_env)learning_log$ django-admin.py startproject learning_log .❷ ...

- 死磕salt系列-salt入门

saltstack简介 SaltStack是一种新型的基础设施管理软件,简单易部署,可伸缩的足以管理成千上万的服务器,和足够快的速度控制,与他们交流,以毫秒为单位.SaltStack提供了一个动态基础 ...

- [CQOI2017]小Q的表格

题目 神仙题,神仙题 这是一道很适合盯着发呆的题目 看到这个规律 \[ f(a,b)=f(b,a) \] \[ b\times f(a,a+b)=(a+b)\times f(a,b) \] 这也没什么 ...