数字信号处理专题(1)——DDS函数发生器环路Demo

一、前言

会FPGA硬件描述语言、设计思想和接口协议,掌握些基本的算法是非常重要的,因此开设本专题探讨些基于AD DA数字信号处理系统的一些简单算法,在数字通信 信号分析与检测等领域都会或多或少有应用。我们还是从老生常谈的DDS函数发生器开始,讲解DAC ADC基本使用以及DDS算法原理与设计方式。

二、设计预期

功能:基于ROM的频率可调DDS正弦函数发生器

DAC ADC型号与设计参数:DAC为AD9708,更新速率125MSPS,精度8bit;ADC为AD9280,采样率32MSPS,精度8bit。由于ADC采样率限制,设计使用32MHZ频率时钟更新与采样数据,并将ROM深度定义为1024.

验证手段:MATLAB产生正弦函数,经过8bit量化后存储在ROM中,数据经过DAC 电缆 ADC环回到FPGA,ILA抓取ADC接收数据波形,观察对比发送与接收数据是否相近。

三、DDS原理

这里只介绍DDS的基本思想,关于详细原理,请参考:【图文】DDS原理_百度文库 https://wenku.baidu.com/view/11cfbf85a0116c175f0e4818.html

实际上,DDS的核心就是将正弦或余弦函数存储在ROM中,利用相位累加特性通过采用不同的步长对ROM寻址的方式产生频率可调正弦波。另外需要注意产生信号的频率范围要满足奈奎斯特采样定理,该定理支持若想无失真恢复原始信号,采样频率必须大于等于信号最高频率成分的2倍。反过来说:产生信号的最高频率小于等于采样率的1/2.采样频率即为FPGA是时钟频率。为防止信号混叠,一般取最高频率成分的1/3.

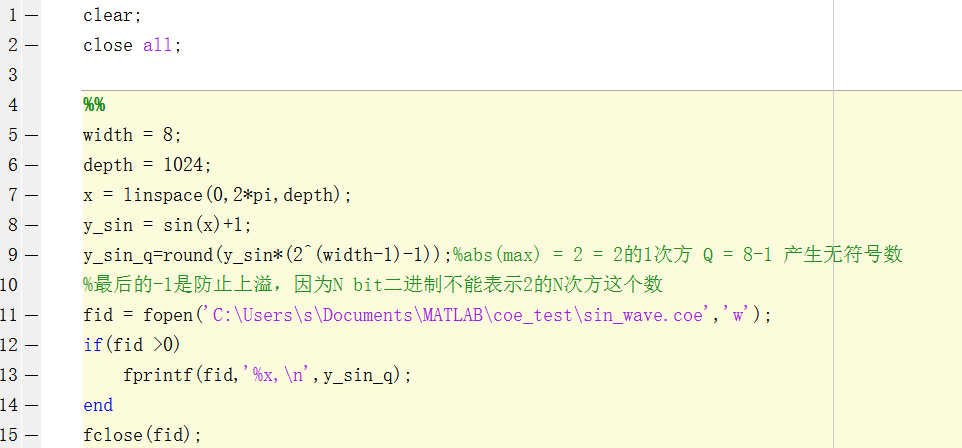

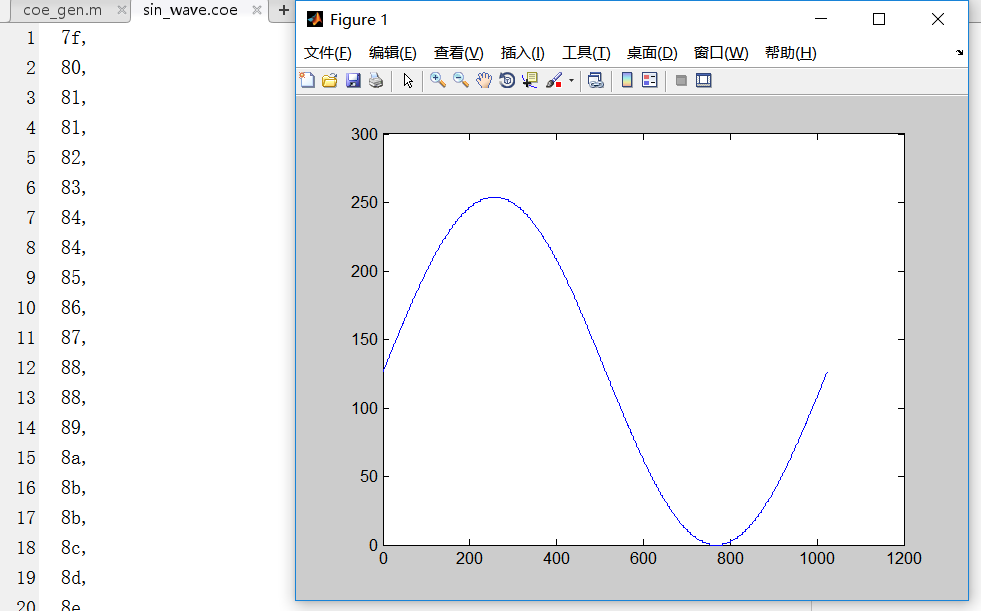

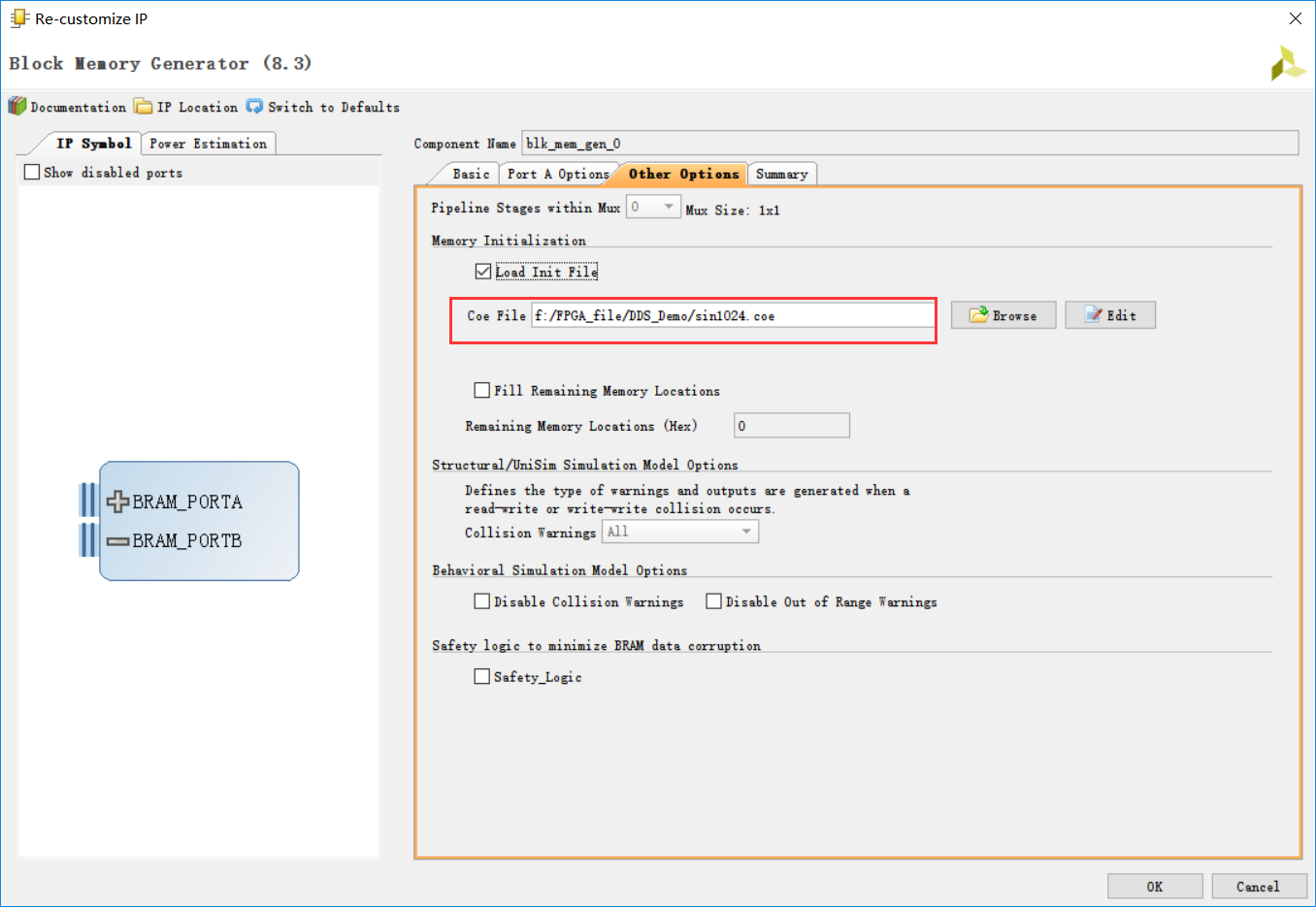

四、MATLAB产生正弦序列.coe文件及ROM初始化

MATLAB产生频率为1/2*pi标准正弦序列。验证无误后,在VIVADO中调用Block Memory Generator IP核,配置为单口ROM,使用刚才产生的系数文件初始化ROM地址数据。

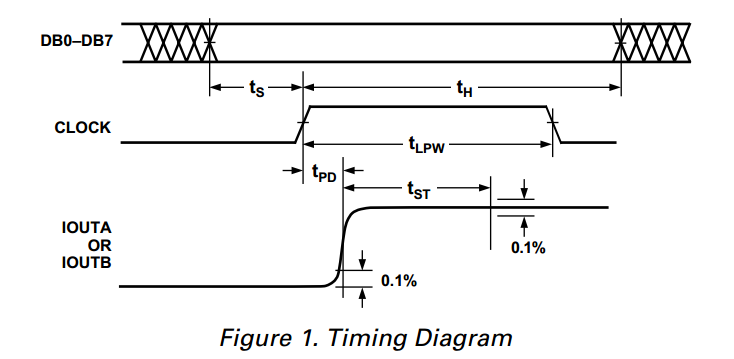

五、DAC ADC驱动

该设计使用的DAC ADC均为为低速并口转换芯片,无需配置,只要FPGA给出时钟信号,并输出/入并行数据即可。根据AD9708 datasheet时序图,其在时钟上升沿采样,故FPGA在输出时钟下降沿更新数据可满足建立与保持时间要求。ADC同样上升沿开始更新数据,接收端在时钟是上升沿采集数据,这样每一时钟周期可以采到上一拍送出的数据。

六、函数发生器及测试工程设计

`timescale 1ns / 1ps module sin_generator#(parameter FCW_W = ,

DAC_W = )

(

input clk,//DAC采样时钟 由PLL产生

input rst_n, input [FCW_W-:] fcw,

output [DAC_W-:] dac_data,

output dac_clk

); reg [ (FCW_W-):] sum ;

wire [:] addra;

//reg [9:0] addra;//地址测试信号

wire ena;

wire [:] douta; //相位累加器

//时钟下降沿产生数据 DAC上升沿采样

always @(negedge clk or negedge rst_n )begin

if(rst_n==) begin

sum <= () ;

end

else begin

sum <= (sum+fcw) ;

end

end assign addra = sum[FCW_W--:]; //rom地址测试

/*always @(posedge clk or negedge rst_n )begin

if(rst_n==0) begin

addra <= (0) ;

end

else begin

addra <= (addra+1) ;

end

end*/ blk_mem_gen_0 u_bram (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.addra(addra), // input wire [9 : 0] addra

.douta(douta) // output wire [7 : 0] douta

);

assign ena = 'b1;

//输出信号

assign dac_data = douta;

assign dac_clk = ~clk; endmodule

sin_generator

函数发生器模块由输入端口fcw数值确定频率控制字。测试工程顶层包括差分时钟转单端时钟原语,用于产生DAC ADC时钟的PLL 函数发生器模块,生成特定频率控制字的VIO IP核,还有接收端ADC数据采样逻辑以及ILA 调试IP核。

`timescale 1ns / 1ps module DDS_Demo_top

#(parameter AD_DA_W = )

(

input sys_clk_p,

input sys_clk_n,

input rst_n, output [AD_DA_W-:] DAC_data,

output DAC_clk, input [AD_DA_W-:] ADC_data,

output ADC_clk

); localparam FCW_W = ; wire sys_clk_ibufg;

wire clk_dac,clk_adc;

reg [ (AD_DA_W-):] data_ad ; wire [FCW_W- : ] probe_out0;

wire [AD_DA_W*-:] probe0; //ADC接口信号

//ADC在时钟上升沿后送出数据,FPGA下一个上升沿采样

assign ADC_clk = clk_adc; always @(posedge clk_adc or negedge rst_n )begin

if(rst_n==) begin

data_ad <= () ;

end

else begin

data_ad <= (ADC_data) ;

end

end /***************************************子模块例化***************************************/

IBUFGDS #

(

.DIFF_TERM ("FALSE"),

.IBUF_LOW_PWR ("FALSE")

)

u_ibufg_sys_clk

(

.I (sys_clk_p),

.IB (sys_clk_n),

.O (sys_clk_ibufg)

); clk_wiz_0 u_pll

(

// Clock out ports

.clk_out1(clk_dac), // output clk_out1

.clk_out2(clk_adc), // output clk_out2

// Status and control signals

.resetn(rst_n), // input resetn

.locked(), // output locked

// Clock in ports

.clk_in1(sys_clk_ibufg)); // input clk_in1 sin_generator#(.FCW_W(FCW_W),

.DAC_W(AD_DA_W))

u_sin_gen

(

.clk (clk_dac) ,//DAC采样时钟 由PLL产生

.rst_n (rst_n) ,

.fcw (probe_out0) ,

.dac_data (DAC_data) ,

.dac_clk (DAC_clk) //由clk_dac产生

); //debug cores

vio_0 u_vio (

.clk(clk_dac), // input wire clk

.probe_out0(probe_out0) // output wire [15 : 0] probe_out0

); ila_0 u_ila (

.clk(clk_adc), // input wire clk

.probe0(probe0) // input wire [15:0] probe0

); assign probe0[:] = DAC_data;

assign probe0[:] = ADC_data; endmodule

DDS_Demo

最后添加引脚约束文件:

#################################clock && reset###############################################

create_clock -period [get_ports sys_clk_p]

set_property PACKAGE_PIN R4 [get_ports {sys_clk_p}]

set_property IOSTANDARD DIFF_SSTL15 [get_ports {sys_clk_p}] set_property PACKAGE_PIN T6 [get_ports rst_n]

set_property IOSTANDARD LVCMOS15 [get_ports rst_n] #####################DAC PIN connect J4 expansion interface##########################

set_property PACKAGE_PIN H14 [get_ports {DAC_clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_clk}] set_property PACKAGE_PIN J14 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN H15 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN J15 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN G13 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN H13 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN J21 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN J20 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}]

set_property PACKAGE_PIN G16 [get_ports {DAC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DAC_data[]}] #####################ADC PIN connect J4 expansion interface########################## set_property PACKAGE_PIN D22 [get_ports {ADC_clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_clk}] set_property PACKAGE_PIN G21 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN G22 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN H20 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN G20 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN J22 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN H22 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN K21 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

set_property PACKAGE_PIN K22 [get_ports {ADC_data[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADC_data[]}]

clk_pin

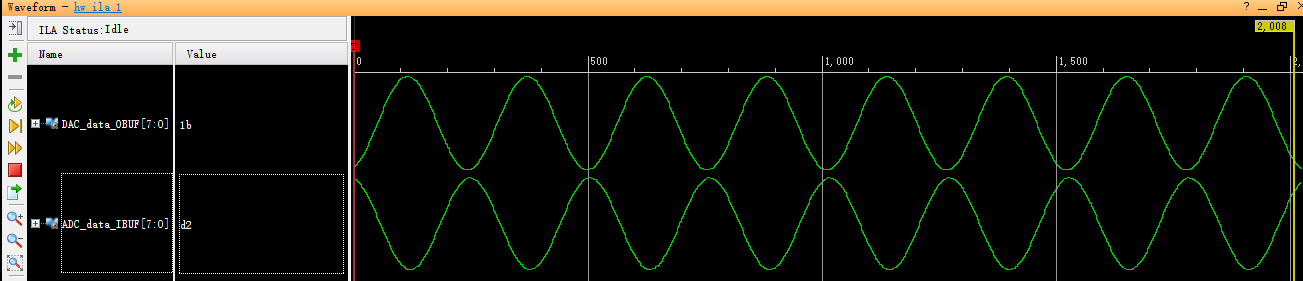

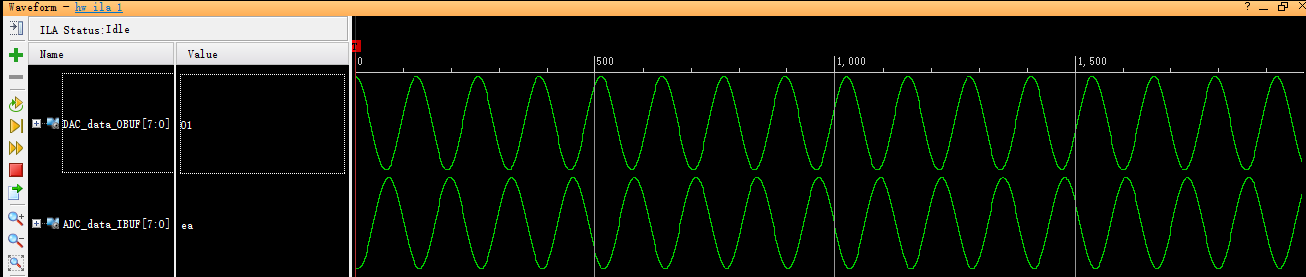

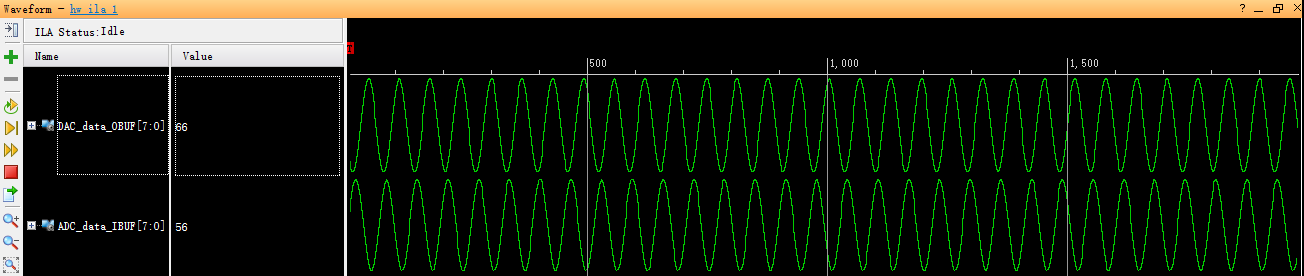

七、实验结果分析

依据之前的参数和DDS信号频率公式,所生成正弦函数频率最好在32/2^16~32/3MHZ之内,使用VIO改变频率控制字数值,观察ILA抓取的发送与接收数据模拟形式波形。任意给出三组频率范围内波形,频率依次由低到高。

总体来讲还是比较简单。搭建好DAC ADC环路,后面可以验证些滤波 同步算法,或者做些数字频率计、示波器之类的实用设计。

数字信号处理专题(1)——DDS函数发生器环路Demo的更多相关文章

- 数字信号处理专题(3)——FFT运算初探

一.前言 FFT运算是目前最常用的信号频谱分析算法.在本科学习数字信号处理这门课时一直在想:学这些东西有啥用?公式推来推去的,有实用价值么?到了研究生后期才知道,广义上的数字信号处理无处不在:手机等各 ...

- 数字信号处理专题(2)——利用FPGA进行基本运算及特殊函数定点运算

一.前言 FPGA以擅长高速并行数据处理而闻名,从有线/无线通信到图像处理中各种DSP算法,再到现今火爆的AI应用,都离不开卷积.滤波.变换等基本的数学运算.但由于FPGA的硬件结构和开发特性使得其对 ...

- FPGA与数字信号处理

过去十几年,通信与多媒体技术的快速发展极大地扩展了数字信号处理(DSP)的应用范围.眼下正在发生的是,以更高的速度和更低的成本实现越来越复杂的算法,这是针对高级信息服更高带宽以及增强的多媒体处理能力等 ...

- 数字信号处理--FFT与蝶形算法

在数字信号处理中常常需要用到离散傅立叶变换(DFT),以获取信号的频域特征.尽管传统的DFT算法能够获取信号频域特征,但是算法计算量大,耗时长,不利于计算机实时对信号进行处理.因此至DFT被发现以来, ...

- 数字信号处理与音频处理(使用Audition)

前一阵子由于考博学习须要,看了<数字信号处理>,之前一直不清除这门课的理论在哪里应用比較广泛. 这次正巧用Audition处理了一段音频,猛然发现<数字信号处理>这门课还是很实 ...

- 数字信号处理MATLAB简单序列

数字信号处理应用的几个基本序列: 1 单位样本序列 function mainImseq() clc clear disp('生成抽样序列'); y=imseq(,,); %调用样本函数,此时序列下标 ...

- 现代数字信号处理——AR模型

1. AR模型概念观 AR模型是一种线性预测,即已知N个数据,可由模型推出第N点前面或后面的数据(设推出P点),所以其本质类似于插值,其目的都是为了增加有效数据,只是AR模型是由N点递推, ...

- 如何使用Matlab做数字信号处理的仿真1

例如 第三版数字信号处理P51 -1.14习题时域离散信号的相关性研究x(n)=Asin(ωn)+u(n),其中ω=π/16,u(n)是白噪声,现要求 ⑴.产生均值为0,功率P=0.1的均匀分布白噪声 ...

- FS,FT,DFS,DTFT,DFT,FFT的联系和区别 数字信号处理

DCT变换的原理及算法 文库介绍 对于初学数字信号处理(DSP)的人来说,这几种变换是最为头疼的,它们是数字信号处理的理论基础,贯穿整个信号的处理. 学习过<高等数学>和<信号与系统 ...

随机推荐

- PyCharm2019 激活码

因公司的需求,需要做一个爬取最近上映的电影.列车号.航班号.机场.车站等信息,所以需要我做一个爬虫项目,当然java也可以做爬虫,但是还是没有python这样方便,所以也开始学习Python啦!!! ...

- android 缩放平移自定义View 显示图片

1.背景 现在app中,图片预览功能肯定是少不了的,用户基本已经形成条件反射,看到小图,点击看大图,看到大图两个手指开始进行放大,放大后,开始移动到指定部位~~~ 我相信看图的整个步骤,大家或者说用户 ...

- ES 04 - 安装Kibana插件(6.6.0版本)

目录 1 Kibana是什么 2 安装并启动Kibana 2.1 准备安装包 2.2 修改配置文件 2.3 启动Kibana并验证 2.4 关闭Kibana服务 3 Kibana功能测试 3.1 关于 ...

- 补习系列(4)-springboot 参数校验详解

目录 目标 一.PathVariable 校验 二.方法参数校验 三.表单对象校验 四.RequestBody 校验 五.自定义校验规则 六.异常拦截器 参考文档 目标 对于几种常见的入参方式,了解如 ...

- Supervisor 为服务创建守护进程

今天需要再服务上部署一个.net 方面的项目:当时开启服务的命令只能在前台执行:使用nohub CMD &等放在后台开启服务都会宕机:所以搜寻了Supervisor 这个解决办法,为服务创建守 ...

- GAN模型生成手写字

概述:在前期的文章中,我们用TensorFlow完成了对手写数字的识别,得到了94.09%的识别准确度,效果还算不错.在这篇文章中,笔者将带领大家用GAN模型,生成我们想要的手写数字. GAN简介 对 ...

- 如何使用在三星840 SSD硬件加密下使用Bitlocker

我的笔记本存放到比较重要的资料,需要加密,想到我的三星EVO 850 SSD支持三种加密模式,于是想使用全盘加密模式.但是找了半天没找到一点合适的中文资料,于是怒而翻译一下加密全盘加密的Bitlock ...

- 持续集成配置之Nuget

持续集成配置之Nuget Intro 本文是基于微软的 VSTS(Visual Studio Team Service) 做实现公众类库的自动打包及发布. 之前自己的项目有通过 Github 上的 T ...

- Python全栈开发之---assert断言

一.python assert的作用: 根据Python 官方文档解释(https://docs.python.org/3/reference/simple_stmts.html#assert), & ...

- Flask 系列之 优化项目结构

说明 操作系统:Windows 10 Python 版本:3.7x 虚拟环境管理器:virtualenv 代码编辑器:VS Code 实验目标 完善环境配置,添加 异常请求 处理 实现 400.404 ...