如何确定FPGA电路中DDR4的Speed bin 是否兼容?

原创 by DeeZeng

实际工作中,经常会碰到因为DDR3/4 或其他料件换料了,需要判断FPGA工程中IP设置需要重新改动,或是兼容直接换料就可行。

我个人倾向用 跑的速度的 speed bin 去设定,然后确认speed bin 是兼容的。

比如 DDR4 将换成2666 的chip, 但Arria 10 工程 只跑2133 或2400 的速度, 那我就按照2133 或 2400 的 speed bin 来设置。

但会需要确认 2133 、2400 speed bin 是被 2666 的chip 向下兼容的。

怎样查看Speed Bin 是否兼容呢?

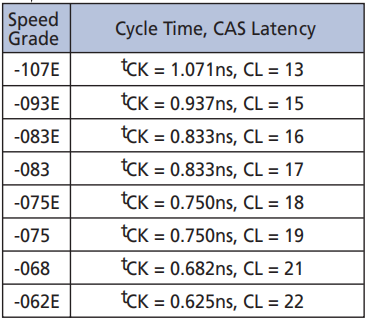

很简单, DDR4的datasheet中就有提,比如 Micron的这颗(随便找的一颗)

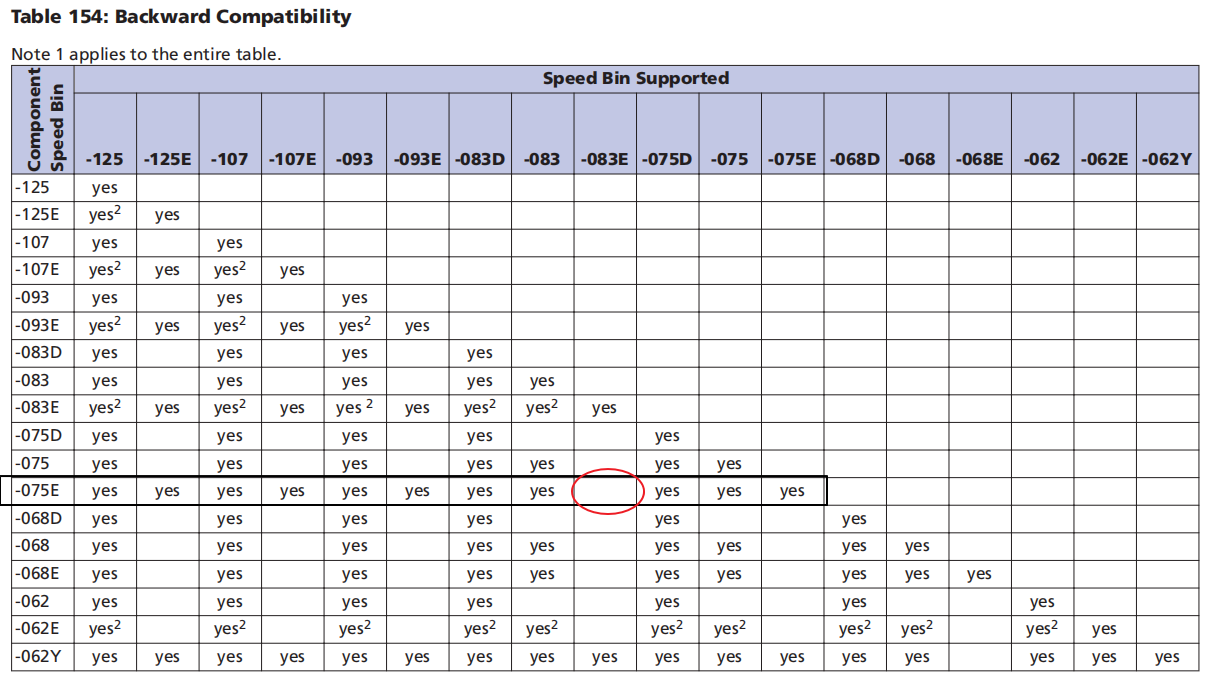

比如 我们选定 2666 的 component speed bin 是 075E。 那考虑兼容的时候 就会看到 不兼容 2400的 083E

这样设定IP的时候 我们就可以设定 2133 的093 或 093E speed bin 或 2400的 083 speed bin,而2400的083E speed bin 是不行的。

为什么会这样呢? 那有些参数是随 clock rate 变化的比如多少UI 是没影响。 但tRCD,tRP则是另外的情况,当然我们直接看兼容表就行了。

从兼容表也可以看出,并不是速度快就能直接替代速度慢的,有些参数还是不行的。 选替代料的时候需要注意一下。

是不是很简单,查看一下兼容表确认下就好!

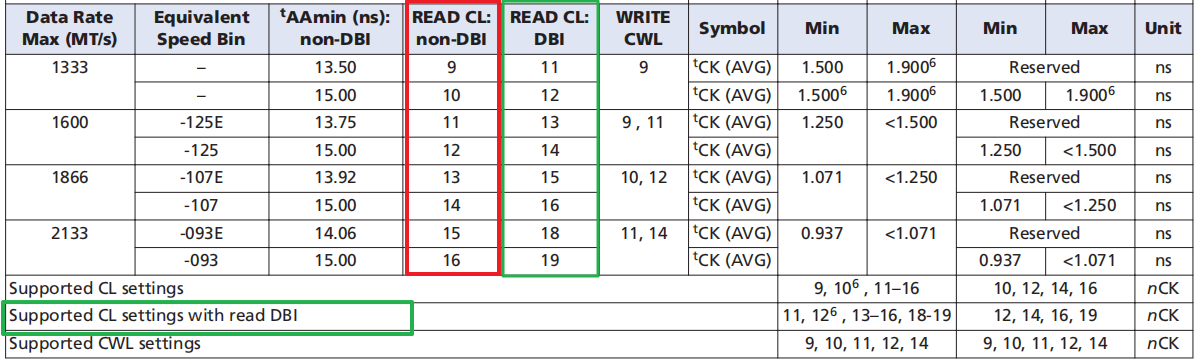

题外话:Data Bus Inversion(DBI) 这个功能可以在IP 中使能与否。

打开它可以让DQ IO 翻转更少,降低功耗。但它同时会增加latency(毕竟要多出一些判断来确定DQ 如何翻转)

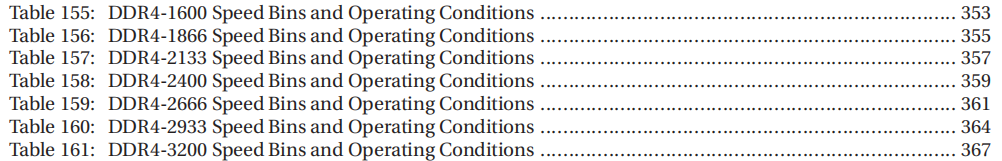

可以在 Speed Bin 中看到:

所以打开DBI 与否 对 CL 的设定是有影响的。

如何确定FPGA电路中DDR4的Speed bin 是否兼容?的更多相关文章

- 影响FPGA设计中时钟因素的探讨。。。转

http://www.fpga.com.cn/advance/skill/speed.htm http://www.fpga.com.cn/advance/skill/design_skill3.ht ...

- FPGA设计中的异步复位、同步释放思想

1.一个简单的异步复位例子: module test( input clk, input rst_n, input data_in, output reg out ); always@(posedge ...

- [专业名词·硬件] 1、等效串联电阻ESR概述及稳压电路中带有一定量ESR电容的好处

一.等效串联电阻ESR概述 ESR是Equivalent Series Resistance的缩写,即“等效串联电阻”.理想的电容自身不会有任何能量损失,但实际上,因为制造电容的材料有电阻,电 ...

- FPGA系统中DRAM,SRAM,SDRAM,FLASH 区别(转)

原文:http://hi.baidu.com/abners/item/a9042ef35d3f005bc8f337f5 一般来说这几种存储器是一个nios系统都具有的,sram的好处是接口简单,速度快 ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- FPGA计算中定标与位扩展的实现

我不知道名字取对没有,在FPGA计算中有时往往需要在不溢出的情况下将数扩大,从而获得更好的计算精度. 比如.在一个8位宽的系统中,将x=0000_0010,算术左移m=5位之后得到xt=0100_00 ...

- 学习FPGA过程中的理论知识

学习FPGA,先要有数电知识,最好有点C语言,,学好硬件描述语言,verilog或者vhdl.在有这些基础上,做一些小的模块不断积累.这里不再赘述. 下面介绍一下关于FPGA学习过程中的一些理论知识. ...

- 硬件电路中VCC,VDD,VEE,VSS有什么区别

电路中GND和GROUND.VCC,VDD,VEE,VSS有什么区别 一.解释 DCpower一般是指带实际电压的源,其他的都是标号(在有些仿真软件中默认的把标号和源相连的)VDD:电源电压(单极器件 ...

- 电路中IC器件电压符号的解释

在电子芯片.运算处理器等集成电路行业中,存在多种电压.常用的的有:VDDQ->The supply voltage to output buffers of a memory chip 存储芯片 ...

随机推荐

- C# RESTful API 访问辅助类

REST 全称是 Representational State Transfer,有人说它是一种风格,并非一种标准,个人觉得挺有道理.它本身并没有创造新的技术.组件与服务,更像是告诉大家如何更好地使用 ...

- 微服务网关 Spring Cloud Gateway

1. 为什么是Spring Cloud Gateway 一句话,Spring Cloud已经放弃Netflix Zuul了.现在Spring Cloud中引用的还是Zuul 1.x版本,而这个版本是 ...

- cat more less 命令混用

在Linux系统中有三种命令可以用来查阅全部的文件,分别是cat.more和less命令.它们查阅文件的使用方法也比较简单都是 命令 文件名 ,但是三者又有着区别. 1.cat命令可以一次显示整个文件 ...

- R语言实战(第2版)PDF完整版带书签目录

<R语言实战2>PDF+源代码 下载:https://pan.baidu.com/s/1gP_16Xq9eVmLJ1yOsWD9FA 提取码:l8dx 分享更多python数据分析相关电子 ...

- C# 6 新语法

1. using 声明的静态用法 2. 表达式体方法 3. 表达式体属性 4. 自动实现的属性初始化器 5. 只读的自动属性 6. nameof 运算符 7. 空值传播运算符 8. 字符串插值 9. ...

- 灵雀云CTO陈恺应邀出席国泰君安信息产业投资峰会,探讨全球科技产业新格局

2019年7月9-10日,国泰君安信息产业投资峰会在上海陆家嘴举办.作为国内容器PaaS领域的龙头公司,灵雀云受邀出席本次大会,在“数字化转型从云做起”的论坛中,CTO陈恺发表了<云原生助力企业 ...

- 自定义HashSet判重标准

HashSet在执行add时会首先根据目标类的hashcode判断是否有与其hashcode相同的对象,若有则使用equals该对象判断是否与其相同. HashSet保证了元素的唯一性, 我们可以通过 ...

- junit中test用法

Test注解 有两个值, expected, timeout expect后面接异常类, timtout后面接时间, 符合则为ture 如 @Test (expected = NullPointExc ...

- spring系列(一):超级经典入门

一 spring是什么 Spring是一个开源框架,它由RodJohnson创建.它是为了解决企业应用开发的复杂性而创建的.Spring使用基本的JavaBean来完成以前只可能由EJB完成的事情. ...

- Android Native 内存泄漏系统化解决方案

导读:C++内存泄漏问题的分析.定位一直是Android平台上困扰开发人员的难题.因为地图渲染.导航等核心功能对性能要求很高,高德地图APP中存在大量的C++代码.解决这个问题对于产品质量尤为重要和关 ...