【转】I2C总线相关知识

1. I2C access

1.1. I2C introduction

I2C(Inter-Integrated Circuit)总线是由NXP恩智浦半导体公司在80年代开发的两线式串行总线,用来进行主控器与被控器的通信。I2C总线具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点,是微电子通信控制领域广泛采用的一种总线标准。

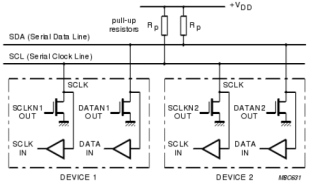

I2C总线由两根信号线构成,一根是串行数据线SDA,一根是串行时钟线SCL,这两根信号线都是双向的,SDA的传输与SCL同步。Figure 1中,连接到总线的器件为漏极开路输出结构,各器件之间执行线与的功能。当总线空闲时,SDA和SCL必须接上拉电阻至高电平来省电。串行的8 位双向数据传输位速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。

I2C总线上可同时挂接多个器件,器件之间靠不同的编址来进行区分,每个连接到总线上的期间都可以通过唯一的地址与主机进行通信。由于I2C是双向传输的总线,每个器件都可能成为主机(发送器)或者从机(接收器),时钟信号SCL由主机产生。

Figure 1 开漏输出

RLXXXA支持一组I2C接口,I2C 工作在master mode情况下可完成上电后EEPROM auto-download动作。而I2C工作在Slave mode时支持external CPU通过I2C access internal Switch core register.

Figure 2 RLXXXA的I2C总线

如果external cpu访问I2C,同时internal 8051通过I2C access eeprom,此时内部会错开,前者优先做动作。

1.2. I2C Transferring Data

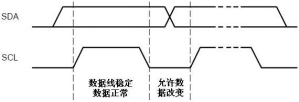

数据的有效性:SDA 线上的数据必须在时钟的高电平周期保持稳定。只有在SCL 线的时钟信号为低电平时,才允许数据线的电平改变状态。(起始时和结束时例外)

Figure 3 I2C位传输数据有效性

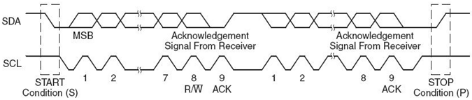

起始条件(S):SCL 线是高电平时,SDA 线从高电平向低电平切换,之后被认为处于忙的状态;

结束条件(P):SCL 线是高电平时,SDA 线由低电平向高电平切换,之后被认为返回空闲状态。若不产生结束信号而产生重复起始条件(Sr),则总线会一直处于忙的状态,此时的起始条件与重复起始条件在功能上是一样的。

Figure 4 起始条件和结束条件

应答信号(ACK):I2C总线上的所有数据都是以8位字节传送的,发送器每发送一个字节,就在时钟脉冲9期间释放数据线(拉高SDA),由接收器反馈一个应答信号,表示接收器已经成功地接收了该字节。应答位的时钟脉冲仍由主机产生,而应答位的数据状态则遵循“谁接受谁产生”的原则,即总是由接收器产生应答位。主机向从机发送数据时,应答位由从机产生;主机从从机接受数据时,应答位由主机产生。I2C总线标准规定:应答位为0表示接收器应答(ACK),为1表示非应答(NACK)。对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。

Figure 5 I2C总线的响应

1.3. I2C Slave for External CPU Access

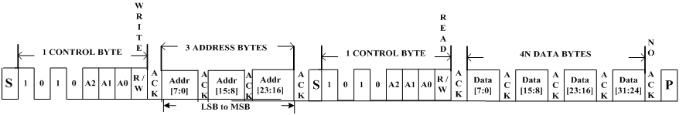

工作在slave mode情况下,I2C支持一次Read/Write与sequential Read/Write一笔4N Byte data的方式,由control byte(1) + address bytes(3) + data bytes(4N, N: integer, N≠0)组合而成。

主机发送一个起始条件后开始帧的发送,发送到SDA 线上的每个字节必须为8 位,每次传输可以发送的字节数量不受限制。每成功发送1Byte字节数据都会产生一个ACK信号。首先传输的是数据的最高位(MSB),如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟线SCL保持低电平,迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL后数据传输继续。

I2C总线上传输帧的首字节control byte主要用来寻址以及决定数据传输方向。其中高4位是device type identifier,用来标识器件类型,固定为1010(一般为EEPROM)。接下来的三位A2、A1、A0为器件的片选地址Device address,因为EEPROM与I2C会共享SCK/SDA的接口, 所以两者必须用Device address来分出外部的I2C Master所要access的是EEPROM还是RLxxx。一般来说, EEPROM会排在Device address 0-3的位置, 而Device会从4开始排. 目前规划RL6xxxA support最多4个Device address给EEPROM使用,default值为000,为避免在进行auto-download动作时与其它device的address发生冲突,可以通过烧写EFUSE来修改。RLxxx Device address default订在4的地方, 但可以通过I2C_Device_Addr[2:0]来修改其device address,也可以通过烧写EFUSE来修改。control byte的LSB为数据传输方向位,write时写0,read时写1.

Figure 6 External CPU Access control byte Sequence

External CPU通过I2C方式access内部register时,在Control Byte部分设置对应的RL6xxxA Devices address和R/W command,在3byte address部分设置要访问的register address。

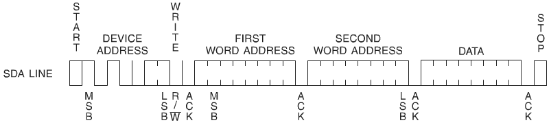

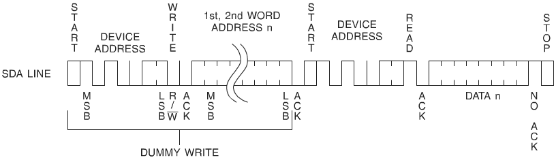

A. 如果是read命令,在standard模式下,format改为进行两次start,第一次表示下register地址,第二次为read data。Standard mode也就是首先执行一个伪写操作(R/W位置写0),ASIC在读到3byte地址后,重新发送起始信号和ASIC地址,此时R/W位置写1,然后会送出对应地址的4byte register值,如图6所示。如果master在得到4byte register 值后,不产生应答信号同时送出stop,就表示完成一次read操作;如果master继续输出SCL,而不输出stop,ASIC在内部自动进行地址的increment(每次+4),输出该register的值,完成sequential read操作,master需要保证SCL以4byte的整数倍输出。

Standard mode

Figure 7 External CPU Access Data Sequence (read)

B. 如果是write命令,ASIC在得到3byte地址后,会读取后面连续的4byte data并将其写到对应的register,如图7所示。Master可以支持single write和sequential write,在single write时,只对一个register进行write操作后,输出stop;在burst write操作时,可以连续写入4N整数倍的data到register,中间不产生停止信号,ASIC内部自动进行地址的increment操作。

Figure 8 External CPU Access Data Sequence (write)

当需要对同一个table的连续entry进行read/write操作的时候,为了提高table access的速度,结合I2C的burst访问,在table access的INDIRECT_CONTROL_FOR_CPU中增加bit Table_Burst(0b0: standard burst way 0b1: special burst way for sequential table access),用来选择burst方式。

I2C提供burst方式2:初始操作和burst方式1一致,read操作时,先control-addr-control-4N bytes data,之后addr+4,继续read/write后续的data. 两种方式的区别就在于前者只能对一条entry的连续对写,而后者可以对连续entry进行读写操作。当需要进行Sequential读取table entry时,将该bit置1,I2C就会切换成burst2的sequence方式。

Standard burst way: control byte +3 address bytes +某一条entry的4N data bytes;

Special burst way: control byte +3 address bytes +第一条entry的TableDataNum个data bytes +第二条entry的TableDataNum个data bytes +……+第EntryNum条entry的TableDataNum个data bytes.

此时可通过table access BURST_OPERATION中bit[4:0] TableDataNum来设置burst连续操作的data register数目,bit[14:5] EntryNum用来设置连续访问的entry的数目。完成TableDataNum个data的read/write操作后,I2C会返回到初始addr处,重新从写入的addr处read/write, 操作下面连续TableDataNum个data. 每次操作完成一条entry的read/write. 每次读出一条entry存在该组indirect data register中, read后自动填入下条entry. Write时会自动填入下条entry需要写的值,entry数目自动加1,自动写入下条entry. eg:需要访问L2 table, 只想获得entry中前2个data register中的参数,那就可以设置TableDataNum=2,那burst操作中返回的就是所有访问的entry中前2个data register中的值。

若I2C处所写的entry数小于EntryNum时,待I2C写完相应的entry后,software将execute写为0.

Table 1 I2C External Access Status Register

|

Reg.bit |

Name |

Mode |

Description |

Default |

|

n.31-n.22 |

Reserved |

RO |

Reserved |

0x0 |

|

n.21-n.0 |

I2C_dataLen |

RO |

Record the data length When read this field ,return the last time burst operation length |

0x0 |

dataLen记录上次read/Write的burst length,如果是single read/write,会返回1,如果是burst操作,返回burst操作的length.

Table 2 I2C External Access Address Register

|

Reg.bit |

Name |

Mode |

Description |

Default |

|

n.31-n.24 |

Reserved |

RO |

Reserved |

0x0 |

|

n.23-n.0 |

I2C_EAAR |

RO |

Latch I2C external access address |

0x0 |

I2C_EAAR栏位记录上次I2C操作时address栏位里面提供的address。

1.4. I2C Master for EEPROM Auto-Download

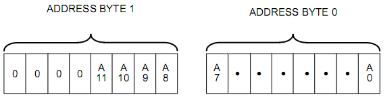

工作在master mode情况下,Device address A2、A1、A0 default值为000,RLxxx只支持大size的EEPROM: 32~128Kb/256 Kb /512Kb. 大size的有分Word-high address and Word-low address共16 bit,如Figure 9所示(address byte 1所占用的bit由EEPROM的size决定)。EEPROM size则会定义在SEL_EEPROM_RANGE[2:0]中,由EEPROM 将信息传递给switch. I2C进行EEPROM auto-download的速率定义在EEPROM_AUTO_DOWNLOAD_CONTROL中的SEL_SCK_FREQ.

Figure 9 Large Size (32Kb) EEPROM address byte

Figure 10 EEPROM Write Timing

Figure 11 EEPROM Read Timing

NOTE:

1. EEPROM第一次download过程中被打断(pin reset拉低或者power off), 为了保证EEPROM在我们做auto load时已经reset ok,再次load时需要以下步骤:

Step 1. SCL输出9 clock,同时SDA保持为high

Step 2. 输出start condition

Step 3. 再重新输出一个start condition开始download过程

前两个步骤是为了EEPROM reset,这样start就一定能正确认到,后续download过程也能正常进行。若不按照该步骤做,会导致第二次downloadfail:因为第二次download在2s左右时间内开始进行,此时ASIC开始吐clock,但eeprom会按照上次被打断的地方开始向外drive data,导致第二次download的start信号被drive坏,不能正常开始第二次download.

2. 为了保证I2C的访问速度,在slave时,如果输出高电平,应该输出高电平,如果输出低电平的时候应该输出低电平;Master时由于速度不高,不存在上诉问题的考虑,但也希望能做到一致。这样做并不符合standard的做法(如果输出高电平,应该推高阻),原因是:第一,推高阻影响速度,无法达到要求的10MHz的速度;第二,即使做了推高阻,但是没有做arbitration其实也不符合standard。考虑到本Project的应用场合不会有两个master,所以不符合standard不会有问题。

【转】I2C总线相关知识的更多相关文章

- Linux设备驱动模型之I2C总线

一.I2C子系统总体架构 1.三大组成部分 (1)I2C核心(i2c-core):I2C核心提供了I2C总线驱动(适配器)和设备驱动的注册.注销方法,提供了与具体硬件无关的I2C读写函数. (2)I2 ...

- Linux+I2C总线分析(主要是probe的方式)

Linux I2C 总线浅析 ㈠ Overview Linux的I2C体系结构分为3个组成部分: ·I2C核心: I2C核心提供了I2C总线驱动和设备驱动的注册.注销方法,I2C通信方法(即“algo ...

- I2C总线协议的总结介绍

在看天翔哥的视频之后,他强调要把I2C协议好好研究一下,那么就对一些基本的通信手段是十分有帮助的..那么就来了解一下I2C总线协议的一些知识吧. I2C(Inter-Integrated Circui ...

- i2c总线驱动,总线设备(适配器),从设备,从设备驱动的注册以及匹配

常用链接 我的随笔 我的评论 我的参与 最新评论 我的标签 随笔分类 ARM裸机(13) C(8) C++(8) GNU-ARM汇编 Linux驱动(24) Linux应用编程(5) Makefile ...

- I2C总线驱动框架详解

一.I2C子系统总体架构 1.三大组成部分 (1)I2C核心(i2c-core):I2C核心提供了I2C总线驱动(适配器)和设备驱动的注册.注销方法,I2C通信方法(”algorithm”)上层的,与 ...

- Linux I2C总线控制器驱动(S3C2440)

s3c2440的i2c控制器驱动(精简DIY),直接上代码,注释很详细: #include <linux/kernel.h> #include <linux/module.h> ...

- Linux I2C总线设备驱动模型分析(ov7740)

1. 框架1.1 硬件协议简介1.2 驱动框架1.3 bus-drv-dev模型及写程序a. 设备的4种构建方法a.1 定义一个i2c_board_info, 里面有:名字, 设备地址 然后i2c_r ...

- 【单片机通信协议】CAN总线基础知识

CAN总线基础知识(一) 1.1 CAN总线是什么? CAN(Controller Area Network)是ISO国际标准化的串行通信协议.广泛应用于汽车.船舶等.具有已经被大家认可的高性能和可靠 ...

- (5)I2C总线的10bit地址以及通用广播地址

其实,10bit地址我没用过,通用广播地址更没用过.通用广播地址应该是在多个mcu之间用i2c进行通信时使用的.虽说没用到,但还是做了翻译,说不定以后有机会用到: 10bit地址 10bit的寻址扩展 ...

随机推荐

- Jsp Cookie的创建与读取 标签: cookiejsp 2016-11-17 15:14 61人阅读 评论(0)

Cookie.jsp <%@ page language="Java" import="java.util.*" pageEncoding="u ...

- css3 box-shadow属性 鼠标移动添加阴影效果

text-shadow是给文本添加阴影效果,box-shadow是给元素块添加周边阴影效果. 基本语法:{box-shadow:[inset] x-offset y-offset blur-rad ...

- 一些SAP Partners能够通过二次开发实现打通C/4HANA和S/4HANA的方法介绍

有好几位朋友在公众号后台给我留言询问SAP C/4HANA和S/4HANA集成的方案. 尽管我给这些朋友推送了一个方案:打通C/4HANA和S/4HANA的一个原型开发:智能服务创新案例,然而我得到的 ...

- System IPC 与Posix IPC(msg消息对列)

系统消息队列: 一.消息队列基本概念 系统V消息队列是随内核持续的,只有在内核重起或者显示删除一个消息队列时,该消息队列才会真正被删除.因此系统中记录消息队列的数据结构(struct ipc_ids ...

- 你真的了解现在的PHP吗?

前段时间,公司的项目从PHP5.3升级到PHP7,现在项目里开始使用PHP7的一些新语法和特性.反观PHP的5.4.5.5.5.6版本,有点认知缺失的感觉.所以,决定看<Modern PHP&g ...

- 2019.1.2 Spring管理事务的方式

Spring管理事务的方式 1.编码式 1.将核心事务管理器配置到Spring容器 2.配置TransactionTemplate模版 3.将事务模版注入service 4.在Service中调用模版 ...

- javascript中的回调函数(callback) (转载)

代码如下: app.use(function(req, res, next) { var err = new Error('Not Found'); err.status = 404; next(er ...

- subline关联linux系统

一. 插件安装用Package Control安装插件按下Ctrl+Shift+P调出命令面板输入install 调出 Install Package 选项并回车,然后输入sftp,下拉列表中会出现一 ...

- iview中position: 'fixed'最顶层z-index

使用iview时候使用<Header :style="{position: 'fixed', width: '100%'}">不是最顶层解决方案 根据样式进行解决在ap ...

- [SharePoint]如何去掉欢迎导航的信息?

在我们实际的开发过程中,经常会把SharePoint中的一些已有的feature去掉,如欢迎信息下面的“我的设置”,“对本页面进行个性化设置”.详细见下图: Figure 1 常见的欢迎信息的界面 ...