Verilog学习笔记简单功能实现(一)...............D触发器

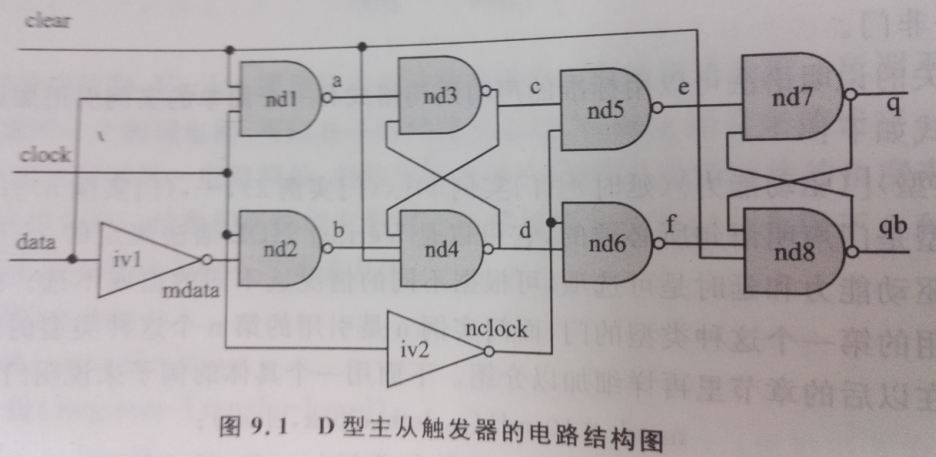

module D_flop(data,clk,clr,q,qb);

input data,clk,clr;

output q,qb;

wire a,b,c,d,e,f,ndata,nclk;

nand nand1(a,clr,data,clk),

nand2(b,ndata,clk),

nand4(d,c,b,clr),

nand5(e,c,nclk),

nand6(f,d,nclk),

nand8(qb,f,clr,q);

nand nand3(c,a,d),

nand7(q,e,qb);

not not1(ndata,data),

not2(nclk,clk);

endmodule

门级电路

上图就是门级Verilog语言描述的对应的网表,由图可以看出这是一个带异步置零的D触发器。

同样我们也可以采用行为描述来定义D触发器。

普通D触发器:

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always语句中被赋值的信号要声明为reg类型寄存器定义

always @ (posedge CLK)

begin Q <= D; end

endmodule

异步D触发器:

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn; //寄存器定义

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q<=;qn<=;end//异步清0,低有效

else if(!set) begin q<=;qn<=;end //异步置1,低有效

else begin q<=~d;qn<=~d;end

end

endmodule

同步触发器:

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(!reset) begin q<=;qn<=;end//同步清0,低有效

else if(!set) begin q<=;qn<=;end //同步置1,低有效

else begin q<=~d;qn<=~d;end

end

endmodule

注意,异步和同步触发器中else begin q<=~d;qn<=~d;end 更正为else begin q<=d;qn<=~d;end

Verilog学习笔记简单功能实现(一)...............D触发器的更多相关文章

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试

IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试 目的不是为了编写TSC2007驱动,是为了学习IIC驱动的编写,读一下TSC2007的ADC数据进行练习,, Linux主机驱动和外设驱 ...

随机推荐

- Android中GridView使用总结

1.http://blog.csdn.net/hellogv/article/details/4567095 基础篇,GridView最基本的用法 2.http://my.eoe.cn/cainia ...

- DB2解除锁表

背景 生产环境中,我几乎没有遇到过锁表.多是在开发过程中遇到的,比如团队开发中经常会遇到多个功能访问同一张表的情况.如果有开发人员在这张表加了排它锁,然后又忘记提交事务,那么其他开发人员就要一直等待了 ...

- MTNET 自用ios网络库开源

短短两天就在https://git.oschina.net/gangwang/MTNET这里收获15个星 github 5星, 值得收藏! MTNET 自用ios网络库开源, 自用很久了,在数歀上架的 ...

- WPF中如何用代码触发按钮Click处理

btnOk.RaiseEvent(new RoutedEventArgs(Button.ClickEvent));

- eclipse 编译出错(java.io.ObjectInputStream)的解决办法

Multiple markers at this line - The type java.io.ObjectInputStream cannot be resolved. It is indirec ...

- tengine-2.1.0 + lua + base64

参考:http://my.oschina.net/eduosi/blog/169606 安装 readline,lua 编译需要用到这个,centos 可以通过 yum 直接安装,如果不需要系统的,可 ...

- linux samba 服务配置及日志管理

2012-01-16 安装samba共需3个rpm包 samba-common-3.0.23c-2.i386.rpm samba-3.0.23c-2.i386.rpm samba-cli ...

- C++ string 用法详解

/////////////////////////////////////////////////////////////////////////////////// 任何人对本文进行引用都要标明作者 ...

- lucene.net的一个动态更新类

工作的需要,需要对于lucene.net索引即时的更新,毕竟lucene.net的索引重建的话比较慢,数据量大的时候建下要几天,所以就写个了缓冲类来解决即时的更新的问题,其实还是比较简单的. 大体上的 ...

- Android studio动态调试smali

前面介绍了使用IDA动态调试smali,这种方法设置简单,不用重打包,用起来方便,但是如果变量类型设置错误则会马上退出调试,这是让人不爽的地方,而使用Android studio则不会. 0x01 ...