基于EPCLYPSE的DDS控制器(一)

软硬件平台

操作系统:windows11

软件平台:vivado2021.1 开发套件

硬件平台:Digilent Eclypse-Z7 Zmod开发套件

vivado 工程搭建

①直接拉取笔者的三个ip

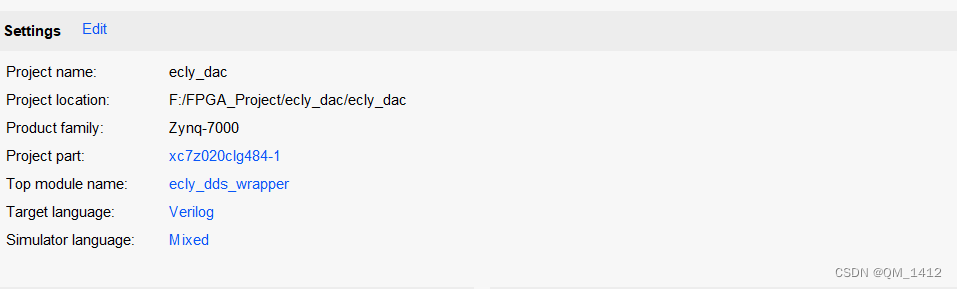

②新建工程

唯一注意的就是板子芯片不要选错就好了

③工程构建

主语路径不能有中文,这三个ip就是笔者链接的ip

在设置中导入三个下载好的ip,然后点击“block design”

然后就得到了以上这个界面

最后根据上面的示意图添加对应的ip,得到工程图

然后生成顶层文件,在做这一步之前先看一下注意事项 如果内部修改了,得重新生成顶层文件

②注意事项

③分配好管脚

若使用官方的板子,则用笔者的xdc文件就可以直接使用,否则需要对应自己板卡做对应引脚的修改,以下是笔者的管脚约束

## 125MHz Clock

set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { sys_clk }]; #IO_L12P_T1_MRCC Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { sys_clk }];

## Buttons_rst

set_property -dict { PACKAGE_PIN C17 IOSTANDARD LVCMOS33 } [get_ports { resetn}];

## USART

set_property -dict {PACKAGE_PIN H17 IOSTANDARD LVCMOS33} [get_ports uart_rxd]

set_property -dict {PACKAGE_PIN H18 IOSTANDARD LVCMOS33} [get_ports uart_txd]

## DAC

set_property -dict {PACKAGE_PIN W16 IOSTANDARD LVCMOS18} [get_ports ZmodDAC_ClkIn_0]

set_property -dict {PACKAGE_PIN W17 IOSTANDARD LVCMOS18} [get_ports ZmodDAC_ClkIO_0]

## DAC SPI

set_property -dict {PACKAGE_PIN Y14 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SDIO_0]

set_property DRIVE 4 [get_ports sZmodDAC_SDIO_0]

set_property -dict {PACKAGE_PIN AA14 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_CS_0]

set_property DRIVE 4 [get_ports sZmodDAC_CS_0]

set_property -dict {PACKAGE_PIN AA13 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SCLK_0]

set_property DRIVE 4 [get_ports sZmodDAC_SCLK_0]

set_property -dict {PACKAGE_PIN W15 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SetFS1_0]

set_property -dict {PACKAGE_PIN Y15 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SetFS2_0]

set_property -dict {PACKAGE_PIN Y13 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_Reset_0]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_EnOut_0]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[13]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[12]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[11]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[10]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[9]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[8]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[0]}]

set_property PACKAGE_PIN V13 [get_ports {dZmodDAC_Data_0[13]}]

set_property PACKAGE_PIN W13 [get_ports {dZmodDAC_Data_0[12]}]

set_property PACKAGE_PIN AB14 [get_ports {dZmodDAC_Data_0[11]}]

set_property PACKAGE_PIN AB15 [get_ports {dZmodDAC_Data_0[10]}]

set_property PACKAGE_PIN V14 [get_ports {dZmodDAC_Data_0[9]}]

set_property PACKAGE_PIN V15 [get_ports {dZmodDAC_Data_0[8]}]

set_property PACKAGE_PIN Y20 [get_ports {dZmodDAC_Data_0[7]}]

set_property PACKAGE_PIN Y21 [get_ports {dZmodDAC_Data_0[6]}]

set_property PACKAGE_PIN AA19 [get_ports {dZmodDAC_Data_0[5]}]

set_property PACKAGE_PIN AA18 [get_ports {dZmodDAC_Data_0[4]}]

set_property PACKAGE_PIN AB20 [get_ports {dZmodDAC_Data_0[3]}]

set_property PACKAGE_PIN AB22 [get_ports {dZmodDAC_Data_0[2]}]

set_property PACKAGE_PIN Y18 [get_ports {dZmodDAC_Data_0[1]}]

set_property PACKAGE_PIN Y19 [get_ports {dZmodDAC_Data_0[0]}]

④综合上板

在上板综合之前,一定要注意,这个板子的内部reset引脚是一直拉低的,若设计的复位低电平复位的,那么直接接入就会一直拉低,导致整个板子不工作,所以得取反

然后就可以愉快的生成比特流文件了

⑤实物接线

⑥测试输出

上位机软件

这个app控制器,需要matlab2021A的runningtime 所以可以自行下载一个,然后安装这个软件,也可以用matlab打开笔者的工程文件,也是一样的,看哪个方便即可

工程下载

笔者把三个ip丢在这里哩,要的可以去参考一下,️没错就是我

基于EPCLYPSE的DDS控制器(一)的更多相关文章

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 基于Controller接口的控制器及简单应用

DispatcherServlet在Spring当中充当一个前端控制器的角色,它的核心功能是分发请求.请求会被分发给对应处理的Java类,Spring MVC中称为Handle.在Spring 2.5 ...

- 基于FPGA的DDS设计(二)

在DDS设计中,如果相位累加器每个时钟周期累加1,就会输出频率为195.313KHz的波形.如果每个时钟周期累加2,就会输出频率为2*195.313KHz的波形·······,如果每两个时钟周期累加1 ...

- 基于FPGA的DDS任意波形发生器设计

一.简介 DDS技术最初是作为频率合成技术提出的,由于其易于控制,相位连续,输出频率稳定度高,分辨率高, 频率转换速度快等优点,现在被广泛应用于任意波形发生器(AWG).基于DDS技术的任 ...

- 基于FPGA(DDS)的正弦波发生器

记录背景:昨晚快下班时,与同事rk聊起怎么用FPGA实现正弦波的输出.我第一反应是利用高频的PWM波去滤波,但感觉这样的波形精度肯定很差:后来想起之前由看过怎么用FPGA产生正弦波的技术,但怎么都想不 ...

- Android 基于蓝牙的方向控制器

最近开发了一个蓝牙控制器App,用手机远程控制小球的运动. 包含了一些基础知识:多线程使用,页面UI数据更新,按钮事件,选择项功能,蓝牙功能(蓝牙打开,蓝牙搜索,蓝牙连接,蓝牙命令发送,蓝牙命令接收) ...

- 基于S5PC100的FIMC控制器解析

作者:邹南,华清远见嵌入式学院讲师. http://www.cnblogs.com/gooogleman/archive/2012/07/26/2610449.html CAMERA SENSOR O ...

- 基于异步的MVC webAPI控制器

MVC – Task-based Asynchronous Pattern (TAP) – Async Controller and SessionLess Controller Leave a re ...

- 国产CPLD(AGM1280)试用记录——做个SPI接口的任意波形DDS [原创www.cnblogs.com/helesheng]

我之前用过的CPLD有Altera公司的MAX和MAX-II系列,主要有两个优点:1.程序存储在片上Flash,上电即行,保密性高.2.CPLD器件规模小,成本和功耗低,时序不收敛情况也不容易出现.缺 ...

- 在MVC控制器里面使用dynamic和ExpandoObject,实现数据转义的输出

在很多时候,我们在数据库里面定义表字段和实际在页面中展示的内容,往往是不太匹配的,页面数据可能是多个表数据的综合体,因此除了我们在表设计的时候考虑周到外,还需要考虑数据展现的处理.如果是常规的处理,那 ...

随机推荐

- C++ Qt开发:QProcess进程管理模块

Qt 是一个跨平台C++图形界面开发库,利用Qt可以快速开发跨平台窗体应用程序,在Qt中我们可以通过拖拽的方式将不同组件放到指定的位置,实现图形化开发极大的方便了开发效率,本章将重点介绍如何运用QPr ...

- Excel多列求平均值

数据源如下所示 需求描述:现在需要根据水果名称和月份求出对应水果的平均单价 一.添加一列辅助列(=A2&B2) 二.Ctrl+A选择所有数据插入数据透视表,选择辅助列到行,客单价到值(值字段设 ...

- [HTML、CSS]知识点

[版权声明]未经博主同意,谢绝转载!(请尊重原创,博主保留追究权) https://blog.csdn.net/m0_69908381/article/details/130176402 出自[进步* ...

- quantus18的signaltap逻辑分析仪

SignalTap的使用 1.SignalTap的作用 SignalTap就是一个IP(对应xilinx的ila),可以将引脚的状态实时显示.这是基于板级的验证,可以有效处理一些仿真难以实现的波形测试 ...

- KingbaseES V8R6 集群运维案例 -- 脚本部署集群后ssh无法连接

案例说明: 在kylin V10环境下,通过脚本方式部署KingbaseES V8R6集群后,发现ssh无法连接主机,通过分析发现在脚本部署过程中会对系统环境进行优化配置,在修改了/etc/ssh/s ...

- #单调栈#CodeChef Meteor

METEORAK 分析 设 \(dp[l][r]\) 表示第 \(l\) 到 \(r\) 行的答案,可以发现它由 \(f[l][r],dp[l][r+1],dp[l+1][r]\) 转移而来. 关键就 ...

- #树状数组,并查集#CF920F SUM and REPLACE

题目 分析 由于\(a_i=1或2\)时\(d(a_i)=a_i\),且其余情况修改后答案只会越来越小, 考虑用树状数组维护区间和,用并查集跳过\(a_i=1或2\)的情况 代码 #include & ...

- 数据库操作入门:PyMongo 和 MongoDB 的基本用法

MongoDB MongoDB是一种流行的NoSQL数据库,它将数据存储在类似JSON的文档中,使数据库非常灵活和可扩展 PyMongo Python需要一个MongoDB驱动程序来访问MongoDB ...

- 上传文件附件时判断word、excel、txt等是否含有敏感词如身份证号,手机号等

上传附件判断word.excel.txt等文档中是否含有敏感词如身份证号,手机号等,其它检测如PDF,图片(OCR)等可以自行扩展. 互联网项目中,展示的数据中不能包含个人信息等敏感信息.判断word ...

- 我只用了3步,实现了一个逼真的3D场景渲染

给3D模型及环境场景渲染出兼具质感和真实感的材质效果,需要经历几步? 显然,目前的3D模型材质渲染技术,还无法实现简单几步就能搞定的标准化作业来量化,完成一个质量过关的3D模型渲染,一般需要: 1.准 ...