Allegro布线基本操作

目录:

一、Allegro基本技巧

1.关闭电源和地网络的飞线

2.开启特定NET飞线

3.元器件快速对齐(待完善)

4.allegro布线完成后如何修改线宽

5.Allegro批量复制Via并保持net属性

6.针对win10系统叠层和Identify DC Nets窗口弹不出来解决方法

7.元件高度的设定与测量

二、快捷键的应用与设置

三、规则设置

四、网表DXF的导入与placement

五、电源PCB注意事项

六、CLK、Chock、MOS、高速信号等注意事项

七、DDR Layout讲解

八、Geber的设置与导出。

1.关闭电源和地网络的飞线

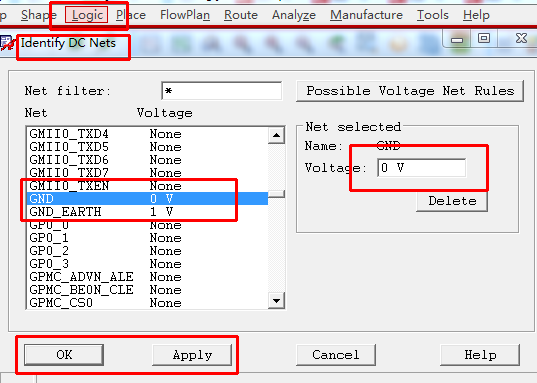

(1)点击Logic-Identify DC Nets,把要关闭的电源和地net设置成相应的电压值,即可关闭。

(2)从Command窗口关闭电源和地的飞线.如下图:

2.开启特定NET飞线

打开未完成的PCB文件,点击菜单栏的DISPLAY->Show RATS->nets。点击你想要显示的VCC\GND元器件的引脚,使未布线完成的电源管脚的连接关系暴露。

3.元器件快速对齐

(1)要在placement模式,框选或者按Shift选择元件,右键align component选项。

注意,如果元件散落成X,Y方向都有可能对齐的样式,软件会选择其中不会造成Align 后元件重叠的那种方向进行对齐。

(2)在top/bottom 的Silkscreen临时画一条线(add line)手动对齐

4.allegro布线完成后如何修改线宽

1.如果要改变整个一条导线的宽度

(1)在find栏里选择Cline;

(2)在PCB中选择要改的导线,点击右键,选择Change Width

(3)在对话框中输入你想要的线宽

2.如果要改变整个导线中某一段导线的宽度

(1)在find栏里选择Cline Segs

(2)在PCB中选择要改的导线,点击右键,选择Change

(3)在对话框中输入你想要的线宽

edit\change,find栏里选上cline,options里有个linewidth在框框中输入你需要的线宽,然后点击需要修改的cline

edit\change,find栏里选上cline,options里有个linewidth在框框中输入你需要的线宽,然后点击需要修改的cline

5.Allegro批量复制Via并保持net属性

使用Allegro时需要批量复制net属性是GND或是其它属性的Via:

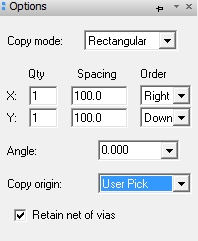

批量选中Via后点击Copy或'Shift+F5'

然后完成复制,如图:

复制完,我们可能发现,这些复制的Via的net属性不是我们想要的GND属性

注意选择上Retain net of vias可以解决这一问题:

该选项允许我们在复制时候保留via的net属性

6.针对win10系统叠层窗口弹不出来解决方法

先右键看有没有done,然后点击层叠,如果没有看到窗口,就按住alt+空格+x,层叠对方框就会跳出。之后缩小窗口,点击OK.

7.元件高度的设定与测量

如何在Allegro中对器件高度设定规则? 在有的设计中,需要设定PCB板上所贴器件的高度规则。比如,超过一定高度,会对该产品在今后的装配带来不便或麻烦。所以,如果我们在项目设计之前就知道类似的一些相关尺寸规定,就可以在设置规则的时候增加一些约束条件。 首先,在制作器件封装的时候,就需要给每个器件定义它的高度:package height。 具体操作是:打开.dra文件,点击Setup—Areas—Package Height,点击器件的Place Bound Top,在Options里面会看到设定器件高度的图示。在相应的位置填入器件的min、max的值,就可以把这些信息记录在该器件的封装里了。 接下来,在.brd里面设置相关规则。 具体操作是:在需要设定相关规则的区域添加一层Route Keepout层,或者Place Bound Top层。然后,同样的按照上面的操作,点击Setup—Areas—Package Height,在Options里面按照示意图,设定相关的规则就行了。 需要注意的是: (1) 首先应该确保所有器件的.dra文件里面都包含了器件高度的设定,否则默认状态下,在placement的时候每个器件都会产生DRC的。如果不知道器件的高度,又不希望那些规则作用在这个器件上,那么可以把最大值设置为0,就可以避免出现不希望看到的DRC。 (2) 如果是采用在Place Bound Top层设定该规则,那么,DRC会产生在相应的Top或者Bottom层;而如果是采用在Route Keepout层设定该规则,那么,DRC会产生在DRC这一列下方的Place Top或者Place Bottom。 (3) 在用不同的层设定该规则的时候示意图的尺寸指示是有所区别的,在设定规则的时候需要注意规则的正确性。 (4) 这种关于器件高度的规则设定是不能够在Setup--Constraints里面通过添加一个Area再在Area里面设定规则来实现的。

如果要对高度设定规则,则需要器件封装中的Place Bound这一层有高度信息。然后在allegro单板设计时,要area中增加如下shape即可

右键添加shape到对应层面后,填入相应要求的高度信息即可

。

8.Allegro中如何更改字体和大小(位号丝印)

1.、更改丝印字体的大小

选择Edit->change按钮,在allegro的右侧出现如下图所示的图标:

若要更改字体大小,只需调整Text block字体大小即可。

2、更改丝印字体的粗细

选择Setup->Design Parameter,再选择Text,即可出现下图所示界面:

再选择Setup Text Sizes,出现下图所示界面:

调整Photo Width,即可达到调整线宽的目的。

9.

Allegro布线基本操作的更多相关文章

- 每天进步一点点------Allegro 布线完成后如何修改线宽

一.如果要改变整个一条导线的宽度 1.在find栏里选择Cline; 2.在PCB中选择要改的导线,点击右键,选择Change Width 3.在对话框中输入你想要的线宽 3.如果要改变整个导线 ...

- Allegro基本操作——PCB布线

转:http://blog.sina.com.cn/s/blog_1538bc9470102vyyq.html http://www.elecfans.com/article/80/110/2010/ ...

- 23.allegro中自动布线[原创]

1. --- 方法①:选择网络自动布线 -- --- 已经步好: --- 方法②: ---- ---- 布线: --- 方法③: -- ----

- 每天进步一点点------Allegro 群组布线

执行Route->connect命令,设置好控制面板中的内容.然后设置同时走线的GROUP包含哪些网络,有两种方法.第一种方法,如果几个网络是紧邻的,可以直接框选,选中的网络就会被包含在GROU ...

- Allegro 快捷键设置

一.快捷键设置 Allegro可以通过修改env文件来设置快捷键,这对从其它软件如AD或PADS迁移过来的用户来说,可以沿用以前的操作习惯,还是很有意义的. Allegro的变量文件一共有2个:一个是 ...

- Allegro学习(http://www.asmyword.com/forum.php?mod=forumdisplay&fid=86)

一.资源 1.网站推荐www.eda365.com,里面有很多有用的东西:当然还有官方代理商的网站http://www.pspice.com.cn/: 2.视频教程:有库源电气的视频教程,还有在www ...

- allegro si(三)

前言:si的教程市面上是很少的,layout是台湾工程师的强项,还有就是日本人,国人爱用AD. si的教程中靠谱的还是张飞的收费课程,还有华为的资料. Cadence SI 仿真实验步骤如下: 1.熟 ...

- Allegro PCB SI (2)

整理一下在电研院学的si (虽然彩超的si在频率15Mhz以上后,si是失真的.昨晚遇到孔大哥也是这样说的,板级仿真,要layout过硬,然后找到合适的top test point) Allegro ...

- allegro使用汇总 [转贴]

1.如何在allegro中取消花焊盘(十字焊盘) set up->design parameter ->shape->edit global dynamic shape parame ...

随机推荐

- 漫谈DNS

文章作者:luxianghao 文章来源:http://www.cnblogs.com/luxianghao/p/6189633.html 转载请注明,谢谢合作. 免责声明:文章内容仅代表个人观点, ...

- 二进制<2>

位运算简介及实用技巧(二):进阶篇(1) ===== 真正强的东西来了! ===== 二进制中的1有奇数个还是偶数个 我们可以用下面的代码来计算一个32位整数的二进制中1的个数的奇偶性, ...

- [UOJ#276]【清华集训2016】汽水

[UOJ#276][清华集训2016]汽水 试题描述 牛牛来到了一个盛产汽水的国度旅行. 这个国度的地图上有 \(n\) 个城市,这些城市之间用 \(n−1\) 条道路连接,任意两个城市之间,都存在一 ...

- [luoguP2601] [ZJOI2009]对称的正方形(二维Hash + 二分 || Manacher)

传送门 很蒙蔽,不知道怎么搞. 网上看题解有说可以哈希+二分搞,也有的人说用Manacher搞,Manacher是什么鬼?以后再学. 对于这个题,可以从矩阵4个角hash一遍,然后枚举矩阵中的点,再二 ...

- BZOJ2333 [SCOI2011]棘手的操作 【离线 + 线段树】

题目 有N个节点,标号从1到N,这N个节点一开始相互不连通.第i个节点的初始权值为a[i],接下来有如下一些操作: U x y: 加一条边,连接第x个节点和第y个节点 A1 x v: 将第x个节点的权 ...

- TCP面试题之为什么需要三次握手才能建立连接/四次挥手才能断开连接

为什么需要三次握手才能建立连接? 答:为了初始化Sequence Number(序列号)的初始值,要通知双方数据包的序号,作为以后通讯的序号,以保证在网络传输过程,不会因为网络原因而导致乱序: 为什么 ...

- UGUI 点击穿透问题

unity上 用 做游戏欢迎界面上通用的ui,然后导到游戏里面直接用,但发现游戏里面是用ngui的,点击ugui 的ui 会穿透过去 ngui会响应,原本模型的点击处理也会响应 我用的 unity 版 ...

- SpringBoot使用Junit4单元测试

SpringBoot2.0笔记 本篇介绍Springboot单元测试的一些基本操作,有人说一个合格的程序员必须熟练使用单元测试,接下来我们一起在Springboot项目中整合Junit4单元测试. 本 ...

- 【CF500D】New Year Santa Network(树上统计)

..]of longint; z:..]of extended; n,i,m,tot,x1:longint; ans,fenmu,y1:extended; procedure add(a,b:long ...

- 《Linux命令行与shell脚本编程大全 第3版》

第一部分 Linux 命令行 第1章 初识Linux she1.1 什么是Linux 21.1.1 深入探究Linux 内核 31.1.2 GNU 工具 61.1.3 Linux 桌面环境 81 ...