Cotex-M3内核LPC17xx系列时钟及其配置方法

一、背景:

最近正在接手一个项目,核心芯片既是LPC17XX系列MCU,内核为ARM的Cotex-M3内核。

想要玩转一个MCU,就一定得搞定其时钟!

时钟对MCU而言,就好比人类的心脏。由其给AHB、APB总线供给血液(时钟频率),而挂在AHB(Advance High Bus)总线上的器件就像是我们的各个器官,挂在APB(Adance Peripheral Bus)总线的外设就像是人类的四肢。各个器官和四肢只有在你的血液(时钟频率)供给恰到好处时才能正常运转。

本篇文章既是对LPC17xx系列的时钟结构及其配置方法做个介绍与总结。

二、正文:

二话不说,先上一张LPC17xx时钟。

由图所示,MCU最原始的时钟动力来自于上图三个地方之一,

osc_clk-->由外接在”XTAL1”,”XTAL2”的晶振来提供时钟源;

rtc_clk-->由外接在”RTCX1”,”RTCX2”的晶振来提供时钟源;

irc_osc-->由MCU内部自带的晶振来提供时钟源。

又由图知,LPC1700系列一共有4大类时钟,

供给CPU直接使用的CCLK时钟;

供给USB使用的usb_clk时钟;

供给看门狗使用的wd_clk时钟;

供给各种外设使用的pclk时钟;

CCLK时钟由主PLL(PLL0)或者直接由三个晶振源之一来提供;

usb_clk时钟由主PLL(PLL0)或者PLL1提供;

pclk时钟由CCLK分频得来;

wd_clk时钟由”rtc_clk” 或者 “irc_osc”提供时钟。

接下来该说如何配置时钟了:

1、 配置CPU时钟(CCLK) :

CPU时钟CCLK若是由PLL0提供的,那么PLL0会先将供给它的时钟进行升频,升频之后,再降频供CPU使用,即CCLK,

至于为何要先升频再降频,暂时未知,也许单纯的是PLL的工作机制吧。以下即配置CPU时钟(CCLK)的具体过程:

a、 描述主振荡器——即主振荡器大小范围多少,有没有稳定等,配置的寄存器为“SCS”。

b、 配置外设时钟:

这里要注意!按照正常思维顺序走的话,“b”这一步应该在所有步骤之后,,但是LPC17xx系列的MCU规定,在enable PLL0前,

要先把外设时钟配置完成,所以,要先配置外设时钟。

PLL0升频再降频后,会生成一个CCLK时钟,该CCLK经过再次分频即可得到所有外设的外设时钟。

外设时钟的配置,既是根据各个外设的时钟需求,来分别独立的对CCLK分频取得。

每个系列MCU均有其最大工作频率CCLK,以不超过该最大工作频率为准,配置CCLK降频(分频)大小的寄存器为“CCLKCFG”。

配置外设时钟的寄存器分别为“PCLKSEL0/1”

在配置外设时钟前,先考虑由PPL0升频多少降频多少才可得到想要的CCLK值,而这实际上是“d”步骤考虑的,所以此处的逻辑

会有点乱。在阅读过程中,可跳过该步骤,直接看“c”步骤,最后跳回来看“b”步骤,但实际操作得按该步骤来。

c、 从这三个振荡器选择供给PLL0的时钟,配置的寄存器为“CLKSRCSEL”。

d、 配置“PLL0CFG”寄存器,来设置PLL0升频值及降频值的大小,寄存器截图如下:

M即是倍频值,N即分频值,当使用晶振源为”rtc_clk”时,M值参照表4.8所建议的值。

PLL0计算方法如下图:

计算PLL0时,各个计算变量参数的意义如下图:

e、 最后使能PLL0时钟并选择是否选用PLL0作为CCLK的输入时钟,操作的寄存器为“PLL0CON”

f、 举个例子:MCU外接晶振为12MHZ,我需要CPU工作在频率100MHZ。那么根据式子,M = 100, N = 6。

Fcco = (2 * 100 * 12MHZ) / 6 =400MHZ。然后4分频,最后得到CCLK为100MHZ。

配置代码如下:

#if (PLL0_SETUP)

LPC_SC->PLL0CFG = PLL0CFG_Val;

LPC_SC->PLL0CON = 0x01; /* PLL0 Enable */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

while (!(LPC_SC->PLL0STAT & (<<)));/* Wait for PLOCK0 */ LPC_SC->PLL0CON = 0x03; /* PLL0 Enable & Connect */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

#endif

2、 USB时钟的配置:

如整体时钟图示,USB时钟只能由PLL0或者PLL1提供,并且!若USB时钟由PLL0提供,那么PLL0的时钟源必须是外部 晶振!

USB需要一个占空比为50%的48MHZ的时钟源,也就是说,PLL1或者PLL0分频出来的时钟Fcco必须为48MHZ的偶数倍数,

以便为USB提供合适的时钟。

A、 若由PLL0提供,那么由“1”步骤配置完PLL0,通过USB分频器获得满足条件的USB时钟即可。

举个例子:USB的CLK要求为48MHZ,那么PLL0主频配置为48MHZ的偶数倍,然后通过USB时钟分频器分频,

来获得符合要求的时钟。

B、 若由PLL1提供,那么就得说说PLL1是如何配置的:

a、 PLL1仅支持10MHZ到25MHZ范围内的时钟输入,且只能是外部时钟源,所以时钟源不用选择;

b、 设置PLL1的“M”值与“P值”,PLL1类似于PLL0,也是会有一个先升频后降频的过程,但可以看出PLL1算是USB的一个

特供时钟源,所以每个值的限制条件会比较多。

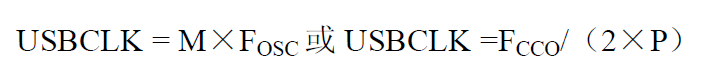

PLL1输出频率的公式:

Fcco频率可按如下公式计算:

注意:

Fosc(时钟源)的频率范围必须为10MHZ~25MHZ,

USBCLK必须为48MHZ,

Fcco的范围为:156MHZ~320MHZ;

举个例子:

输入的外部晶振为12MHZ,配置“M”的值为4,“P”的值为2,按公式计算可得PLL1升频后为192MHZ,然后分频到48MHZ

供给USB使用。

PLL1配置代码如下:

#if (PLL1_SETUP)

LPC_SC->PLL1CFG = PLL1CFG_Val;

LPC_SC->PLL1CON = 0x01; /* PLL1 Enable */

LPC_SC->PLL1FEED = 0xAA;

LPC_SC->PLL1FEED = 0x55;

while (!(LPC_SC->PLL1STAT & (<<)));/* Wait for PLOCK1 */ LPC_SC->PLL1CON = 0x03; /* PLL1 Enable & Connect */

LPC_SC->PLL1FEED = 0xAA;

LPC_SC->PLL1FEED = 0x55;

#else

LPC_SC->USBCLKCFG = USBCLKCFG_Val; /* Setup USB Clock Divider */

#endif

3、 看门狗wd_clk还未使用,下次要配时,再做记录。

三、总结:

不论是cotex-m3内核的LPC17xx系列、STM32系列,还是更高阶的arm9,arm11,时钟才是是摸透它们的最佳切入点。

就实际使用来说,使用MCU既是使用各种外设,或者实现各种通信。不论何种外设,何种通信(UART、IIC、CAN、USB等),

其能正确工作的关键就在于要给定正确合适的时钟。时钟的选法就采用MCU芯片手册上的时钟图来倒推回去,

首先根据外设的需求确定外设时钟,接着考虑CPU的时钟,然后在反推到最初的时钟源的选择。

完毕,在此做个记录,以便下次参考。

记录地点:深圳WZ

记录时间:2016年6月3日

Cotex-M3内核LPC17xx系列时钟及其配置方法的更多相关文章

- Cotex-M3内核STM32F10XX系列时钟及其配置方法

一.背景 最近做个项目,需要使用STM32,还是以前一样的观点,时钟就是MCU心脏,供血即时钟频率输出,想要弄明白一个MCU,时钟是一个非常好的切入点.言归正传,网上已经有太多大神详述过STM32的详 ...

- 国产新芯片连不上J-Link?芯海CS32L010系列芯片JLink配置方法

疫情以来芯片供货紧张,特别是ST的MCU一芯难求.所以很多产品不得不切换成国产.不过也是经过使用后才发现,很多国产芯片的性能还是挺好的.由于芯片比较新,官方J-Link还没有支持,所以调试和烧录有些不 ...

- STM32F2系列时钟的配置

前一节详细介绍了系统默认的时钟配置,及各路时钟输出是多少,这是默认配置的,但实际使用的时钟默认的时钟并不符合要求,所以就得知道如何调用库函数进行配置. 最好的资料就是查阅stm32f2xx_rcc.c ...

- STM32F7系列时钟相关问题:HSE模式配置(旁路模式、非旁路模式

从时钟源的角度,分为两类外部时钟(E)和内部时钟(I).从时钟速率的角度,分为两类高速时钟(HS)和低速时钟(LS).而把它们组合起来就有四种时钟:HSE.HIS.LSE.LSI.至于为什么会有这么复 ...

- STM32入门系列-STM32时钟系统,时钟使能配置函数

之前的推文中说到,当使用一个外设时,必须先使能它的时钟.怎么通过库函数使能时钟呢?如需了解寄存器配置时钟,可以参考<STM32F10x中文参考手册>"复位和时钟控制(RCC)&q ...

- STM32 M3内核的位带操作原理及步骤

STM32 M3内核的位带操作原理及步骤 一.位带操作有什么用?什么是位带操作 位带操作的作用:可以实现对某一GPIO口寄存器(或SRAM内存中)的某一bit位直接写0或1,达到控制GPIO口输出(或 ...

- Spartan6系列之芯片配置模式详解

1. 配置概述 Spartan6系列FPGA通过把应用程序数据导入芯片内部存储器完成芯片的配置.Spart-6 FPGA可以自己从外部非易失性存储器导入编程数据,或者通过外界的微处理器.DSP等对 ...

- [转载]:STM32为什么必须先配置时钟再配置GPIO

转载来源 :http://blog.csdn.net/fushiqianxun/article/details/7926442 [原创]:我来添两句,就是很多同学(包括我)之前搞低端单片机,到了stm ...

- ANDROID Porting系列二、配置一个新产品

ANDROID Porting系列二.配置一个新产品 详细说明 下面的步骤描述了如何配置新的移动设备和产品的makefile运行android. 1. 目录//vendor/创建一个公 ...

随机推荐

- Maven异常:Could not find artifact

用Maven build("clean tomcat7:run" ) Maven聚合工程时,出现了一下问题: [INFO] Scanning for projects... [E ...

- Io 异常: The Network Adapter could not establish the connection 解决方法

1.IP错误: 在设置URL时错误,例如:jdbc:oracle:thin:@192.168.1.80:1521:orcl 数据库服务器是否正确:ping 服务器IP是否通畅.ping不通则将URL更 ...

- Code笔记之:CSS块级元素、内联元素概念

文档流 将窗体自上而下分成一行行, 并在每行中按从左至右的顺序排放元素,即为文档流. 每个非浮动块级元素都独占一行, 浮动元素则按规定浮在行的一端. 若当前行容不下, 则另起新行再浮动. 内联元素也不 ...

- JavaWeb学习总结-01 JavaWeb开发入门

一 基本概念 1 Web开发的相关知识 Web,表示网页的意思,它用于表示Internet主机上供外界访问的资源. Internet上供外界访问的Web资源分为: 静态web资源(如html 页面): ...

- React Native 开发之 (07) 常用组件-View

掌握了React Native的组件就可以使用IOS的原生组件和API. 一 View组件 就像开发web应用程序中,需要使用很多的HTML标签.例如 div,form.但是在基于DIV+CSS布局的 ...

- linux忘记mysql密码找回方法

linux忘记mysql教程密码找回方法 今天我们主要是讲一下关于linux忘记mysql密码处理方法,下面提供了5种linux忘记mysql密码找回方法哦. 方法一: # /etc/init. ...

- python的正则表达式 re-------可以在字符串前加上 r 这个前缀来避免部分疑惑,因为 r 开头的python字符串是 raw 字符串,所以里面的所有字符都不会被转义

正则表达式使用反斜杆(\)来转义特殊字符,使其可以匹配字符本身,而不是指定其他特殊的含义.这可能会和python字面意义上的字符串转义相冲突,这也许有些令人费解.比如,要匹配一个反斜杆本身,你也许要用 ...

- ServiceStack.Text 更快的序列化

Json.net 是以前最经常用的序列化组件,后来又注意到ServiceStack号称最快的,所以我做了以下测试 1)Json.net using System; using System.Colle ...

- win7开防火墙,允许ping通

- JavaScript 日历

效果图: <html> <head> <script language="javascript"> /*@ 解题思路: .计算本月有多少天(先要 ...