基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证

1.预备知识

整数分为短整数,中整数,长整数,本文只涉及到短整数。短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为0表示为正数),取值范围为-127~127。

负数的表示方法为正值的求反又加1。例如:

8’b0000_0100; //表示值:4,正值求反为:8’b1111_1011;再加1表示为:8’b1111_1100,这样便得到了-4的表示方法为:8’b1111_1100。

同理,负值变成正值的方法为:负值求反又加1。

2.设计思路

怎样判断一个短整数是正值还是负值?

利用一个数的最高位,if(!A[7]) //A是正值;if(B[7]) //B是负值。

在乘法运算中,运算结果的符号可以通过异或运算得到。

|

A值 |

B值 |

结果 |

|

正(0) |

正(0) |

正(0) |

|

正(0) |

负(1) |

负(1) |

|

负(1) |

正(0) |

负(1) |

|

负(1) |

负(1) |

正(0) |

3.乘法器程序设计思路

首先考虑输入信号量,有乘数与被乘数,有一个开始指令(Start_Sig),相当于我们在计算器中输入完计算式子之后,再按下一个“=”号,得到最终的结果。

再考虑输出信号量,有计算结果,同时在计算结果出来后,输出一个运算完成信号(Done_Sig)。

乘法运算的Verilog HDL程序实现:以8X5来举例,其中8是被乘数,5是乘数,表示的含义是5个8相加。乘法运算可以拆分成三个步骤来实现:

在运算前,取得乘数和被乘数的符号位,然后取被乘数和乘数的正值。

isNeg <= Multiplicand[7]^Multiplier[7];

Mcand <= Multiplicand[7]?(~Multiplicand+1’b1):Multiplicand;

Mer <= Multiplier[7]?(~Multiplier+1’b1):Multiplier;

4.基于ModelSim的乘法器仿真验证

本文将详细描述ModelSim的配置过程,方便以后查阅。

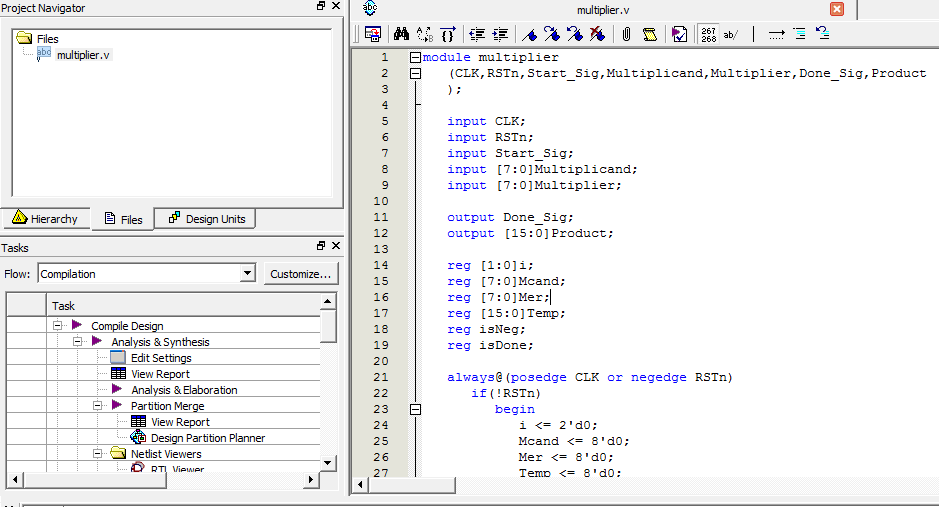

(1)首先建立乘法器的模型,编辑好Verilog HDL程序(学习重点)

(2)关联Quartus与Modelsim-Altera

(2)关联Quartus与Modelsim-Altera

Tools ---- Options ---- EDA Tool Options,选择仿真工具,并添加仿真工具的安装路径。本文选用的Modelsim-Altera。

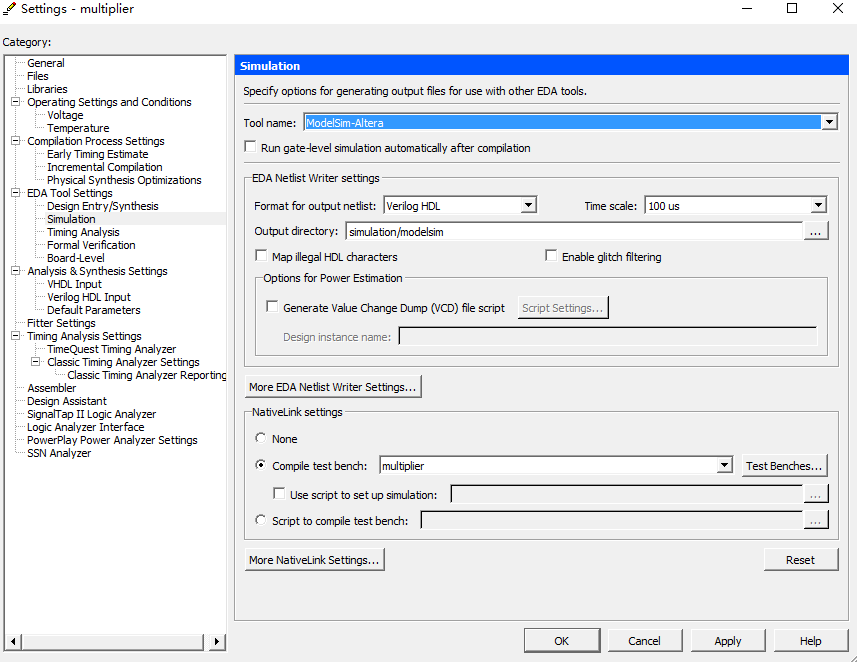

(3)设置仿真工具与需要仿真的文本格式,Time Scale。

Assignments ---- Settings ---- Simulation

Tool name:

Format for output netlist:

Time scale:

Output directory:为默认设置

(4)自动生成Test bench模板

(4)自动生成Test bench模板

Processing ---- Start ---- Start Test Bench Template writer,操作完成后,自动生成Test bench。

打开Test Bench文件,在整个工程文件中会生成一个simulation文件夹,打开,找到里面的“XXX.vt”文件。

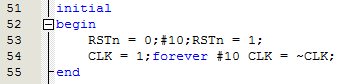

(5)编辑Test bench文件

(5)编辑Test bench文件

按照模板文件中的注释,填充相应的测试程序即可。(里面有大学问)

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

结合“#num”这一参数的变化,与仿真波形的对比,可以得出“#num”是用来设定时间的语句。

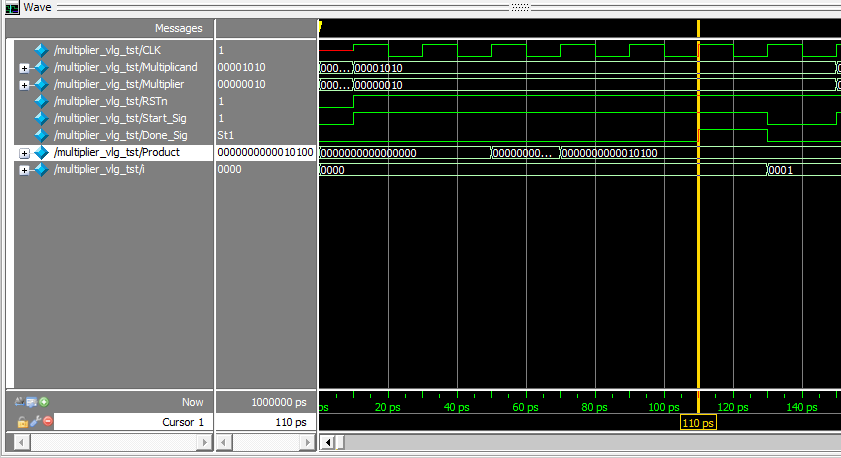

首先谈谈乘法器的工作原理:首先输入乘数与被乘数,当Start_Sig信号置高电平,乘法器开始工作,按照预先写好的模型一步一步运算完后,Done_Sig输出高电平,代表运算完成,得出运算结果输出到Product上。

1.Start_Sig由0跳变到1,乘法器开始运算(相当于计算器上的等号按钮),此时乘数与被乘数输入端口已经有数值,Done_Sig处于st0状态,代表还未完成计算。

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

5.Done_Sig状态又恢复到st0,此刻Start_Sig信号由1变为0,代表乘法器关闭,停止工作,always块语句里面的乘法算法将不再执行。

(6)将编辑好的Test bench文件添加到工程中

Assignments ---- Settings ---- Simulation

选择 Compile test bench选项,单击“...”

New ----

需要填充如下内容:

Test bench name:就是testbench文件的名字,即“.vt”文件的文件名。

Top level module in test bench:就是testbench文件的顶层模块名。

End simulation at:就是仿真最大的时间。

在Test bench files面板中添加Test bench文件,单击“...”找到“.vt”文件的路径,单击add即可,最后单击OK。

单击OK。

单击OK。

单击Apply,单击OK。

单击Apply,单击OK。

(7)开始仿真

Tools ---- Run EDA Simulation Tool ---- EDA RTL Simulation

自动启动ModelSim程序,即可以看到仿真波形。

基于Verilog HDL整数乘法器设计与仿真验证的更多相关文章

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于Verilog语言的可维护性设计技术

[注]本文内容主体部分直接翻译参考文献[1]较多内容,因此本文不用于任何商业目的,也不会发表在任何学术刊物上,仅供实验室内部交流和IC设计爱好者交流之用. “曲意而使人喜,不若直节而使人忌:无善而致人 ...

- 基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器. 全加器的两个 ...

- paper:基于verilog HDL 的高速可综合FSM设计

1.寄存器输出型状态机 VS 组合逻辑输出型状态机 2.状态编码方法 这块讲的不好,也比较少. 3.系统设计中模块划分的指导性原则

- 基于Verilog HDL的二进制转BCD码实现

在项目设计中,经常需要显示一些数值,比如温湿度,时间等等.在数字电路中数据都是用二进制的形式存储,要想显示就需要进行转换,对于一个两位的数值,对10取除可以得到其十位的数值,对10取余可以得到个位的数 ...

- 基于Verilog HDL的ADC0809CCN数据采样

本实验是用ADC0809CCN进行数据采样,并用7段数码管进行显示. ADC0809由一个8路模拟开关.一个地址锁存与译码器.一个A/D转换器和一个三态输出锁存器组成.多路开关可选通8个模拟通道,允许 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

随机推荐

- Typescript中的class interface 只是在声明,其实什么也没有干!

由于vue.js的特殊机制,初始化后给对象添加的属性是无法更新UI的. 最近结合typescript和vue进行web开发,就遇到了这样的坑. class user{ name:string; age ...

- 使用easeui dialog弹出框中使用CKeditor多次加载后无法编辑问题

问题呈现:弹出框页面 <tr class="addtr"> <th>内容</th> <td> <!-- <textare ...

- hadoop2的高可用性

1 hadoop2 namenode由一个节点变成两个节点,同时在线,且同时只有一个是活跃的,如果一个出了问题,另外一个立即接替:没必要配置Secondary NameNode.Checkpoi ...

- Exception mybatis 配置文件:<typeAlias alias="***" type="***"/> 重复配置

INFO - Destroying singletons in org.springframework.beans.factory.support.DefaultListableBeanFactory ...

- JXL操作Excel

jxl是一个韩国人写的java操作excel的工具, 在开源世界中,有两套比较有影响的API可 供使用,一个是POI,一个是jExcelAPI.其中功能相对POI比较弱一点.但jExcelAPI对中文 ...

- C#求任意范围内的质数

class Program { public static List<int> list; static void Main(string[] args) { Console.WriteL ...

- 实现TabelView的多个cell布局

- (void)viewDidLoad { [super viewDidLoad]; self.LabelArray=[[NSMutableArray alloc]initWithObjects:@& ...

- 收拾那掉了一地的session

多个页面有如下多个session,本来可能是如下面这样的 Session["UId"] = 10; Session["UName"] = "test& ...

- 微信公众号红包接口开发PHP开发 CA证书出错,请登陆微信支付商户平台下载证书

微信红包接口调试过程中一直提示“CA证书出错,请登陆微信支付商户平台下载证书”,经反复调试,大致解决方法如下: 1.首先确保CA证书的路径是否正确,一定得是绝对路径,因为是PHP开发的,这里需要三个p ...

- Linux下的五个查找命令:grep、find、locate、whereis、which

原文转自 http://www.cnblogs.com/wanqieddy/archive/2011/07/15/2107071.html 1.grep grep(General Regular Ex ...