I2S音频总线学习

IIS音频总线学习(一)数字音频技术

一、声音的基本概念

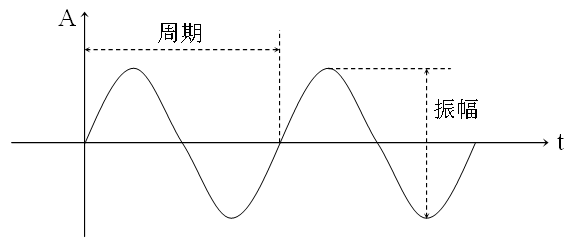

声音是通过一定介质传播的连续的波。

重要指标:

- 振幅:音量的大小

- 周期:重复出现的时间间隔

- 频率:指信号每秒钟变化的次数

声音按频率分类:

声音的传播携带了信息,它是人类传播信息的一种主要媒体。 声音的三种类型:

- 波形声音:包含了所有声音形式

- 语音:不仅是波形声音,而且还有丰富的语言内涵(抽象→提取特征→意义理解)

- 音乐:与语音相比,形式更规范。音乐是符号化的声音。

二、声音的数字化

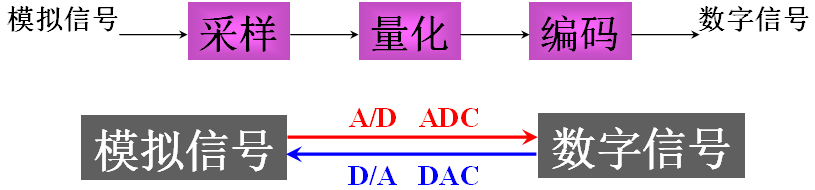

1.声音信号的类型

- 模拟信号(自然界、物理)

- 数字信号(计算机)

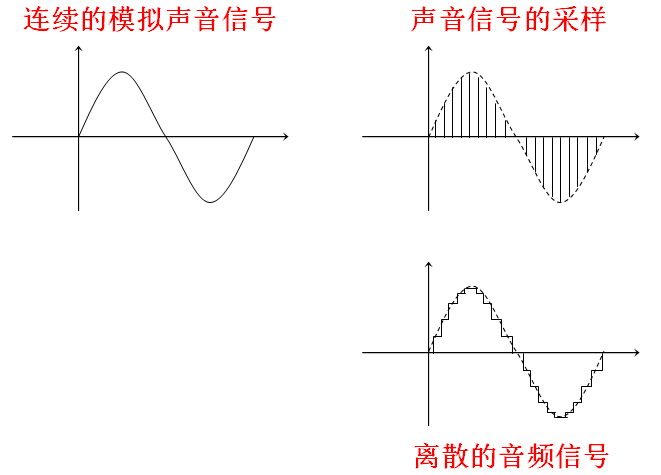

2.声音数字化过程

3.声音数字化过程示意图

4.声音数字化三要素

|

采样频率 |

量化位数 |

声道数 |

|

每秒钟抽取声波幅度样本的次数 |

每个采样点用多少二进制位表示数据范围 |

使用声音通道的个数 |

|

采样频率越高 声音质量越好 数据量也越大 |

量化位数越多 音质越好 数据量也越大 |

立体声比单声道的表现力丰富,但数据量翻倍 |

|

11.025kHz 22.05 kHz 44.1 kHz |

8位=256 16位=65536 |

单声道 立体声 |

5.声音数字化的数据量

音频数据量=采样频率×量化位数×声道数/8(字节/秒)

|

采样频率 (kHz) |

量化位数 (bit) |

数据量(KB/s) |

|

|

单声道 |

立体声 |

||

|

11.025 |

8 |

10.77 |

21.35 |

|

16 |

21.53 |

43.07 |

|

|

22.05 |

8 |

21.53 |

43.07 |

|

16 |

43.07 |

86.13 |

|

|

44.1 |

8 |

43.07 |

86.13 |

|

16 |

86.13 |

172.27 |

|

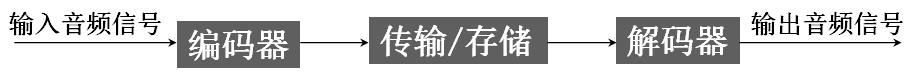

三、音频的文件格式

1.WAV文件

WAV是Microsoft/IBM共同开发的PC波形文件。因未经压缩,文件数据量很大。

特点:声音层次丰富,还原音质好

2.MP3文件

MP3(MPEG Audio layer3)是一种按MPEG标准的音频压缩技术制作的音频文件。

特点:高压缩比(11:1),优美音质

3.WMA文件

WMA(Windows Media Audio)是Windows Media格式中的一个子集(音频格式)。

特点:压缩到MP3一半

4.MIDI文件

MIDI(乐器数字接口)是由一组声音或乐器符号的集合。

特点:数据量很小,缺乏重现自然音

四、数字音频压缩标准

1.音频压缩方法概述

压缩编码技术是指用某种方法使数字化信息的编码率降低的技术

音频信号能压缩的基本依据:

①声音信号中存在大量的冗余度;

②人的听觉具有强音能抑制同时存在的弱音现象。

音频信号压缩编码的分类:

①无损压缩(熵编码)

霍夫曼编码、算术编码、行程编码

②有损压缩

波形编码--PCM、DPCM、ADPCM 、子带编码、矢量量化

参数编码--LPC

混合编码--MPLPC、CELP

2.音频压缩技术标准

|

分类 |

标准 |

说明 |

|

电话语 音质量 |

G.711 |

采样8kHz,量化8bit,码率64kbps |

|

G.721 |

采用ADPCM编码,码率32kbps |

|

|

G.723 |

采用ADPCM有损压缩,码率24kbps |

|

|

G.728 |

采用LD-CELP压缩技术,码率16kbps |

|

|

调幅广 播质量 |

G.722 |

采样16kHz,量化14bit,码率224(64)kbps |

|

高保真 立体声 |

MPEG 音频 |

采样44.1kHz,量化16bit,码率705kbps (MPEG三个压缩层次,384-64kbps) |

五、声卡

1.声卡的主要功能

声卡是负责录音、播音和声音合成的一种多媒体板卡。其功能包括:

①录制、编辑和回放数字音频文件

②控制和混合各声源的音量

③记录和回放时进行压缩和解压缩

④语音合成技术(朗读文本)

⑤具有MIDI接口(乐器数字接口)

2.芯片类型

- CODEC芯片(依赖CPU,价格便宜)

- 数字信号处理器DSP(不依赖CPU)

I2S音频总线学习(二)I2S总线协议

一、I2S总线概述

音响数据的采集、处理和传输是多媒体技术的重要组成部分。众多的数字音频系统已经进入消费市场,例如数字音频录音带、数字声音处理器。对于设备和生产厂家来说,标准化的信息传输结构可以提高系统的适应性。I2S(Inter—IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。

二、I2S总线规范

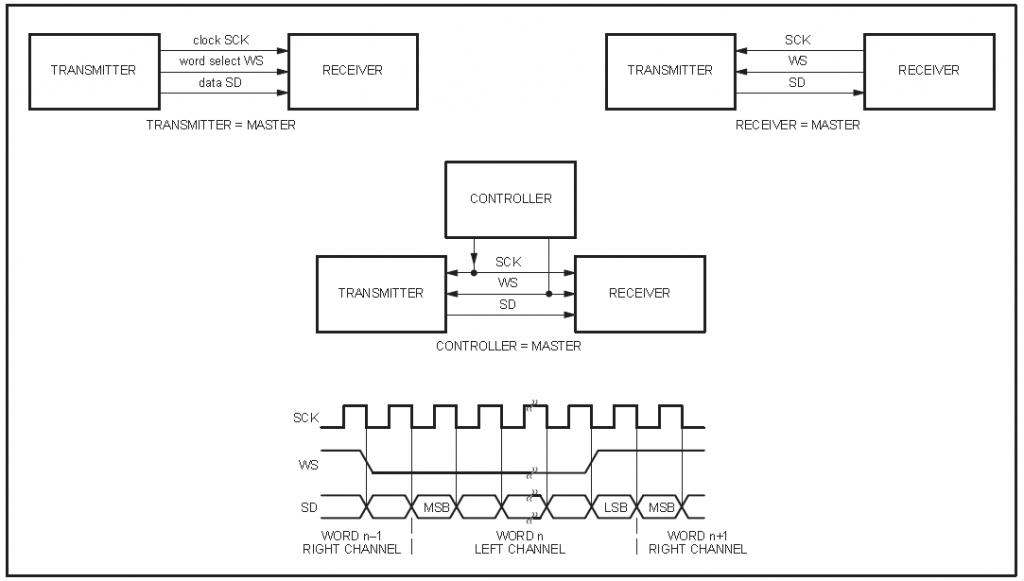

I2S总线拥有三条数据信号线:

1、SCK: (continuous serial clock) 串行时钟

对应数字音频的每一位数据,SCK都有1个脉冲。SCK的频率=2×采样频率×采样位数。

2、WS: (word select) 字段(声道)选择

用于切换左右声道的数据。WS的频率=采样频率。

WS为“1”表示正在传输的是左声道的数据。

WS为“0”表示正在传输的是右声道的数据。

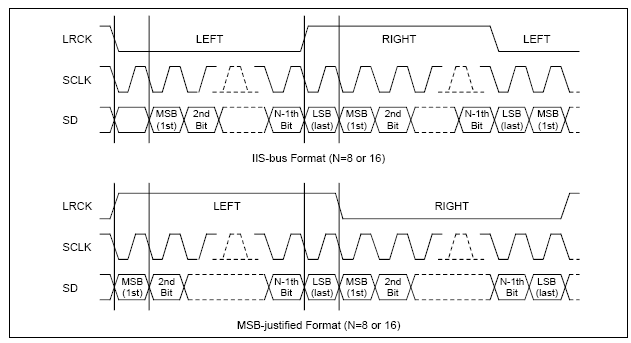

WS可以在串行时钟的上升沿或者下降沿发生改变,并且WS信号不需要一定是对称的。在从属装置端,WS在时钟信号的上升沿发生改变。WS总是在最高位传输前的一个时钟周期发生改变,这样可以使从属装置得到与被传输的串行数据同步的时间,并且使接收端存储当前的命令以及为下次的命令清除空间。

3、SD: (serial data) 串行数据

用二进制补码表示的音频数据。 I2S格式的信号无论有多少位有效数据,数据的最高位总是被最先传输(在WS变化(也就是一帧开始)后的第2个SCK脉冲处),因此最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。也就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。当然,对I2S格式来说数据长度可以不同。

另一个基本的接口时序图可以参看图2所示:

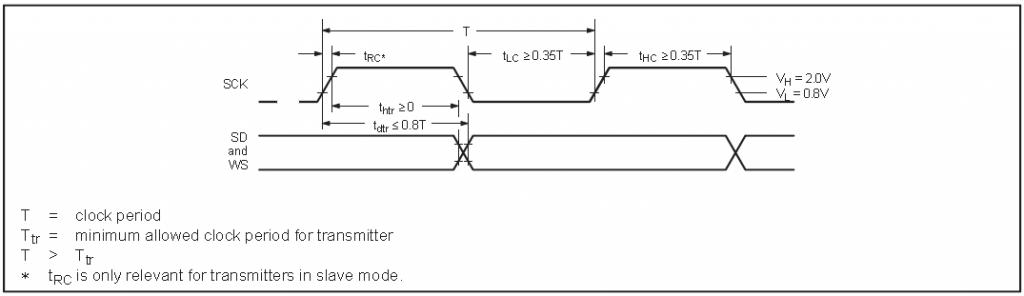

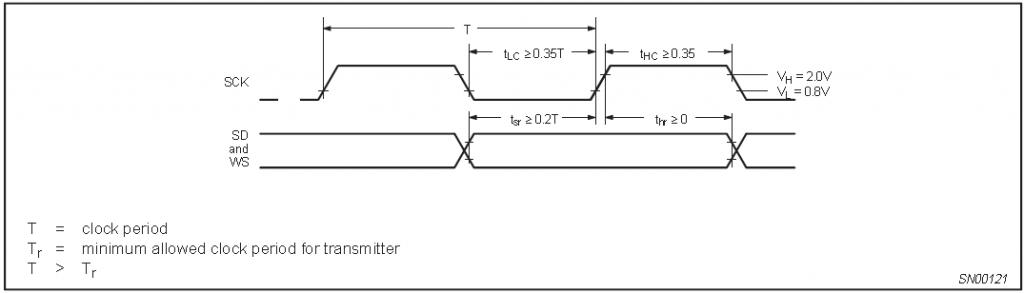

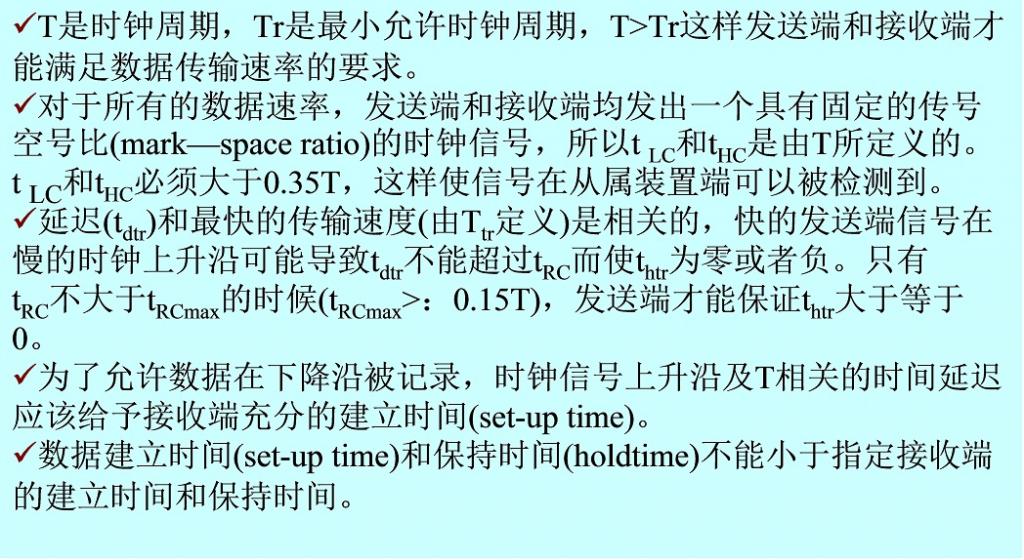

4、时序要求

1.外部时钟和从设备的内部时钟之间的延迟

2.内部时钟和数据信号以及命令选择信号之间的延迟

对于数据和命令信号的输入,外部时钟和内部时的延迟不占据主导的地位,它只是延长了有效的建立时间(set-up time)。延迟的主要部分是发送端的传输延迟和设置接收端所需的时间。见图3和图4:

5、电气特性

输出电压:

VL <0.4V

VH>2.4V

输入电压

VIL=0.8V

VIH=2.0V

注:目前使用的TTL电平标准,随着其他IC(LSI)的流行,其他电平也会支持。

I2S音频总线学习(三)S3C2440的I2S控制器

一、I2S控制器结构框图

- 总线接口,寄存器组和状态机(BRFC):总线接口逻辑和FIFO 访问由状态机控制。

- 5 位双预定标器(IPSR):一个预定标器用于IIS 总线接口的主时钟发生器,另外一个用作外部编解码时钟发生器。

- 64 位FIFO(TxFIFO 和RxFIFO):在发送数据传输时,数据写到TxFIFO;在接收数据传输时,从RxFIFO 读取数据。

- 主IISCLK 发生器(SCLKG):在主设备模式,串行位时钟是从主时钟生成。

- 通道发生器和状态机(CHNC):IISCLK 和iislrck 是由通道状态机生成并控制。

- 15 位移位寄存器(SFTR):在发送模式下并行数据移位成串行数据输出,在接收模式下串行数据输入移位成并行数据。

二、发送接收模式

1.通常传输

IIS 控制寄存器对于发送接收FIFO 有一个FIFO 准备标志位。当FIFO 准备发送数据时,如果FIFO 非空,FIFO 准备标志位置1。如果FIFO 为空,FIFO 准备标志位置0。当接收FIFO非满,对于接收FIFO 的FIFO 准备标志位置1。其指出FIFO 准备好接收数据。如果接收FIFO 为满,FIFO 准备标志置0。这些标志用于决定CPU 读写FIFO 的时间。用这种方法当CUP 在访问发送接收FIFO 时,串行数据能被发送和接收。

2.DMA 传输

在此模式下,发送或接收FIFO 对DMA 控制器是可访问的。在发送或接收模式下的DMA服务请求是由FIFO 准备标志自动执行。

3.发送和接收模式

在此模式下IIS 总线接口可以同时接收和发送数据。在OSS驱动中使用该模式。

三、音频串行接口格式

1.IIS 总线格式

IIS 总线有四线包括串行数据输入(IISDI),串行数据输出(IISDO),左右通道选择(IISLRCK)和串行位时钟(IISCLK)。生成IISLRCK 和IISCLK 的设备是主设备。串行数据以2 的补码发送,MSB(Most Significant Bit 最高位)先发。因为发送器和接收器可能有不同的字长,MSB(最高位)先发。发送器不必知道接收器可以处理多少位,接收器也不必知道会收到多少位。当系统字长大于发生器的字长,字为了数据发送而被截断(最低位被置0)。如果接收器接收大于其字长的位,在LSB(最低位)后的位被忽略。另外,如果接收器收到的位数小于其字长,缺少的位被置0。因此MSB 有一个固定的位置,而LSB 的位置取决于字长。只要IISLRCK 发送改变,发送器在一个时钟周期内发送下一个字的MSB。由发送器发送的串行数据可以和时钟信号的下降沿和上升沿同步。但是,串行数据必须在串行时钟信号的上升沿锁存到接收器。因此当同步上升沿的数据发送时有一些限制。左右通道选择线指出了正在发送的通道。IISLRCK 可以在串行时钟的下降沿或上升沿被改变,当时其不需要对称。在从设备,信号在串行时钟的下降沿或上升沿被锁存。在MSB 被发送,IISLRCK 线改变一个时钟周期。此允许发送器导出用于建立发送的串行数据同步时序。此外,其使能接收存储前一个字且为下一个字的接收清除输入。

2.MSB JUSTIFIED 格式

MSB JUSTIFIED 总线格式在结构上和IIS 总线格式。唯一和IIS 总线格式的区别,MSB JUSTIFIED 格式实现了只要IISLRCK 改变,发送器总是发送下一个字的MSB。

四、IIS采集频率和主设备时钟

I2S主设备时钟频率可以通过采样频率来选择,这是因为I2S主设备时钟频率是由I2S分频器产生的(主设备时钟频率=PCLK/预分频器值),因此必须选择合适的预分频值和CODECLK的采样频率类型(256fs或384fs),才能获得合适的I2SLRCK频率(I2SLRCK频率=主设备时钟频率/CODECLK)。

串行位采用频率类型(16/32/48fs)可以通过配置信道的串行位数和CODECLK采样频率类型来完成(串行位时钟频率类型=CODECLK的采用类型/串行数据位数)。

五、IIS 总线接口特殊寄存器

I2S相关的寄存器包括I2S控制寄存器I2SCON、I2S模式寄存器I2SMOD、I2S分频寄存器I2SPSR、I2SFCON寄存器和FIFO寄存器。

1)I2SCON控制寄存器

I2SCON控制寄存器物理地址为0x55000000,可读/写,复位后值为0x100。寄存器各个比特位意义如下:

[8] 左右声道标记,0=左声道,1=右声道;

[7] 发送FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[6] 接收FIFO就绪标记,取0时表示没有就绪,取1时表示FIFO就绪;

[5] 发送DMA请求使能,取0时请求禁止,取1时请求使能;

[4] 接收DMA请求使能,取0时请求禁止,取1时请求使能;

[3] 发送通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[2] 接收通道空闲命令,在空闲状态(暂停传输)时,I2SLRCK是不激活的,0表示I2SLRCK产生,1表示不产生;

[1] I2S预分频器使能,取0时预分频器禁止,取1时预分频器使能;

[0] I2S接口使能,取0时I2S禁止,取1时I2S使能。

2)I2SMOD模式寄存器

I2SMOD模式寄存器物理地址为0x55000004,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[8] 主从模式选择,取0时为主模式,取1时为从模式;

[7:6] 发送/接收模式选择,00=无,01=接收模式,10=发送模式,11=发送/接收模式;

[5] 左右通道优先级,取0时右通道高左通道低,取1时右通道低左通道高;

[4] 串行接口格式,取0时I2S兼容格式,取1时MSB可调格式;

[3] 每通道串行数据位,取0时8位,取1时16位;

[2] 主时钟频率选择,取0时主时钟是256fs(采样频率),取1时为384fs;

[1:0] 串行位时钟频率选择,00=位时钟是16fs,01=位时钟是32fs,10=位时钟是48fs,11=未定义。

3)I2S分频寄存器I2SPSR

I2S分频寄存器物理地址为0x55000008,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[9:5] A预分频值,预分频器A的除因子,I2S总线接口主时钟=MCLK/A预分频因子;

[4:0] B预分频值,预分频器B的除因子,外部CODEC时钟=MCKL/B预分频因子。

4)I2SFCON寄存器

I2SFCON寄存器物理地址为0x5500000C,可读/写,复位后值为0x000。寄存器各个比特位意义如下:

[15] 发送FIFO访问模式选择,取0时工作于普通模式,取1时工作在DMA模式;

[14] 接收FIFO访问模式选择,取0时工作于普通模式,取1时工作在DMA模式;

[13] 控制发送FIFO使能,取1时使能,取0时禁止;

[12] 控制接收FIFO使能,取1时使能,取0时禁止;

[11:6] 发送端FIFO数据计数,计数值0~32;

[5:0] 接收端FIFO数据计数,计数值0~32。

5)FIFO寄存器I2SFIF

FIFO寄存器物理地址为0x55000010,可读/写,复位后值为0x000。寄存器各个比特位意义如下:I2S总线接口在发送/接收模式有两个64字节的FIFO,每个FIFO由宽16、深32的表组成,并且每个FIFO单元可以分别操作高字节或低字节。通过FIFO入口访问发送和接收FIFO,入口地址为0x55000010。

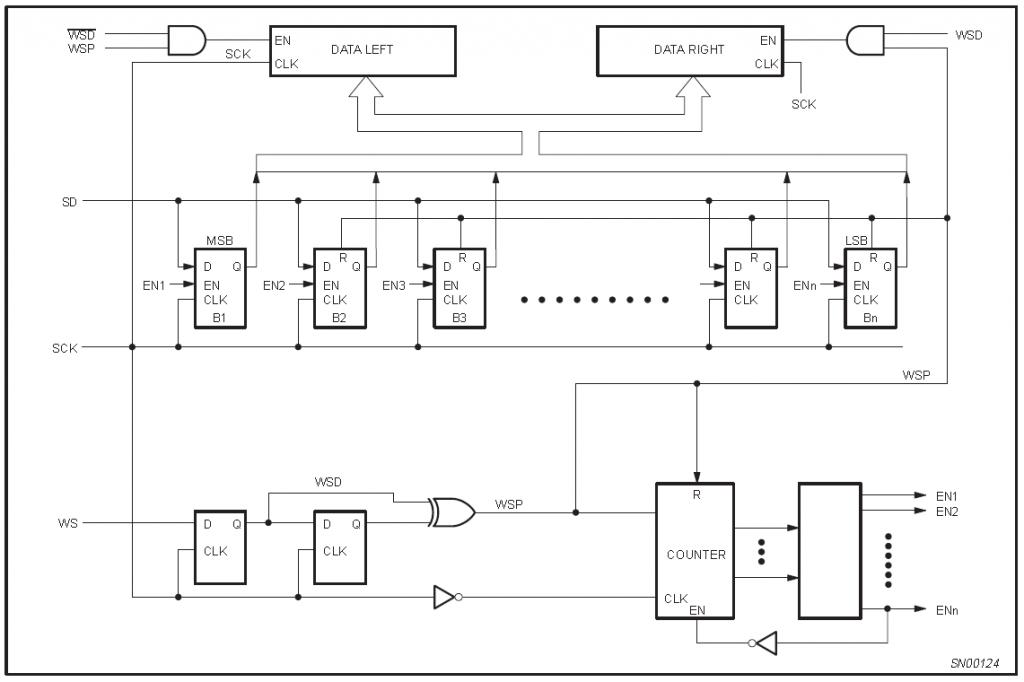

I2S音频总线学习(四)I2S接口设计

一、数据发送端的设计

二、数据接收端的设计

I2S音频总线学习的更多相关文章

- I2S音频总线学习(二)I2S总线协议

http://blog.csdn.net/ce123_zhouwei/article/details/6919954

- 关于音频总线IIS的学习---Verilog

关于音频总线IIS的学习---Verilog 主要思想: 在分析寄存器的值变化的时候,将时钟的边沿分两边来看,边沿之前,边沿之后,在always 块语句里面用来分析判断的寄存器的值,都应该用边沿变化之 ...

- 第38章 I2S—音频播放与录音输入—零死角玩转STM32-F429系列

第38章 I2S—音频播放与录音输入 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/ ...

- Xilinx AXI总线学习(1)

Xilinx AXI总线学习 1. AXI GPIO 采用的是AXI4-Lite接口 AXI GPIO Block Diagram Block design: 端口描述: AXI GPIO核有哪些寄存 ...

- Avalon总线学习 ---Avalon Interface Specifications

Avalon总线学习 ---Avalon Interface Specifications 1.Avalon Interfaces in a System and Nios II Processor ...

- CAN总线学习系列之三——CAN控制器的选择

CAN总线学习系列之三——CAN控制器的选择 在进行CAN总线开发前,首先要选择好CAN总线控制器.下面就比较一些控制器的特点. 一些主要的CAN总线器件产品 制造商 产品型号 器件功能及特点 Int ...

- CAN总线学习系列之二——CAN总线与RS485的比较

CAN总线学习系列之二——CAN总线与RS485的比较 上 一节介绍了一下CAN总线的基本知识,那么有人会问,现在的总线格式很多,CAN相对于其他的总线有什么特点啊?这个问题问的好,所以我想与其它总线 ...

- CAN总线学习系列之— CAN总线特点介绍

CAN总线学习系列之— CAN总线特点介绍 CAN 总线作为一种工业界的流行总线广泛应于工业自动化.多种控制设备.交通工具.医疗仪器以及建筑.环境控制等各个行业中,它是是一种多主机局域网,所以这样 一 ...

- CAN总线学习总结——错误帧和错误状态

CAN总线学习总结——错误帧和错误状态 标签: 数据 / 错误帧 / 错误状态 / CAN总线 / 总线协议 253 一.五种CAN总线可能发生的错误 1.CRC错误: 接收节点计算出的CRC校验值, ...

随机推荐

- mysql之Navicat工具、pymysql模块

1. IDE工具介绍(Navicat) 为了方便测试,使用IDE工具,就是Navicat,这个工具本质上就是一个socket客户端,可视化的连接mysql服务端的一个工具,并且是图形界面版的.它和直接 ...

- Mysql数据库单表查询

1.单表查询语法 #查询数据的本质:mysql会到你本地的硬盘上找到对应的文件,然后打开文件,按照你的查询条件来找出你需要的数据.下面是完整的一个单表查询的语法 select * from,这个sel ...

- Berlekamp-Massey算法学习笔记

Berlekamp-Massey算法 很久之前就听说过这个算法,当时六校联考的时候Day1T1是一道很有意思的递推,神仙zzx不会做于是就拿BM算法艹出了递推式Orzzzzzzzzzzx 推荐一篇讲的 ...

- 3038 3n+1问题

3038 3n+1问题 时间限制: 1 s 空间限制: 32000 KB 题目等级 : 白银 Silver 题解 题目描述 Description 3n+1问题是一个简单有趣而又没有 ...

- imooc《JavaScript深入浅出》上的一个 arraysSimilar 函数

任务 请在 index.html 文件中,编写 arraysSimilar 函数,实现判断传入的两个数组是否相似.具体需求: 数组中的成员类型相同,顺序可以不同.例如 [1, true] 与 [fal ...

- 【代码笔记】Web-ionic-头部与底部

index代码: <!DOCTYPE html> <html> <head> <meta charset="utf-8"> < ...

- Flume初入门简单配置与使用

1.Flume在集群中扮演的角色 Flume.Kafka用来实时进行数据收集,Spark.Storm用来实时处理数据,impala用来实时查询. 2.Flume框架简介 1.1 Flume提供一个分布 ...

- Linux 学习笔记之超详细基础linux命令 Part 13

Linux学习笔记之超详细基础linux命令 by:授客 QQ:1033553122 ---------------------------------接Part 12---------------- ...

- Kotlin入门(9)函数的基本用法

上一篇文章介绍了Kotlin新增的空安全机制,控制语句部分可算是讲完了,接下来将连续描述Kotlin如何定义和调用函数,本篇文章先介绍函数的基本用法. 前面几篇文章介绍控制语句之时,在setOnCli ...

- SpringCloud+Feign环境下文件上传与form-data同时存在的解决办法

最近项目转型使用SpringCloud框架下的微服务架构,各微服务之间使用Feign进行调用.期间,发现若被调用方法涉及到文件上传且仅存在单个文件时,一切正常,代码片段如下: @RequestMapp ...