Fast exit from dram self-refresh

Embodiments of the invention describe a dynamic random access memory (DRAM) device that may abort a self-refresh mode to improve the exit time from a DRAM low power state of self-refresh. During execution of a self-refresh mode, the DRAM device may receive a signal (e.g., a device enable signal) from a memory controller operatively coupled to the DRAM device. The DRAM device may abort the self-refresh mode in response to receiving the signal from the memory controller.

FIELD

Embodiments of the invention generally pertain to electronic devices, and more particularly to systems, apparatuses and methods to improve the exit time from a dynamic random access memory (DRAM) low power state of self-refresh.

BACKGROUND

Memory cells in a DRAM device include a transistor and a capacitor to store a bit of data. The memory cells are 'dynamic' because their data decays and becomes invalid due to various leakage current paths to surrounding cells and to the substrate of the device. To keep the data in the cells valid, each memory cell is periodically refreshed.

Every row of cells in a DRAM memory array needs to be refreshed before the data in the row decays to an invalid state. There are two types of refreshes: external refreshes and internal refreshes (i.e., the DRAM device places itself in self-refresh mode).

During internal DRAM memory refreshes, the memory controller has no visibility to when this refresh is initiated. As a result, the controller is designed to wait for an entire refresh cycle (tRFC, plus a guard band, e.g., 10 ns) before issuing a command to the DRAM. The time period a memory controller must wait before issuing a valid command is herein referred to as tXS (i.e., tRFC+10 ns). tRFC for a 2 Gbit device is in the range of 160 ns. The tRFC approximately doubles as DRAM devices increase in density (e.g., tRFC for a 4 GBit device is in the range of 300 ns, tRFC for an 8 Gbit device is in the range of 550 ns), thus increasing tXS.

Therefore it is desirable to reduce the value of tXS for DRAM devices in order to reduce the time a memory controller must wait before issuing valid commands.

DESCRIPTION

Embodiments of the invention describe a DRAM device that may abort a self-refresh mode to improve the exit time from a DRAM low power state of self-refresh. A self-refresh mode is to be understood as a mode to refresh rows of a DRAM device. This mode is managed internally by the DRAM—the DRAM controller has no visibility to when the refresh mode is initiated.

In the prior art, the DRAM controller is designed to wait for a refresh cycle (tRFC) to complete (tRFC plus and a guard band value, e.g. 10 ns) before issuing a command to the DRAM. By enabling a DRAM device to abort a self-refresh mode, the DRAM controller has a significantly shorter wait period before it may issue a command to the DRAM. In one embodiment, a DRAM device is enabled by the memory controller to abort self-refresh modes in order to maintain the option of the DRAM device functioning according to the prior art (i.e., execute a full self-refresh cycle).

FIG. 1 is a block diagram of selected components of a computing system utilizing an embodiment of the invention. Computing system 100 includes a plurality of processors (e.g., central processing units and/or cores) 150-1through 150-n, memory controller 110, memory 115 including (at least one) DRAM memory device 130, and interconnect 120. Memory controller 110controls, at least in part, the transfer of information between system components and memory 115, and thus the transfer of information between system components and DRAM memory 130. Said system components may include processors 150-1 through 150-n, an input/output device (e.g., a peripheral component interconnect (PCI) Express device), memory itself, or any other system component that requests access to memory 115. In other embodiments, memory controller 110 may be included (or integrated) with a system processor.

Both memory controller 110 and DRAM device 130 may cause a refresh of the DRAM memory cells to occur. Memory controller 110 may issue a command to DRAM device 130 to refresh some or all of its memory cells. DRAM device 130 may also execute a "self-refresh" mode—essentially a plurality of commands to refresh the cells of the device (e.g., each command may execute a refresh of a plurality of rows).

In this embodiment, memory controller 110 is responsible for "enabling" DRAM 130 (e.g., asserting a "clock enable" signal). DRAM 130 may abort an executing self-refresh mode in response to receiving the enable signal from memory controller 110(or a dedicated signal from memory controller 110 initialing the exit from self-refresh mode). It is to be understood that aborting an executing self-refresh mode allows for a significant reduction in the time memory controller 110 must wait before issuing a valid command (i.e., tXS). Thus, aborting a self-refresh mode is also referred to herein as a fast exit from DRAM self refresh. Operations describing how DRAM 130 may abort said self-refresh mode are described below.

DRAM device 130 may require memory controller 110 to "enable" the device to abort self-refresh modes (i.e., enable "fast exit" mode for the device). If the "fast exit" mode is not enabled, then DRAM device 130 will not abort the self-refresh mode. Memory controller 110 will be aware if "fast exit" mode is or is not enabled, and adjust the timing of issuing commands to the DRAM device accordingly.

FIG. 2 is a block diagram of components of a DRAM device utilizing an embodiment of the invention. In this example, a DRAM memory includes (at least one) double-data rate (DDR) 4×4 device 200. DRAM device 200 may include plurality of memory banks 201-216 (other embodiments may be utilized by devices including more or less banks). Memory banks 201-216 may have differing types of memory cells in some embodiments (e.g., one type of memory cell may be faster than others or may consume more or less power compared with other memory cell types). Moreover, various types of DRAM may be utilized for the memory banks shown in FIG. 2, including for example, Graphics DRAM, Fast DRAM, Low Power DRAM, etc.

Banks 201-216 may be organized within four bank groups, each group including four banks (i.e., group 201-204, 205-208,209-212 and 213-216). In this example, 32 bits of data are transferred for every read or write access.

According to the DDR3 specification (as defined by JEDEC JESD79-3) the refresh period is 64 ms and refresh interval is 7.8 us. This translates to 8K refresh commands during the refresh period (64 ms/7.8 us=8K). In this example, DRAM device200 has 32K rows per bank; thus each refresh command will refresh four rows of memory (32K/8K=4).

A self-refresh mode executed by DRAM device 200 may be aborted during the execution of a refresh command (i.e., during the refresh of four rows of memory in this embodiment). It is to be understood that when DRAM device 200 receives an indication to abort a self-refresh mode (e.g., a device enable signal from the DRAM controller, a dedicated signal from the controller to abort the self-refresh, etc.), it may increase the efficiency of subsequent self-refresh mode executions to keep track of which rows were able to be refreshed, and which rows have yet to be refreshed. Row refreshes may be kept track of through row address counter 250 containing bits B14-B0—because there are 32 k rows per bank, DRAM device 200would require 15 row address bits for row address counter 250.

Because four rows of memory are refreshed per refresh command in this embodiment, two bits (e.g., B0 and B1) may indicate the specific row to refresh, and the remaining bits indicate which bank group and bank includes the row to be refreshed. In this example, at the start of each refresh command, bits B1 and B0 are 00. If a refresh command is issued then the remaining row address bit segment (e.g., B14-B2) is incremented by one and bits B1 and B0 cycle thru 00, 01, 10 and 11. This assumes that four rows of memory are refreshed in all the banks.

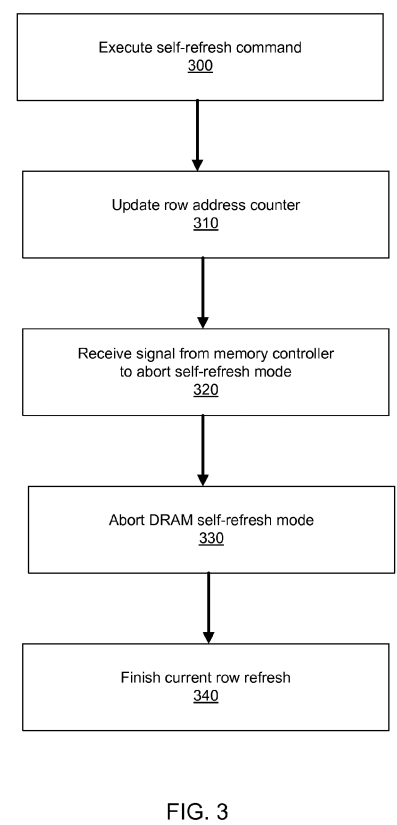

FIG. 3 is a flow diagram of an embodiment of the invention. Flow diagrams as illustrated herein provide examples of sequences of various process actions. Although shown in a particular sequence or order, unless otherwise specified, the order of the actions can be modified. Thus, the illustrated implementations should be understood only as examples, and the illustrated processes can be performed in a different order, and some actions may be performed in parallel. Additionally, one or more actions can be omitted in various embodiments of the invention; thus, not all actions are required in every implementation. Other process flows are possible. Operations described below may be executed via logic, circuitry or modules included in a DRAM device.

A self refresh mode is executed on a DRAM device, 300. The self refresh mode may be a plurality of commands, each command to refresh a plurality of rows of the DRAM device (e.g., 4 rows per command as described above).

The self-refresh mode may include commands to update a row address counter after each DRAM row is refreshed, 310. As describes above, the row address counter may indicate the rank, device and bank that includes the DRAM row that is to be refreshed.

An signal from a memory controller operatively coupled to the DRAM device indicating the self refresh mode is to be aborted may be received, 320. In one embodiment, this signal is a device enable signal. In other embodiments, the signal is a dedicated signal indicating the self-refresh mode is to be exited. The self-refresh mode is aborted in response to receiving the signal, 330. The DRAM device may include a self-refresh exit routine to handle self-refresh aborts consistently.

When the signal from the memory controller is received, it is possible that a self refresh was ongoing within the DRAM. If self-refresh was ongoing, then in one embodiment the self-refresh is aborted on a row boundary. In other words, the rows that are currently being refreshed are finished, but the row address counter is not incremented, 340.

For example, if DRAM was in the middle of refreshing the second of four rows, then row address counter bits [B01:B00] are at (0,1) assuming counters are incremented at end of refresh. In this embodiment, the 3rd and 4th row are not refreshed and row address counter bits [B01:B00] are reset to (0,0). Row address counters bits [B14:B2] are at the same value as before the refresh command that was aborted. In other words, they are not incremented. In other embodiments, row address counter bits [B01:B00] are incremented to reflect the last specific row that was refreshed before the self-refresh mode was aborted.

Thus, it is understood that in embodiments of the invention, due to the possibility of several aborts, the rows of a DRAM device may not be refreshed via the DRAM device self-refresh mode. The memory controller may initiate an external refresh to keep the data in the cells valid.

FIG. 4 illustrates a DRAM refresh cycle according to an embodiment of the invention. This diagram shows a potential self-refresh cycle for four rows of a bank according to an embodiment of the invention.

In this embodiment, a refresh command will refresh rows 400-403. The time to complete this command is represented by tRFC 410, while the time to complete a refresh of each row is represented by tRC 420.

It is to be understood that the fast self-refresh exit time in embodiments of the invention is tRC 420 (plus a guard band) as opposed to tRFC 410 (plus a guard band). As illustrated in FIG. 4, tRC 420 is significantly shorter than tRFC 410. In this example, a 2 GBit DRAM devices a presumed, and thus tRC is 45 ns while tRFC is 160 ns. It is understood that the discrepancy between tRC and tRFC in high density DRAM devices is larger (e.g., tRFC for a 4 GBit device is in the range of 300 ns, while tRFC for an 8 Gbit device is in the range of 550 ns).

In one embodiment, a memory controller will at least periodically issue an extra DRAM device refresh command upon causing a DRAM device to exit the self-refresh mode. This ensures that all rows of a DRAM device are refreshed in the presence of a plurality of self-refresh mode aborts.

SRC=https://www.google.com.hk/patents/US20120079182

Fast exit from dram self-refresh的更多相关文章

- 深入解析内存原理:DRAM的基本原理

前面我们知道了在一个简单的SRAM 芯片中进行读写操作的步骤了,然后我们来了解一下普通的DRAM 芯片的工作情况.DRAM 相对于SRAM 来说更加复杂,因为在DRAM存储数据的过程中需要对于存储的信 ...

- S3C2440启动代码2440init.s彻底解析

可以选择nand启动和nor启动,这两者之间的关系通过一个按键来选择 这个OM0有何玄机,在数据手册中有这么一段 位宽RAM启动了(当然,还得设置一些东西,下面就说), Nanaflash启动经历的过 ...

- 将ADS1.2的工程迁移到KEIL上-基于2440

裸机程序应该是一个很好的选择 1. 不拷贝启动代码,因为我们用自己的启动代码 2. 建立工程目录分级,建立完成后如下所示 拷贝相应代码到对应目录中 Option中拷贝 Core中拷贝 建立 ...

- Static Random-Access Memory Dynamic Random-Access Memory

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION RAM technology is div ...

- USB电源管理

在USB总线接口协议中,由于涉及电源供电,因此协议中规定了完整的电源管理方案.通过USB电源管理可以实现USB设备的激活.挂起.空闲和睡眠等,从而降低无效的功率消耗,实现系统电源的有效使用和合理分配. ...

- 【技术贴】解决127.0.0.1和http://localhost均被拦截跳转到另一个网页

很艰难的历程. 今天安装一个OA系统,要用到http://127.0.0.1输入完成之后,可以进入安装界面,but,我输入完了之后,自动跳到了129129垃圾网站,艹,我真TM服了,我把本地连接网线都 ...

- [AS/400] 基本概念

本文内容源于 Go4AS400 在 AS/400 中,AS 代表着 Application System.AS/400 是一个安全性高的系统,可以限制用户只能访问.处理特定的信息.AS/400 整合了 ...

- [CSAPP笔记][第六章存储器层次结构]

第六章 存储器层次结构 在简单模型中,存储器系统是一个线性的字节数组,CPU能够在一个常数访问每个存储器位置. 虽然是一个行之有效的模型,但没有反应现代系统实际工作方式. 实际上,存储器系统(memo ...

- arm汇编:ldr,str,ldm,stm,伪指令ldr

ldr,str,ldm,stm的命名规律: 这几个指令命名看起来不易记住,现在找找规律. 指令 样本 效果 归纳名称解释 ldr Rd,addressing ldr r1,[r0] addressin ...

随机推荐

- Playing with coroutines and Qt

你好!我最近想知道C ++中的协程的状态,我发现了几个实现.我决定选择一个用于我的实验.它简单易用,适用于Linux和Windows. 我的目标是试图找到一种方法来让代码异步运行,而不必等待信号触发插 ...

- IQMath是什么 浮点转定点运算,dsp

[转帖注明出处:blog.csdn.net/lanmanck] 网上搜了一下没发现非常合适的,特写出来与大家分享. 大家都知道嵌入式系统里带浮点运算指令的CPU都比較少,TI的DSP也是定点的廉价. ...

- js课程 2-8 js内置对象有哪些

js课程 2-8 js内置对象有哪些 一.总结 一句话总结:JS中内置了17个对象,常用的是Array对象.Date对象.正则表达式对象.string对象.Global对象. 1.js常用对象有哪些? ...

- css 单行图片文字水平垂直居中汇总

(1) 水平居中 a. 行内元素水平居中 因为img是行内元素(行内块级元素也一样)父级元素设置text-align:center即可,例如: <div style="width: 6 ...

- 【81.82%】【codeforces 740B】Alyona and flowers

time limit per test2 seconds memory limit per test256 megabytes inputstandard input outputstandard o ...

- [Angular2 Animation] Delay and Ease Angular 2 Animations

By default, transitions will appear linearly over time, but proper animations have a bit more custom ...

- 搭建hbase-0.94.26集群环境 分类: B7_HBASE 2015-01-24 17:14 861人阅读 评论(0) 收藏

先安装hadoop1.2.1,见http://blog.csdn.net/jediael_lu/article/details/38926477 1.配置hbase-site.xml <prop ...

- js中数组如何使用

js中数组如何使用 一.总结 一句话总结:new Array()和[]两种方法都可以创建数组. 二.js中创建数组,并往数组里添加元素 数组的创建 var arrayObj = new Array() ...

- php面试题四

php面试题四 一.总结 二.php面试题四 01. 输出为 Mozilla/4.0(compatible;MSIE5.01;Window NT 5.0)时,可能的输出语句是: A.$_S ...

- TEMPDB

TEMPDB暴涨 阅读目录 前言 正文 原因 解决 补充 回到顶部 前言 tempdb暴增,造成磁盘空间不足,甚至影响业务运行. 回到顶部 正文 如图,tempdb log文件从7.4 ...