实现1sym转换成2个sym送给CVI(VGA数据)

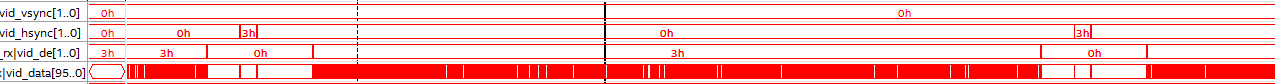

CVI的时序如下 :de指示数据有效。

从下面的程序看,同步码的长度不会影响对有效数据的判断。同步码的作用更多的是用于计算行及一行的像素数目。

方案一:

1 module vga_1sym_2_2sym(

input clk_i,

input rst_p,

input [:] data_i,

input h_sync_i,

input v_sync_i,

input de_i , output [:] data_o,

output [:] h_sync_o,

output [:] v_sync_o,

output [:] de_o,

output vga_clk_o ); wire ctrl_clk;

wire vga_clk;

wire vga_clk_dvi2;

clkctrl u0_clkctrl (

.inclk (clk_i), // altclkctrl_input.inclk

.outclk (ctrl_clk) // altclkctrl_output.outclk

);

iopll u0 (

.rst (rst_p), // reset.reset

.refclk (ctrl_clk), // refclk.clk

.locked (), // locked.export

.outclk_0 (vga_clk), // outclk0.clk

.outclk_1 (vga_clk_dvi2) // outclk0.clk

); reg [:] data_r;

reg [:] vga_data_dly2;

reg [:] vga_data_dly3;

reg h_sync_r = ;

reg v_sync_r = ;

reg de_r = ;

always @( posedge vga_clk )

begin

data_r <= data_i;

h_sync_r <= h_sync_i;

v_sync_r <= v_sync_i;

de_r <= de_i;

end

// reg [1:0] de_dly = 2'b00;

// always @( posedge vga_clk )

// begin

// de_dly[1:0] <= {de_dly[0],de_i};

// end

// wire pos_de = (de_dly[1:0] == 2'b01 );

reg h_l_cnt = 'b0;

always @( posedge vga_clk )

begin

// if( pos_de )

// h_l_cnt <= 1'b1;

// else

h_l_cnt <= ~h_l_cnt;

end

reg [:]data_r2 = ;

reg [:] h_sync_r2 = 'b00;

reg [:] v_sync_r2 = 'b00;

reg [:] de_r2 = 'b00;

always @( posedge vga_clk )

begin

if( h_l_cnt ) begin

data_r2[:] <= data_r;

h_sync_r2[] <= h_sync_r;

v_sync_r2[] <= v_sync_r;

de_r2[] <= de_r; end else begin data_r2[:] <= data_r;

h_sync_r2[] <= h_sync_r;

v_sync_r2[] <= v_sync_r;

de_r2[] <= de_r;

end

end

reg vga_cvi_valid = ;

always @( posedge vga_clk )

begin

if( ~h_l_cnt )

vga_cvi_valid <= 'b1;

else

vga_cvi_valid <= 'b0; end // assign data_o = data_r2;

// assign h_sync_o = h_sync_r2;

// assign v_sync_o = v_sync_r2;

// assign de_o = de_r2; wire rd_empty;

wire [:] fifo_dout;

reg [:] rd_empty_r = 'b00;

wire rd_en ;

fifo_w22 u0_fifo_w22 (

.data ({data_r2,h_sync_r2,v_sync_r2,de_r2}), // fifo_input.datain

.wrreq (vga_cvi_valid), // .wrreq

.rdreq (rd_en), // .rdreq

.wrclk (vga_clk), // .wrclk

.rdclk (vga_clk_dvi2), // .rdclk

.q (fifo_dout), // fifo_output.dataout

.rdempty (rd_empty), // .rdempty

.wrfull () // .wrfull

);

always @( posedge vga_clk_dvi2 )

begin

rd_empty_r <= {rd_empty_r[],rd_empty};

end

assign rd_en = ~rd_empty_r[];

assign {data_o,h_sync_o,v_sync_o,de_o} = fifo_dout;

assign vga_clk_o = vga_clk_dvi2;

endmodule

现在用一种更简单的方式即可实现,

方案二:

module vga_1sym_2_2sym(

input clk_i,

input rst_p,

input [:] data_i,

input h_sync_i,

input v_sync_i,

input de_i , output [:] data_o,

output [:] h_sync_o,

output [:] v_sync_o,

output [:] de_o,

output vga_clk_o,

output vga_valid_o );reg [:] data_r;

reg [:] vga_data_dly2;

reg [:] vga_data_dly3;

reg h_sync_r = ;

reg v_sync_r = ;

reg de_r = ;

always @( posedge vga_clk )

begin

data_r <= data_i;

h_sync_r <= h_sync_i;

v_sync_r <= v_sync_i;

de_r <= de_i;

end

// reg [1:0] de_dly = 2'b00;

// always @( posedge vga_clk )

// begin

// de_dly[1:0] <= {de_dly[0],de_i};

// end

// wire pos_de = (de_dly[1:0] == 2'b01 );

reg h_l_cnt = 'b0;

always @( posedge vga_clk )

begin

// if( pos_de )

// h_l_cnt <= 1'b1;

// else

h_l_cnt <= ~h_l_cnt;

end

reg [:]data_r2 = ;

reg [:] h_sync_r2 = 'b00;

reg [:] v_sync_r2 = 'b00;

reg [:] de_r2 = 'b00;

always @( posedge vga_clk )

begin

if( h_l_cnt ) begin

data_r2[:] <= data_r;

h_sync_r2[] <= h_sync_r;

v_sync_r2[] <= v_sync_r;

de_r2[] <= de_r; end else begin data_r2[:] <= data_r;

h_sync_r2[] <= h_sync_r;

v_sync_r2[] <= v_sync_r;

de_r2[] <= de_r;

end

end

reg vga_cvi_valid = ;

always @( posedge vga_clk )

begin

if( ~h_l_cnt )

vga_cvi_valid <= 'b1;

else

vga_cvi_valid <= 'b0; end assign data_o = data_r2 ;

assign h_sync_o = h_sync_r2 ;

assign v_sync_o = v_sync_r2 ;

assign de_o = de_r2 ;

assign vga_clk_o = vga_clk;

assign vga_valid_o = vga_cvi_valid;

end

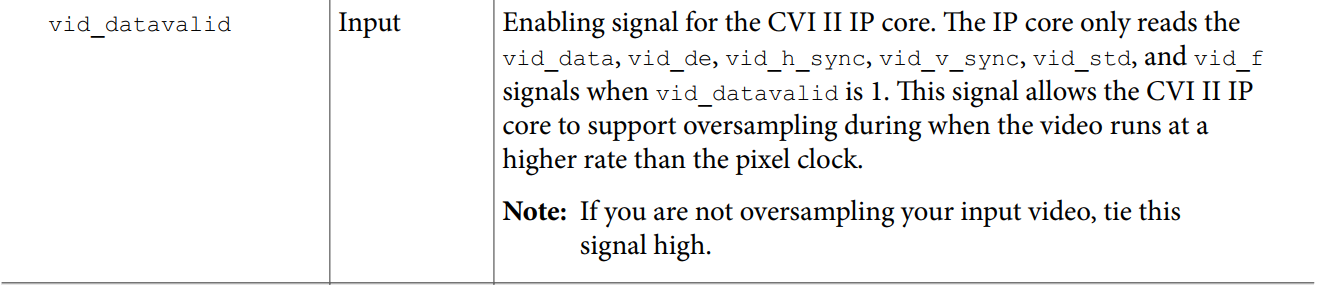

该实现过程与方案一相比,节省了PLL和FIFO,但输出了一个vga_valid_o信号,该信号连接到CVI的vid_datavalid信号。以下是vid_datavalid信号的定义:

意思是,CVI II IP核只在vid_datavalid为高电平时,才会读取vid信号,该信号用于CVI支持视频信号的过采样。也就是同一个像素对应多个时钟的情况下,只需要一个时钟的数据即可。

原本我的想法是让vid_datavalid始终保持高电平状态,通过vga_cvi_valid信号控制de_o翻转,间隔一个时钟数据有效一次(其实在实现时v_sync_o,h_sync_o都有翻转,目前觉得可能不翻转h,v信号也许可行),但是画面很不正常。de_o的作用是指示vid_data是有效数据。

方案三:

尝试上面提到的h,v不翻转。保持vid_datavalid始终为高电平。

经过验证,可能不行。

实现1sym转换成2个sym送给CVI(VGA数据)的更多相关文章

- 将list<对象>转换成DataTable,把DataTable转换成参数传入存储过程实现批量插入数据

领导让在存储过程中批量添加数据,找出效率最高的,我看到后台代码后,发现可以将list<对象>转换成DataTable,把DataTable转换成参数传入存储过程实现批量插入数据,知道还有其 ...

- GUID转换成16位字符串或19位数据(确保唯一)

// <summary> /// 根据GUID获取16位的唯一字符串 /// </summary> /// <param name=\"guid\"& ...

- C#将DataTable转换成list的方法

本文实例讲述了C#将DataTable转换成list及数据分页的方法.分享给大家供大家参考.具体如下: /// <summary> /// 酒店评论列表-分页 /// </su ...

- list<?>转换成 对应的 class

项目中用到的,list转换成bean.因为查询出来的数据用list 泛型接收,要返回 实体对象.所以需要对应转换. 主要用到的技术:反射. 上代码: public static <T> L ...

- Linux下ffmpeg添加Facebook/transform代码块实现将全景视频的球模型转换成立方体模型

Facebook事实上已开始在平台中支持360度全景视频的流播,但公司对此并不满足.其工程师更是基于锥体几何学设计出了一套全新的视频编码,号称最高能将全景视频的文件大小减少80%.(VR最新突破:全景 ...

- DataTable 转换成 Json的3种方法

在web开发中,我们可能会有这样的需求,为了便于前台的JS的处理,我们需要将查询出的数据源格式比如:List<T>.DataTable转换为Json格式.特别在使用Extjs框架的时候,A ...

- 微信小程序中利用时间选择器和js无计算实现定时器(将字符串或秒数转换成倒计时)

转载注明出处 改成了一个单独的js文件,并修改代码增加了通用性,点击这里查看 今天写小程序,有一个需求就是用户选择时间,然后我这边就要开始倒计时. 因为小程序的限制,所以直接选用时间选择器作为选择定时 ...

- C#将Word转换成PDF方法总结(基于Office和WPS两种方案)

有时候,我们需要在线上预览word文档,当然我们可以用NPOI抽出Word中的文字和表格,然后显示到网页上面,但是这样会丢失掉Word中原有的格式和图片.一个比较好的办法就是将word转换成pdf,然 ...

- DataTable转换成IList<T>的简单实现

DataTable的无奈 很多时候,我们需要去操作DataTable.但DataTable的操作,实在是太不方便了.Linq?lambda表达式?统统没有... 特别是对现有结果集做进一步筛选,这样的 ...

随机推荐

- java爬取网页Unicode转UTF-8中文

unicode编码简而言之就是将每一个字符用16位2进制数标识.但是通常都用4位的16进制数标识. 例如: 1)中文字符串"你好"的unicode码为:\u60\u597d; 2) ...

- win10下安装配置mysql-8.0.13

1.下载mysql-8.0.13安装包 https://dev.mysql.com/downloads/mysql/ 选择zip安装包下载就好. 2.解压到你要安装的目录 3.创建my.ini配置文件 ...

- rbac 权限分配, 基于formset实现,批量增加

这里需要两个知识点: - formset - 自动发现项目中的URL1. 什么是formset: Django中 form组件 或 ModelForm组件,用于做一个表单的验证. 接收前端form表单 ...

- 学习knockoutjs轻量级的MVVM框架

教程:knockoutjs介绍 http://www.w3cfuns.com/forum.php?mod=viewthread&tid=5598714 MVVM架构~knockoutjs实现简 ...

- Oracle_高级功能(2) 索引

1.oracle优化器 优化目标分为4种: choose (选择性) rule (基于规则) first rows(第一行) all rows(所有行) Description:描述sql的执行计划 ...

- 利用Swoole编写一个TCP服务器,顺带测试下Swoole的4层生命周期

1首先我们写一个入口脚本,这里简单点的功能就是开启服务和关闭服务 <?php //CLI命令 if(isset($argv[1]) && in_array($argv[1], [ ...

- iOS.Debug.Simulator

1. iOS Simulator Tips & Tricks http://code.tutsplus.com/tutorials/ios-simulator-tips-tricks--mob ...

- java1.8 版本改成 java1.7版本

以前先安装的java1.7 大部分程序应该都是只支持1.7 不支持1.8 但是因为要跑一个别人的项目 要求是java1.8 所以想在电脑上同时装1.7和1.8 到官网上下载1.8 安装 安装完成后 并 ...

- tyvj 创世纪 - 基环树

codevs : 传送门 Description 上帝手中有着N 种被称作“世界元素”的东西,现在他要把它们中的一部分投放到一个新的空间中去以建造世界. 每种世界元素都可以限制另外一种世界元素,所 ...

- Codeforces 798C. Mike and gcd problem 模拟构造 数组gcd大于1

C. Mike and gcd problem time limit per test: 2 seconds memory limit per test: 256 megabytes input: s ...