计数器IP核

Quartus II提供的LPM_couter IP核的使用

FPGA设计方式:

原理图,Verilog HDL设计方式,IP核输入方式

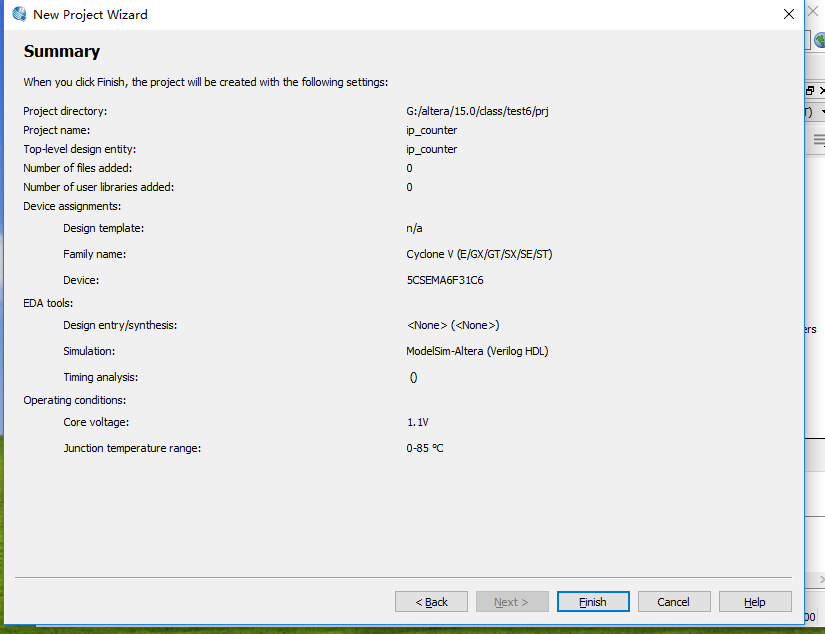

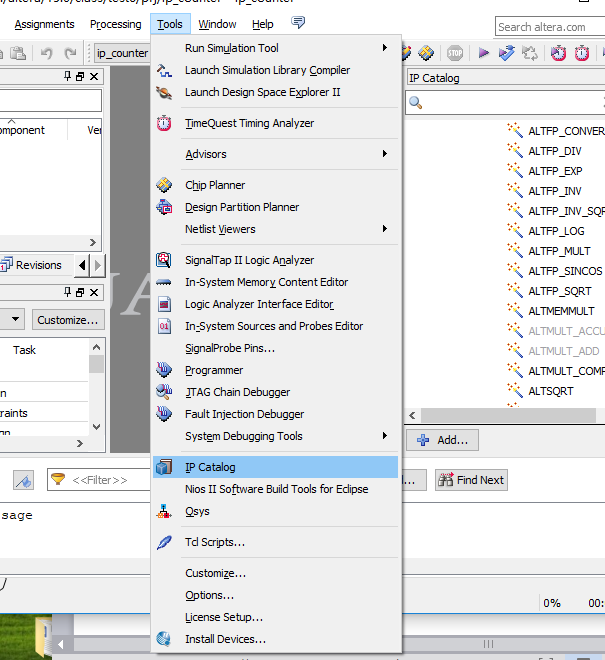

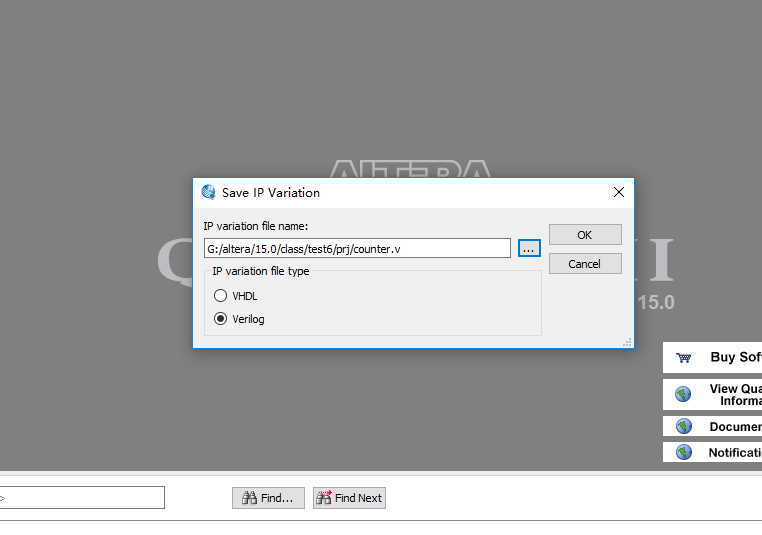

创建IP核

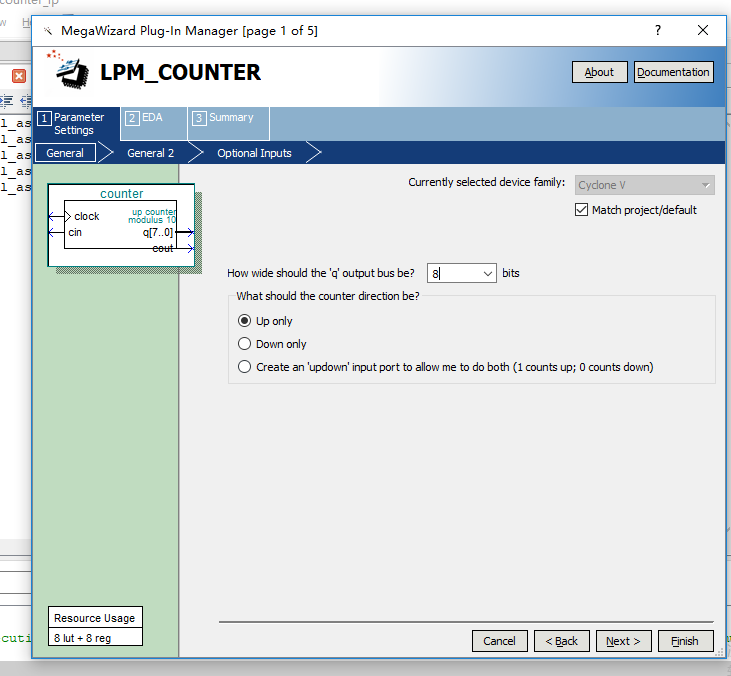

点击TOOLS—IP catalog-libray-Arithmetic-LPM_COUNTER

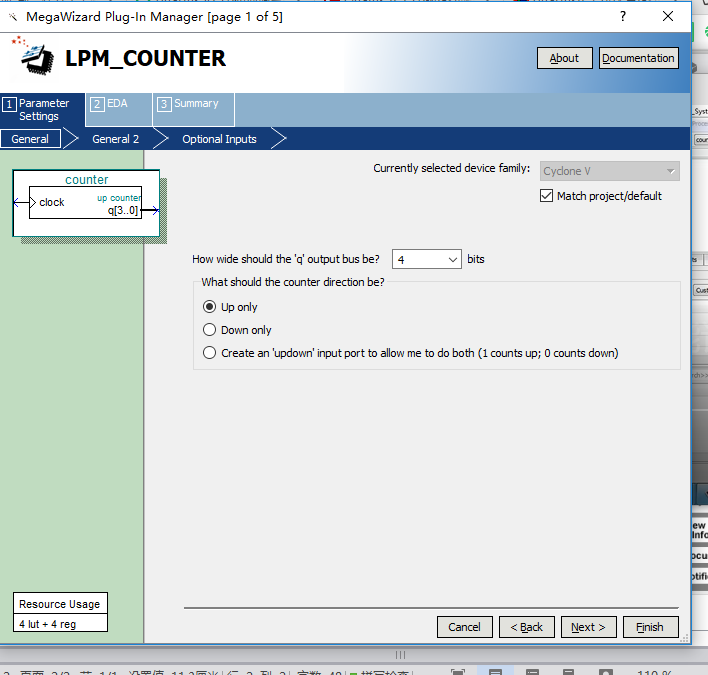

选择希望输出的寄存器是多少位的,计数类型。

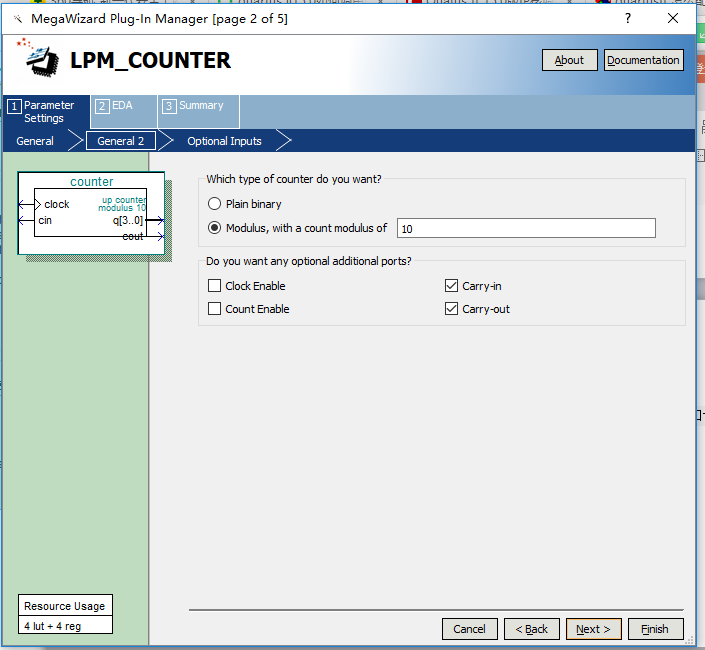

选择计数器类型(直接计数还是以模的形式计数),是否需要时钟使能和计数使能信号、进位链的输入和进位链的输出。

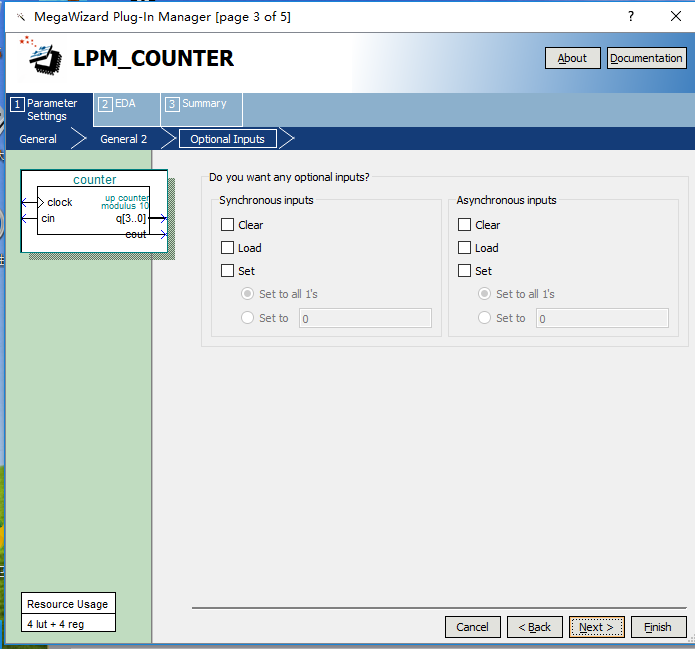

清零加载等信号

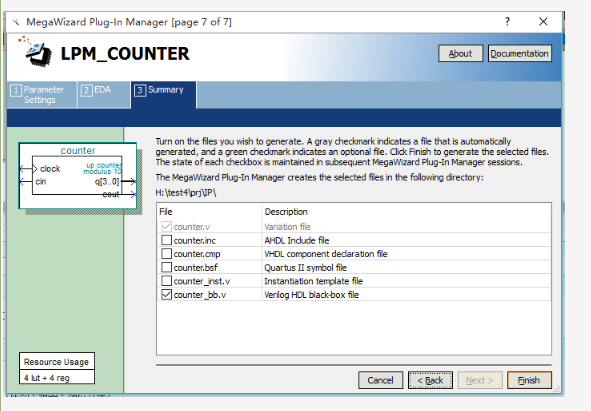

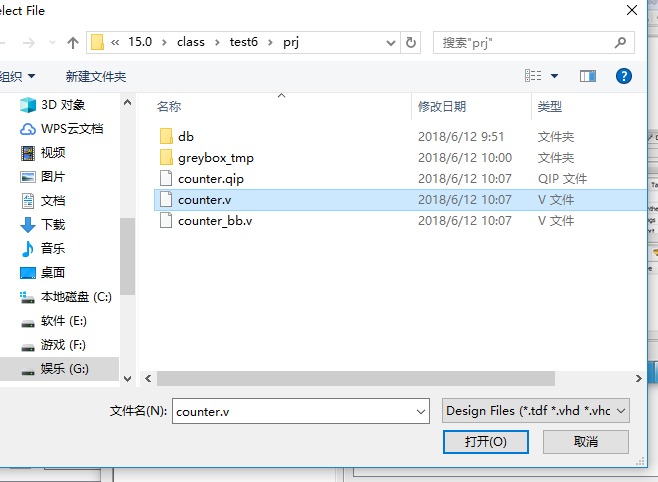

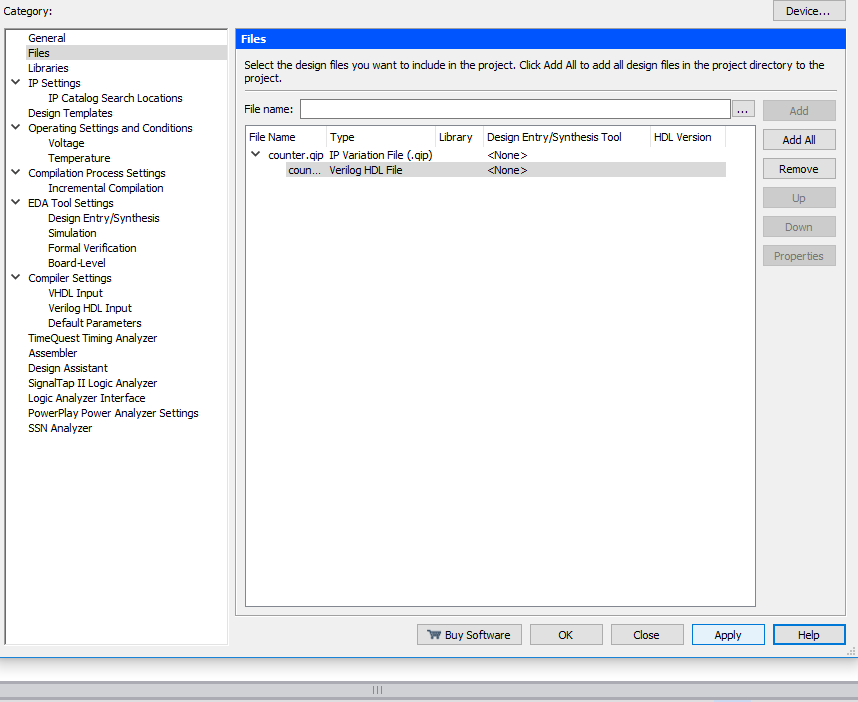

创建成功后的IP核的文件信息

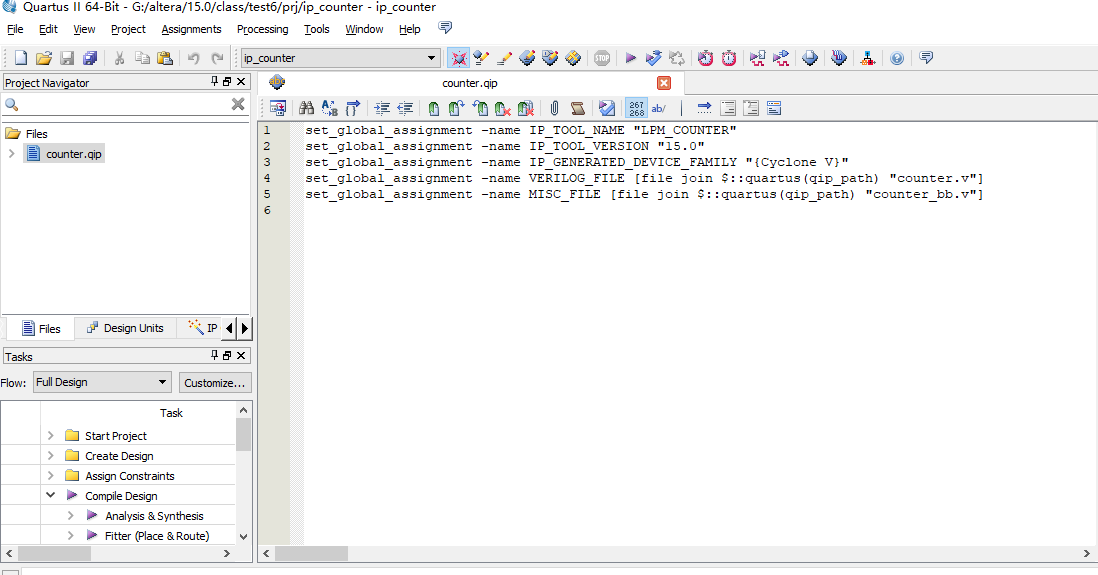

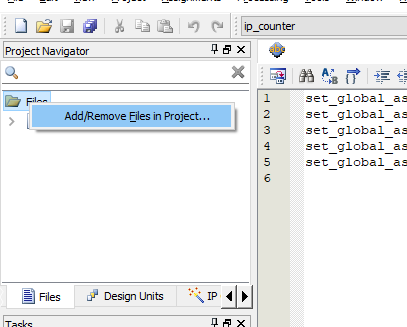

将counter.v文件加载到顶层文件中

Ip核已经做好了功能,直接利用就可以;

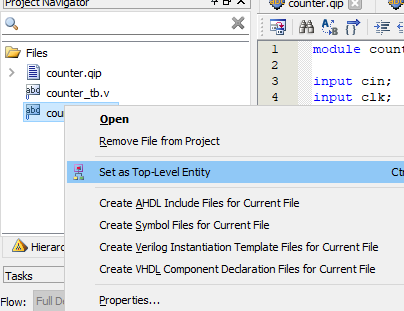

把counter_ip设置为顶层文件后进行编译。

编写testbench文件进行测试IP核功能

`timescale 1ns/1ns

`define clock_period

module counter_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [:] q;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout),

.q(q)

);

initial clk = ;

always #(`clock_period/)clk = ~clk;

initial begin

repeat()begin

cin = ;

#(`clock_period*)cin = ;

#(`clock_period)cin = ;

end

#(`clock_period*);

$stop;

end

endmodule

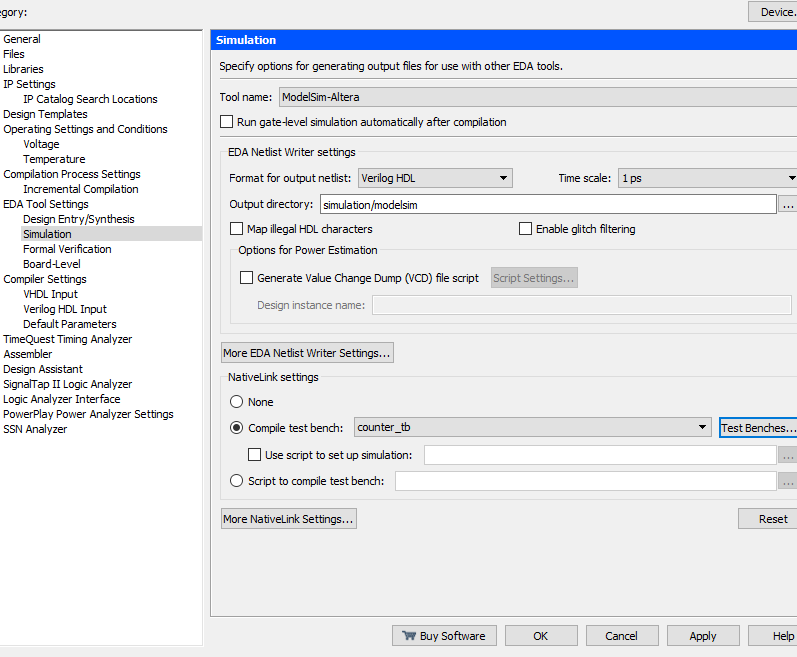

设置仿真

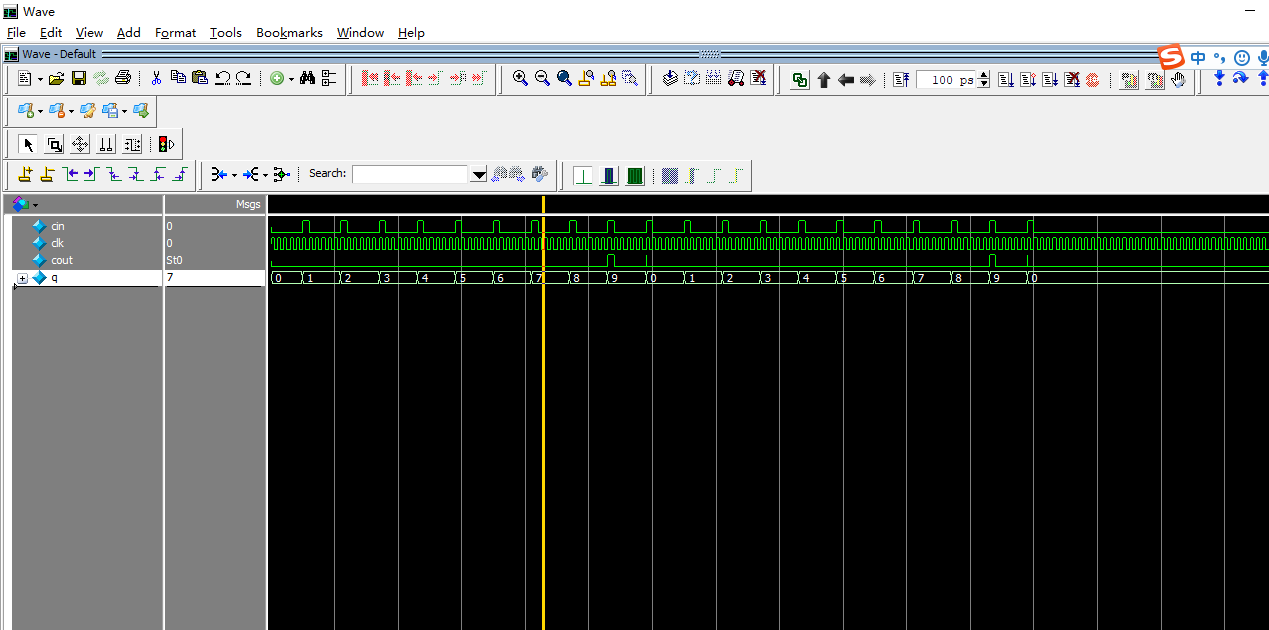

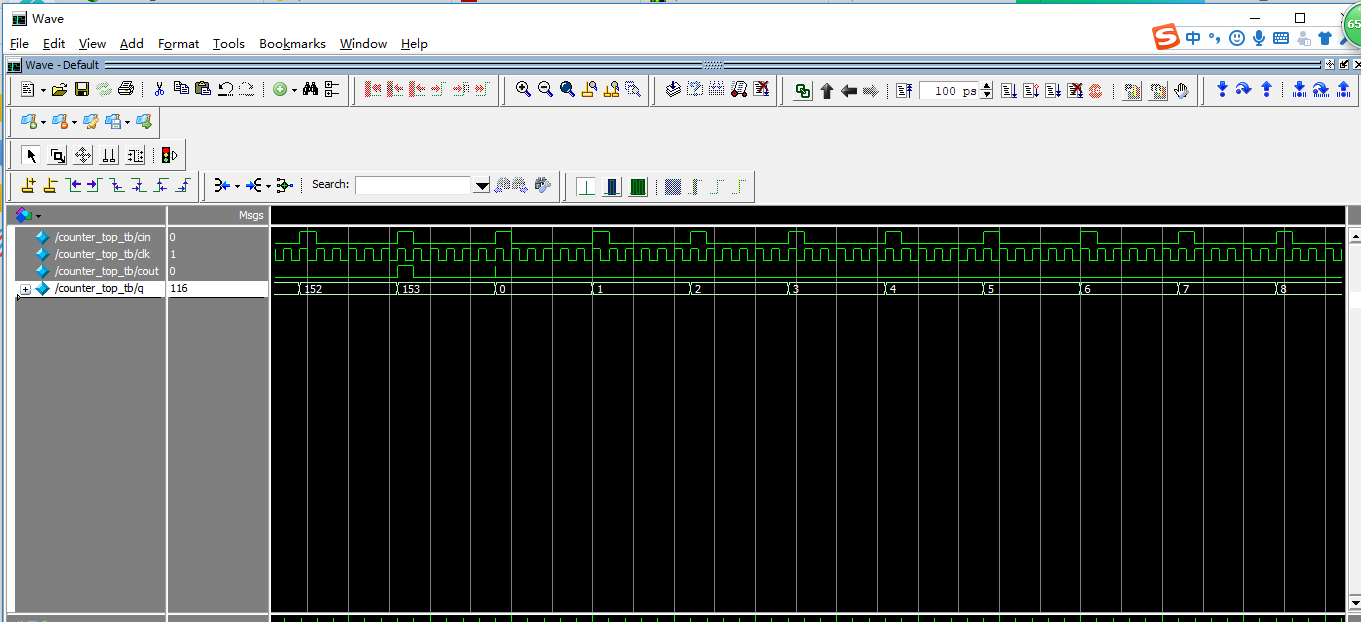

运行 仿真,可以看到每隔5个clk有一个cin信号,计数器完成一次计数,到计数到设定的模值10时会产生一次c_out信号,然后计数器重新开始从0开始计数,与设计的期望。

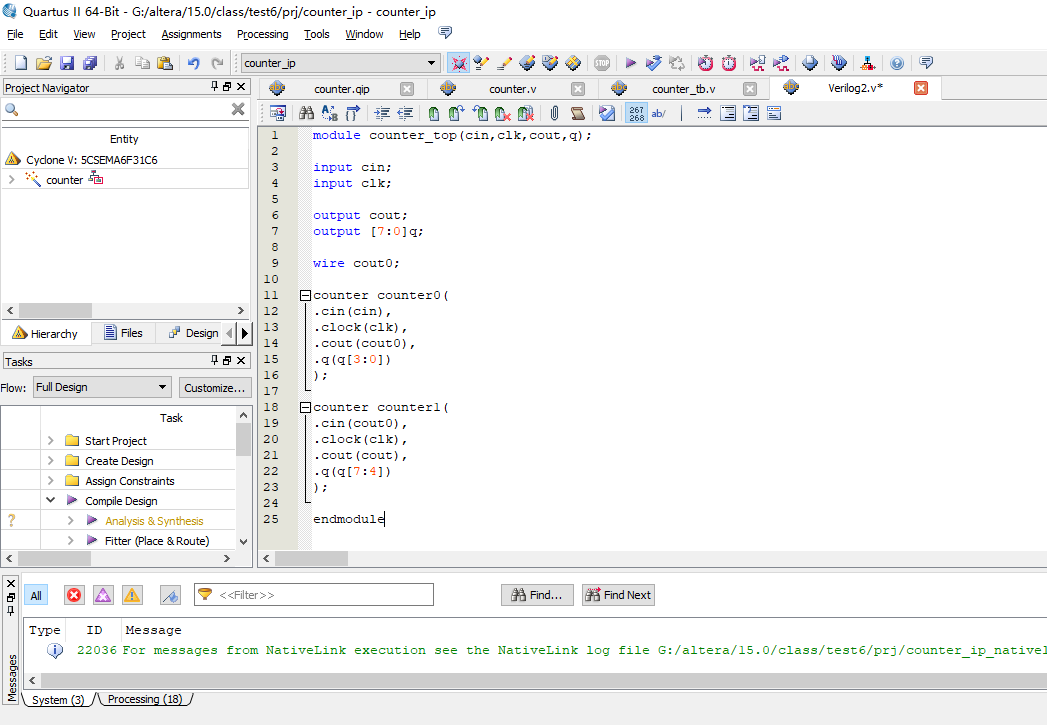

若要将计数器改为8位计数器:

(1)可以将 ip核改为8位

(2)也可以进行级联

新建Verilog文件进行编程如下。

这里的原理是将前一级的c_out作为下一级计数的c_in,此时即将两个计数器级连起来了,这样就将一个四位的计数器转换成了一个八位的计数器。

将这个文件设置为顶层文件。

module counter_top(cin,clk,cout,q); input cin;

input clk; output cout;

output [:]q; wire cout0; counter counter0(

.cin(cin),

.clock(clk),

.cout(cout0),

.q(q[:])

); counter counter1(

.cin(cout0),

.clock(clk),

.cout(cout),

.q(q[:])

); endmodule

编写testbench如下

`timescale 1ns/1ns

`define clock_period

module counter_top_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [:] q;

counter_top counter0(

.cin(cin),

.clk(clk),

.cout(cout),

.q(q)

);

initial clk = ;

always #(`clock_period/)clk = ~clk;

initial begin

repeat()begin

cin = ;

#(`clock_period*)cin = ;

#(`clock_period)cin = ;

end

#(`clock_period*);

$stop;

end endmodule

计数器IP核的更多相关文章

- 利用IP核设计高性能的计数器

利用Quartus II的LPM_counter IP核进行设计(利用IP核设计可以迅速高效的完成产品的设计) 新建工程 调用IP核 创建一个新的IP核 选择LMP_COUNTER,语言类型,输出路径 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- IP核引发的关于定,浮点数的认识

上面是一段关于CORDIC_IP测试文件,用于计算给定角度的sin值和cos值,关于数值表示规则在此不再重复,仅仅说明以下3点: 1 数采用原码,反码,补码,本身并没有正确与否之分(这一点很重要,我 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- 第7讲 SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

随机推荐

- selenium规避网站监测

规避网站监测 现在不少大网站有对selenium采取了监测机制.比如正常情况下我们用浏览器访问淘宝等网站的window.navigator.webdriver的值为undefined.而使用sel ...

- adb -- cannot connect to x.x.x.x:5555“由于目标计算机积极拒绝,无法连接”

原因 安卓系统未打开adb网络调试功能 通过USB方式连接到安卓系统设置即可 解决 先通过USB线连接 adb devices 能看到所连接的设备情况下 adb root 权限提权 adb shell ...

- 新建Microsoft Word文档

问题描述 L正在出题,新建了一个word文档,想不好取什么名字,身旁一人惊问:“你出的题目叫<新建Microsoft Word文档>吗?”,L大喜,一拍桌子,说:“好,就叫这个名字了.” ...

- gulp常用插件之gulp-uglify使用

更多gulp常用插件使用请访问:gulp常用插件汇总 gulp-uglify这是一款使用UglifyJS缩小js文件. 更多使用文档请点击访问gulp-uglify工具官网. 安装 一键安装不多解释 ...

- C++ STL:next_permutation和prev_permutation

两个函数都在#include <algorithm>里 顾名思义,next_permutation用来求下一个排列,prev_permutation用来求上一个排列. 当前的排列不满足函数 ...

- LeetCode 112. 路径总和 (递归遍历二叉树)

题目链接:https://leetcode-cn.com/problems/path-sum/ 给定一个二叉树和一个目标和,判断该树中是否存在根节点到叶子节点的路径,这条路径上所有节点值相加等于目标和 ...

- 用 ArcMap 发布 ArcGIS Server Feature Server Feature Access 服务

1. 安装Desktop, 2. 安装ArcGIS Server 3. 安装PostgreSQL 9.5 从 C:\Program Files (x86)\ArcGIS\Desktop10.5\Dat ...

- Python之路Day11

函数名的第一类对象及使用 当作值,赋值给变量 def func(): print(1) print(func) #查看函数的内存地址 a=func print(a) a() 可以当作容器中的元素 de ...

- 【转载】JS导出CSV文件

转自:http://www.cnblogs.com/dengnan/p/3990211.html 通过自己实际测试有以下几种方法 方法一通过a标签实现,把要导出的数据用“\n”和“,”拼接成一个字符串 ...

- 重载(Overload)和重写(Override)的区别是什么?

首先java程序的运行分为编译和运行两部分. 所以重载和重写在这一点就有很明显的区别,因为重写方法的方法名和参数个数类型都一样,所以在java虚拟机的编译阶段是识别不出重写的方法的不同,在运行期间才可 ...