FPGA中亚稳态相关问题及跨时钟域处理

前言

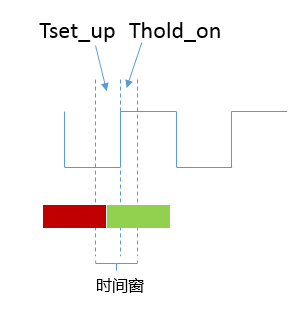

触发器输入端口的数据在时间窗口内发生变化,会导致时序违例。触发器的输出在一段时间内徘徊在一个中间电平,既不是0也不是1。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

触发器由于物理工艺原因,数据并不是理想化的只要触发沿时刻不变即可。触发器有固定的建立时间,保持时间。

建立时间:在时钟有效沿到来前数据需要稳定的时间。

保持时间:在时钟有效沿之后数据还需要保持不变的时间。

后果:会给设计带来致命的功能故障。

一般来说,信号是在异步信号,跨时钟域,复位电路中产生亚稳态。

解决方式:

1.单比特信号:

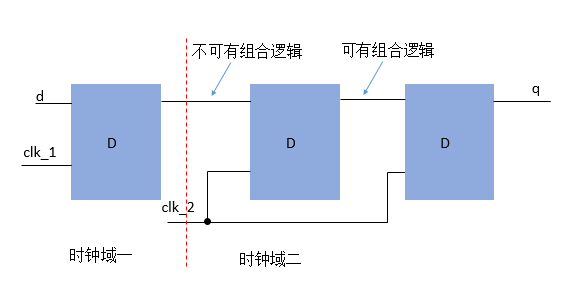

①采用同步器同步,低速设计打两拍,高速设计可能需要打三拍。

低速到高速时钟域,低速信号一般能被高速时钟域采到甚至多次。但高速时钟域到低速时钟域就不太好办了:

②闭环解决方案:采用握手反馈信号,这会导致延时开销大。

③开环解决方案:把信号展宽,至少为采样T的1.5倍。这样至少能采到一次。

2.多比特信号:

传递多比特信号,普通同步器就没啥卵用了,因为多比特信号偶发数据变化歪斜,导致采到的不一定是正确数据。

①多比特信号融合:把多比特信号转换为单比特信号,再用同步器同步。

②多周期路径规划:数据不需要同步,至需要同时传递一个同步的使能信号到接收时钟域即可,使能信号没被同步到接收时钟域并被识别之前数据不被采集。即在信号某个沿产生同步脉冲指示信号。

③异步fifo。

以上。

FPGA中亚稳态相关问题及跨时钟域处理的更多相关文章

- FPGA跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- 异步FIFO跨时钟域亚稳态如何解决?

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO的读写时钟域不同,是异步的,要是将读时钟域的读指针与写时钟域 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA中亚稳态——让你无处可逃

1. 应用背景 1.1 亚稳态发生原因 在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery ti ...

- 基于FPGA的跨时钟域信号处理——专用握手信号

在逻辑设计领域,只涉及单个时钟域的设计并不多.尤其对于一些复杂的应用,FPGA往往需要和多个时钟域的信号进行通信.异步时钟域所涉及的两个时钟之间可能存在相位差,也可能没有任何频率关系,即通常所说的不同 ...

- cdc跨时钟域处理-结绳握手法

参考文档 https://blog.csdn.net/u011412586/article/details/10009761 前言 对于信号需要跨时钟域处理而言,最重要的就是确保数据能稳定的传送到采样 ...

- 跨时钟域设计【一】——Slow to fast clock domain

跨时钟域设计是FPGA设计中经常遇到的问题,特别是对Trigger信号进行同步设计,往往需要把慢时钟域的Trigger信号同步到快时钟域下,下面是我工作中用到的慢时钟域到快时钟域的Verilog HD ...

- 跨时钟域设计【二】——Fast to slow clock domain

跨时钟域设计中,对快时钟域的Trigger信号同步到慢时钟域,可以采用上面的电路实现,Verilog HDL设计如下: // Trigger signal sync, Fast clock dom ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

随机推荐

- sql存储过程中使用 output、nvarchar(max)

1.sql存储过程中使用 output CREATE PROCEDURE [dbo].[P_Max] @a int, -- 输入 @b int, -- 输入 @Returnc int output - ...

- 翻转一个数组(c++实现)

反转一个数组: 其实STL中的vector有一个reverse函数便可以使用. #include<iostream> using namespace std; int* ReverseAr ...

- Redis服务端的搭建(初级)

前方低能,仅适合入门级菜鸟阅读,大神大牛通通闪开! 前言:redis经常被用来做缓存(原因自行科普),基于学习的需要自己搭建了一个redis服务器,考虑到项目的分布式部署,所以前期开始的时候,redi ...

- Python_函数的有用信息、带参数的装饰器、多个装饰器装饰一个函数

函数的有用信息 代码1: def login(username, password): """ 此函数需要用户名,密码两个参数,完成的是登录的功能. :return: T ...

- LZO

LZO 是致力于解压速度的一种数据压缩算法,LZO 是 Lempel-Ziv-Oberhumer 的缩写.这个算法是无损算法,参考实现程序是线程安全的. 实现它的一个自由软件工具是lzop.最初的库是 ...

- 【学习总结】C-翁恺老师-入门-第0周<程序设计与C>

[学习总结]C-翁恺老师-入门-总 1-首先按视频说的下载编辑器 <DevC++> 并一路默认设置: 安装包下载链接 (我有vc6.0不过预感告诉我老师要用类似CS50里那种命令行编辑器? ...

- Migrate MySQL database using dump and restore

kaorimatz/mysqldump-loader: Load a MySQL dump file using LOAD DATA INFILEhttps://github.com/kaorimat ...

- python 3.6.1 安装scrapy踩坑之旅

系统环境:win10 64位系统安装 python基础环境配置不做过多的介绍 window环境安装scrapy需要依赖pywin32,下载对应python版本的exe文件执行安装,下载的pywin32 ...

- java不同的包下相同的类名的问题与解决办法

Java中的类以包进行分类组织,当程序中需要用到某个包下的类时,可以以该类的全限定名进行引用.这样,不同的包中的类就可以同名,不会产生混淆. 但是这样就可能导致引用的时候会产生一些问题. 第一个问题, ...

- [转帖]国产闪存颗粒终于熬出头 紫光存储S100固态硬盘评测

国产闪存颗粒终于熬出头 紫光存储S100固态硬盘评测 https://www.cnbeta.com/articles/tech/830875.htm 全国产的 SSD 群联貌似是对岸的 不过不管怎么说 ...