强大的Vivado IP工具——自定义IP的使用

首先,要指出,本文不描述任何IP的功能与使用。

在开发一个大型FPGA项目时,多人协作是必不可少的。这个时候,如何提交设计给负责集成的人,是项目开发中最关键的问题之一。

常用的一个方法是,提交网表。网表的提交可以算是相当方便的操作了,这在ISE的时期还体会不到,但到了Vivado中,正如amazing icecream在博文http://blog.chinaaet.com/detail/37153中描述的,dcp的引入,让网表这一非常好用的功能发挥了其应有的作用。对于部分设计,直接使用dcp提交设计,已经足够。

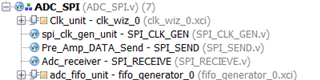

但正如amazing icecream在博文http://blog.chinaaet.com/detail/37165中描述的,dcp不支持嵌套这一问题,成为Vivado在工程化管理中最严重的问题之一。比如,如果遇到如下的设计

设计中包含了两个IP的xci。如果IP使用的OOC模式,则和dcp模块一样,都使用网表提交给顶层ADC_SPI。如果再将ADC_SPI模块打包成dcp,就会出现dcp文件的嵌套。调用ADC_SPI这个dcp网表时,会出现错误,无法读取其中的dcp模块的信息。

这就意味着,使用dcp的模块,只能是纯代码的模块,无法使用任何IP,哪怕是FIFO、BRAM之类的简单IP。另外,dcp也无法多次提交,所有开发者只能提交一次dcp网表,而无法层级提交dcp网表。

所以,本文介绍一下IP Packager这个工具,来解决上述的工程问题。目前的IP Packager仍然不支持包含dcp网表,但是生成子dcp网表的工程也可以封装为IP,所以可以用IP的方法来层级嵌套。

IP Packager,用来将自己的设计打包,封装成IP。然后在IP Catalog中导入后就可以与Xilinx提供的IP一起使用。其操作相对简单,难度低,可操作性很强。该工具为Vivado独有,ISE似乎没有类似的工具可以使用。

如何使用呢?首先,准备一个设计,由于IP Packager在封装IP时并不会检查设计是否有问题,比如是否有源文件确实等,需要开发者自己确认设计是否完整。

然后在菜单栏中选择“Tool”->“Create and Package IP…”,如下图所示。

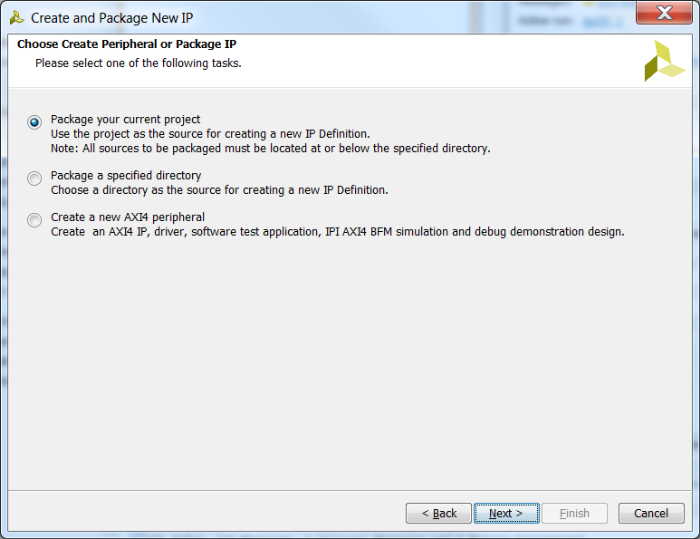

弹出如下界面,有兴趣可以自行阅读说明或参考相关文档,点击Next

在下一个界面中,选择第一项,然后点击Next。这里说明一下,第一项是将工程封装成IP,第二是将某个目录下的源文件封装成IP,第三项是封装AXI4的外设,有兴趣可以自行阅读说明文字或查询文档。

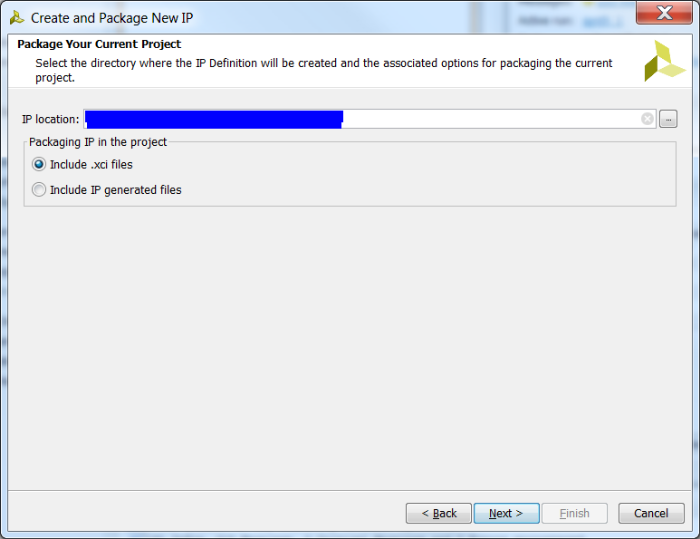

下一界面选择IP的路径,用于日后导入IP文件,同时选择仅包括xci文件还是包括所有IP已经生成的网表。这里选择“Include .xci files”

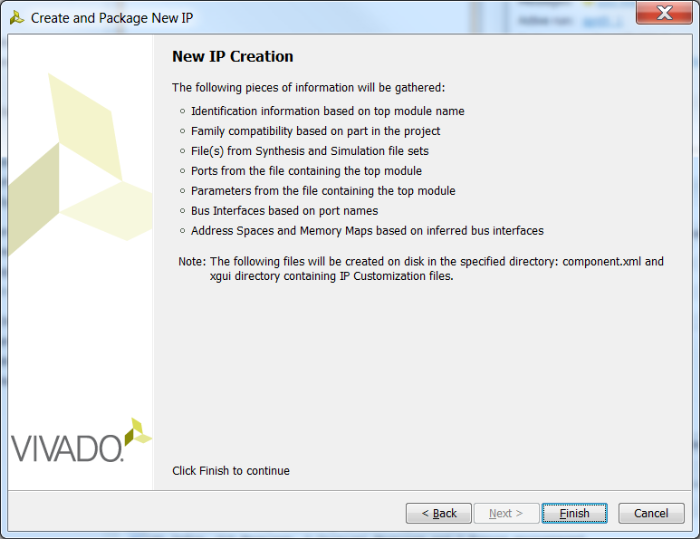

最后一页点击Finish即可

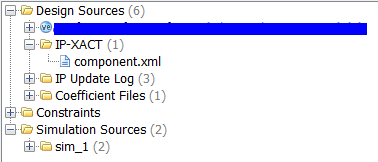

设置完成之后,可以发现在Project Manager窗口下的Hierarchy标签中,会多一个IP-XACT,下面会有一个component.xml,其中保存着封装IP的信息。

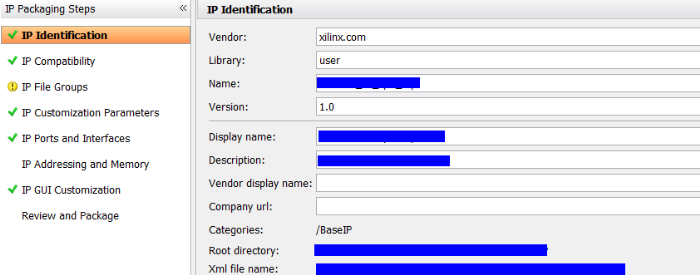

在Package IP的主界面里,列出了IP的定制化选项

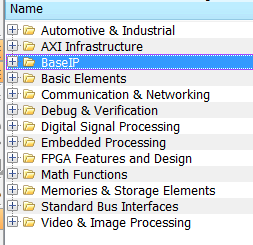

在第一项中,可以设置IP的信息,其中Categories是导入后IP存放的位置,默认为BaseIP,及IP Catalog导入后,可以再BaseIP中找个该IP

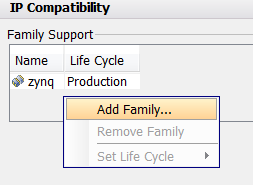

需要注意的是第二项“IP Compatibility”,点开后如下图所示。

从图中可以看到,此IP在封装时是兼容Zynq系列的,但是不兼容其他系列,为了让其支持其他系列的FPGA,可以右键弹出菜单,点击“Add Family”。

在弹出的“Choose Family Support”中选择希望添加的FPGA。

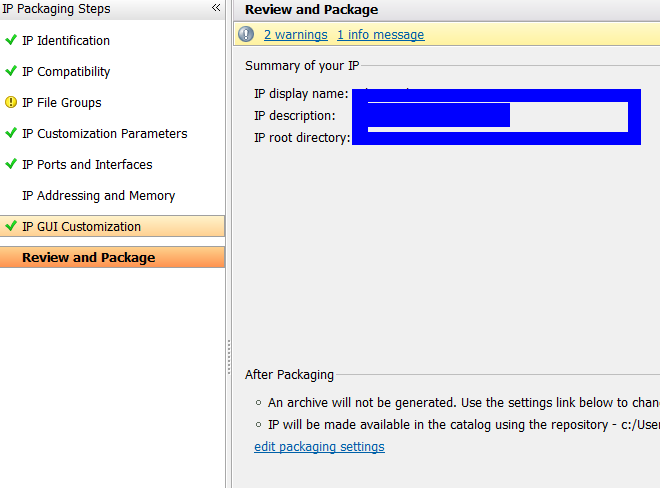

在最后一步“Review and Package”中,点击下方的edit packaging settings, 可以打开设置界面。

在蓝色框中,勾选“Create archive IP”即可生成zip压缩文件,用来保存IP信息,便于存档及使用。点击OK后回到Vivado主界面,然后点击Re-package IP即可刷新输出文件。

此时, IP封装的工作已经全部完成。

IP封装好以后,下一步就是如何调用该IP。首先打开IP Catalog。无论是单独建一个管理IP的工程,还是在Project Manager中点击IP Catalog,都可以。

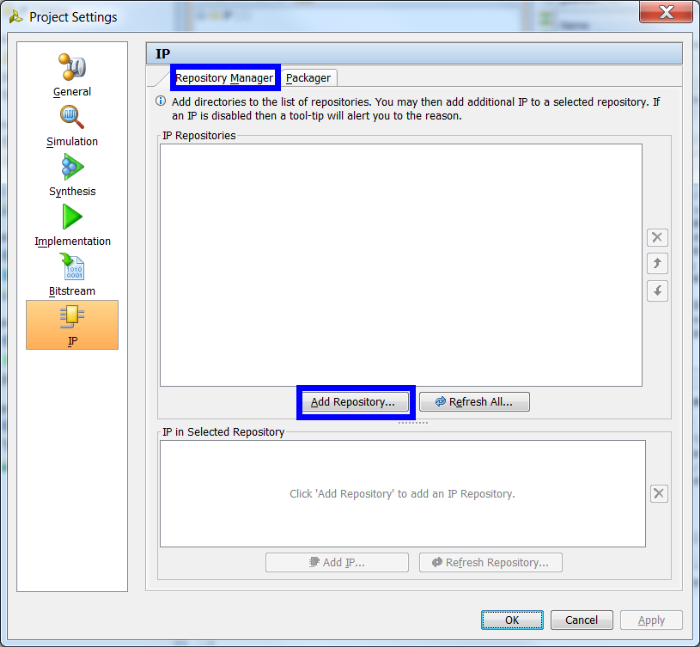

进入IP Settings,界面如下图所示

在“Repository Manager”标签中,点击“Add Repository…,如上图蓝框所示。

添加好刚才进行IP封装的路径后,即可自动识别出IP

点击OK返回IP Catalog主界面,即可在IP Catalog中找到相关IP。注意,只有IP兼容FPGA芯片时,该IP才会显示在IP Catalog中。比如IP封装式选择的是V7,主工程是K7,则无法使用;但是IP封装中添加兼容K7后,主工程是K7时就可以在IP Catalog中找到该IP

IP Packager的问题是,代码无法加密,不具有类似dcp的不可读功能。

考虑到Vivado目前仍然比较新,不排除在今后的版本中添加IP Packager的加密功能和dcp的嵌套功能。

如有兴趣,赶快去定制自己的IP Core吧。

转载:http://blog.chinaaet.com/ad604/p/37169

强大的Vivado IP工具——自定义IP的使用的更多相关文章

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- [转帖]vivado & VS2013工具

来源:http://bbs.csdn.net/topics/380057699 添加OpenCV库后,MFC在Debug模式下调试,提示应用程序无法正常启动(0xc000007b). 解决方法:在环境 ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- 第三章 VIVADO 自定义IP 流水灯实验

第二章里面已经说过了,MIZ701 PL部分没有输入时钟,因此驱动PL资源必须是通过PS来提供时钟,所以这个流水灯实验也得建立一个最小系统了,然后再添加一个流水灯的自定义IP. 3.0本章难度系数★★ ...

- AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构.我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序 ...

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断.PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势. 一.PL 侧定时 ...

随机推荐

- enum don't allocate any memory

int main() { _asm{ mov edi,edi mov edi,edi } ,Green,Yellow}; _asm{ mov edi,edi mov edi,edi } Color c ...

- U-Boot添加menu命令的方法及U-Boot命令执行过程

转;http://chenxing777414.blog.163.com/blog/static/186567350201141791224740/ 下面以添加menu命令(启动菜单)为例讲解U-Bo ...

- quartz做集群配置较短的时间间隔会重复执行任务的问题

quartz.properties org.quartz.jobStore.misfireThreshold = 60000 这个参数(单位为毫秒)设置了以后就是超时1min的就不执行,小于1min会 ...

- 【redis】在spring boot2.0中使用redis的StringRedisTemplate 自动注入@Autowired

1.使用opv.increment 达到增量的效果[判断某个用户 是第几次做这种操作] @RequestMapping("createCode") @RestController ...

- JS中for和forEach的区别

https://thejsguy.com/2016/07/30/javascript-for-loop-vs-array-foreach.html

- 实现同时提交多个form(基础方法) 收集

实现同时提交多个form(基础方法) 收集 分类: 1.2-JSP 1.3-J2EE 1.1J2se 1.0-Java相关2011-12-01 20:59 1644人阅读 评论(0) 收藏 举报 bu ...

- git命令01

1.了解git工具产生的背景知识.git 是什么? 目前它是一种分布式版本控制系统.那什么又是版本控制系统? 一种能自动帮助记录每次文件的改动,不仅仅是记录自己对文件的修 改变化,而且可以记录其他人对 ...

- axios 同时执行多个请求

http://chuansong.me/n/394228451820 同时执行多个请求 axios.all([ axios.get('https://api.github.com/xxx/1'), a ...

- 前端性能优化:使用Array.prototype.join代替字符串连接

来源:GBin1.com 有一种非常简单的客户端优化方式,就是用Array.prototype.join代替原有的基本的字符连接的写法.在这个系列的第一篇中,我在代码中使用了基本字符连接: htmlS ...

- java中异常介绍

一.异常概述 异常处理已经成为衡量一门语言是否成熟的标准之一,目前的主流编程语言如C++.C#.Ruby.Python等,大都提供了异常处理机制.增加了异常处理机制后的程序有更好的容错性,更加健壮. ...