《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案

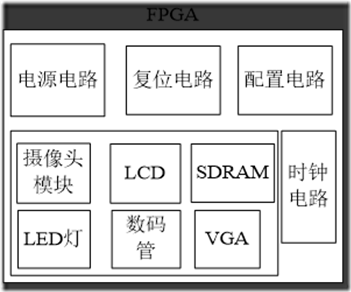

对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况。图2.6是笔者曾经设计的硬件平台系统。

图2.6系统框图

对于选定一个系统方案之后,接下来做的要先去查看所选用的芯片的数据手册。那么查看手册一般有几点必须要注意,(1)FPGA的工作电压,确定若FPGA正常工作需要几档电压,好设计电源电路;(2)考虑功耗,这决定着需要多大功率的电源才能驱动芯片正常工作;(3)查看时钟网络的分布,这决定在进行逻辑设计时时钟分配的问题;(4)JTAG下载电路,这一部分是决定能否数据配置成功的关键;(5)查看器件工作的最高频率,这决定着系统能够运行的最大带宽有多少。

对于功耗的计算部分,需要在系统最高时钟频率下,找到一个浩大的工程,计算所消耗的电流部分,然后查看所设计的电源电路的理论值是否能够满足功耗的需求。由于FPGA内核消耗较大,所以设计电源电路时应以内核功耗为准,即1.2V内核的消耗大于3.3V的I/O消耗,

2 FPGA芯片确定

对于FPGA芯片的确定以及后面PCB的制作,都需要查看Altera的官方手册,设计来源于手册。对于手册大致分为几个部分:(1)Cyclone xx 成员总览;(2)逻辑单元和逻辑阵列块;(3)存储单元;(4)嵌入式乘法器资源;(5)时钟网络资源;(6)I/O特性;(7)上电复位特性;(8)JTAG下载;

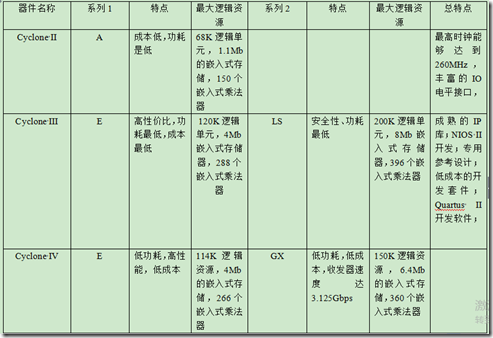

Cyclone系列芯片对比如表2.1所示:

由于Cyclone系列的片子都不算便宜,一片都要几十块,所以不求最贵的,但求资源够用即可。对比资源情况,货源,价钱情况,选择Cyclone III EP3C5E144C8N。更多详细的资源还请各位去查相关的手册,设计来源于手册。

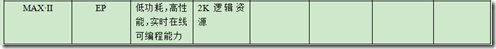

对于所选的型号,我们应该有一个定性的认识。当拿到一款芯片时,我们能大致估计这个芯片的一些信息,图2.7是芯片型号的信息解释。

图2.7芯片型号说明

对于我们所选择的芯片信号Cyclone III EP3C5E144C8N,其表达的信息为:

上述型号中有一个参数信息就是速度等级,这代表什么呢?笔者对于事物充满了好奇心,搜索了相关的资料,总结如下:

(1) 对于Altera芯片,序号越低,速度等级越高,片子越贵。速度快慢:C6 > C7 > C8;Xilinx速度等级划分与Altera相反;

(2) 每一个速度等级划分是片子生产出来之后进行测试,快的标记为低的序列号,慢的标记高的序列号;

(3) 速度等级的选取方面,本着够用就行的原则,能用慢的则用慢的。快的芯片价格较高,不容易买到。

所以对于速度等级,可以选择C8级别,这也是市面上常用的级别。对于时序若是不满足要求,可以通过高质量的verilog代码去实现时序方面的收敛问题。

3 SDRAM芯片确定

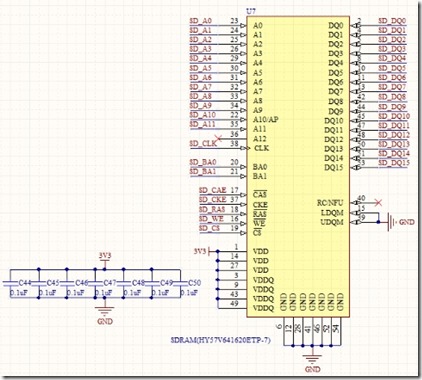

基于价格,兼容性分析,选用几款常用的SDRAM芯片,如hynix公司的HY57V641620ET-6,HY57V283220T-6,HY57V2562GTR-75C,以及ISSI公司的IS42S1632B-7TIL(terasic开发板上面所用),还有Micron公司的产品MT48LC8M32B2TG-6,以上几款产品除容量和位宽不一致外,操作时序都一样。更详细的信息可以参见SDRAM文件夹中的手册部分。

SDRAM的电路部分是较简单的,PCB layout时可以不用保证严格的走线等长,但是也不能太长,否则会造成信号的延时,对于时序可能不能够满足要求。图2.8是常用的电路设计方案。还有一点要注意的是SD_CLK,这个引脚需要接入FPGA的PLLX_CLKOUTn的引脚,目的是为了得到更低延时、更稳定可靠的时钟信号,而且SDRAM的时钟高达100MHz以上,所以就必须使用这个引脚了。具体可以查看EP3C5E的pin_out引脚文件。

图2.8 SDRAM电路

4 电源各参数确定

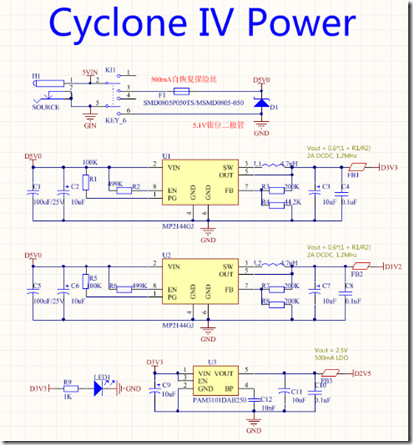

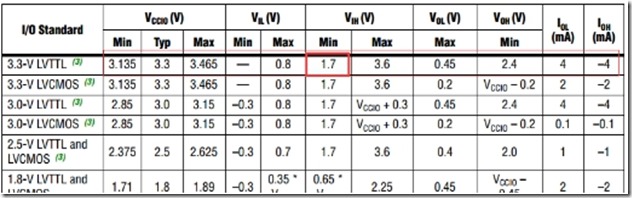

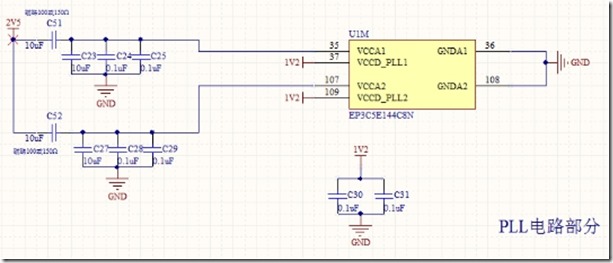

对于电源部分,查看手册如图xx所示,其中VccINT = 1.2V,VccA = 2.5V,VccD_PLL = 1.2V,对于IO电压则选择常用的3.3V, Vio = 3.3V。

图2.9 电气特性

对于FPGA而言,优质的电源输出是非常重要的,这关系到系统的稳定性。TI官网给出了一些关于FPGA的解决方案,如图2.10所示,给出FPGA内部各电流情况,看到占据较大电流的部分是内核消耗。在Quartus II中也有前期分析功耗的工具-PowerPlay Power Analyzer Tool,若是手头有一个较大的工程,可以进行烧录测试,测试前期所消耗的功耗。对于DE2-35平台上给了9V&1.3A(11.7W)的电源适配器,DE1-SOC平台上给了12V&3.5A的电源适配器,因此用一般2A或者1A的电源适配器绰绰有余。在电源设计时有两个概念比较重要,一个是LDO,一个是DC-DC,下面解释一下LDO和DC-DC的区别。

LDO 是一种线性稳压器,DC-DC是直流变(到)直流(不同直流电源值的转换),如果输入电压和输出电压很接近,最好是选用LDO稳压器,可达到很高的效率。所以,在把锂离子电池电压转换为3V输出电压的应用中大多选用LDO稳压器。虽说电池的能量最後有百分之十是没有使用,LDO稳压器仍然能够保证电池的工作时间较长,同时噪音较低。如果输入电压和输出电压不是很接近,就要考虑用开关型的DCDC了,因为从上面的原理可以知道,LDO的输入电流基本上是等于输出电流的,如果压降太大,耗在LDO上能量太大,效率不高。DC-DC转换器包括升压、降压、升/降压和反相等电路。DC-DC转换器的优点是效率高、可以输出大电流、静态电流小。随着集成度的提高,许多新型DC-DC转换器仅需要几只外接电感器和滤波电容器。但是,这类电源控制器的输出脉动和开关噪音较大、成本相对较高。总的来说,升压是一定要选DCDC的,降压,是选择DCDC还是LDO,要在成本,效率,噪声和性能上比较。

压差Dropout、噪音Noise、电源抑制比(PSRR)、静态电流Iq,这是LDO的四大关键数据。PSRR越高,LDO输出纹波越低。Iq是芯片自身消耗的电流,应当尽量选小的Iq。

图2.10 TI对FPGA芯片电压和电流分析

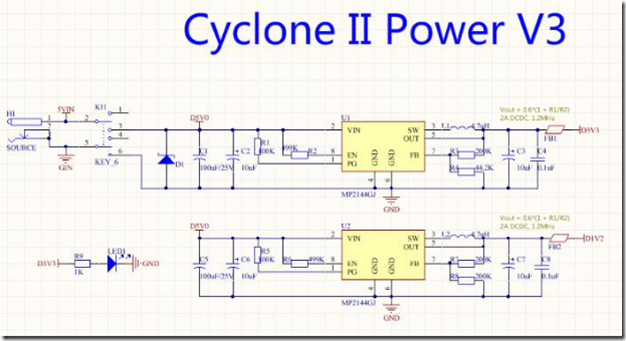

对于电源部分的设计,采用如下几个方案,对于只有3.3V和1.2V的电源设计,可以采用图2.11所示的电路。这里的D1采用了5.1V的稳压二极管(作钳位用),防止短接、防止外部输入电压过高而烧坏电路!采用两路并行的DC-DC实现最大可达到3A的3.3V和1.2V电压。当然对于常用的AMS1117这款芯片,是基于LDO的,也可以去用,不过电流最大好像只能达到1A,对于有些功耗较高的场合可能需要重新考虑,不过一般的情况应该能够适应。对于Cyclone III代之后,又增加了2.5V电压部分,可以仿照上述电路生成2.5V即可,如图2.12所示,只需修改MP芯片输出的FB处的两个电阻值即可。除了上述的解决方案之外,也可以选用电源专用芯片如TI的TPS75003也是一个不错的选择,若是对于成本不是很敏感的情况下。

图2.11 电源设计

5 下载和配置电路确定

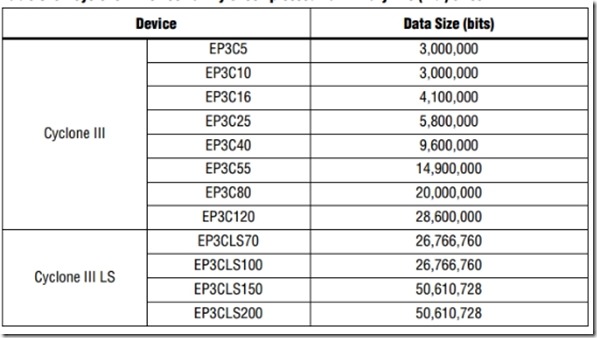

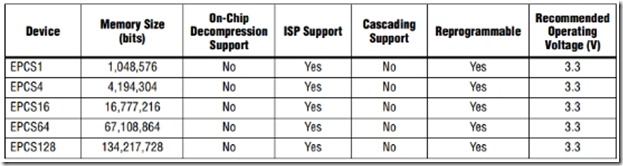

对于配置电路部分,需要考虑的因素也是较多的,PCB的layout是一方,那么对于flash芯片的选型也是需要格外注意的。图2.12是EP3C5内部资源情况。那么在选用EPCS芯片时,如图2.13,其内存数据必须大于EP3C5的内部资源量,否则可能会造成存储不成功。在做NIOS时也需要较大内存的EPCS,可以选用EPCS16。

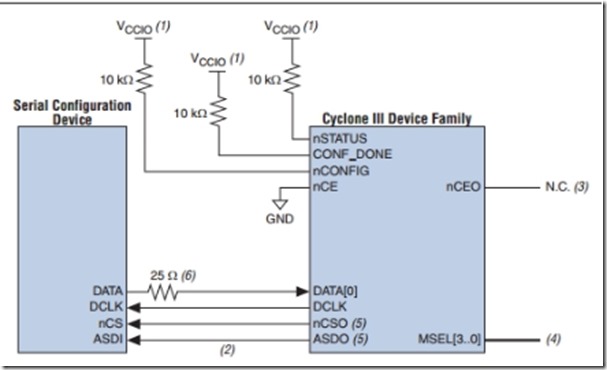

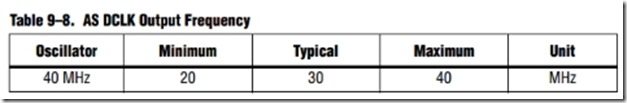

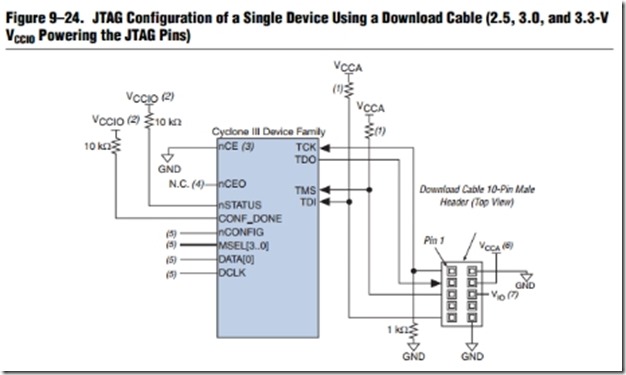

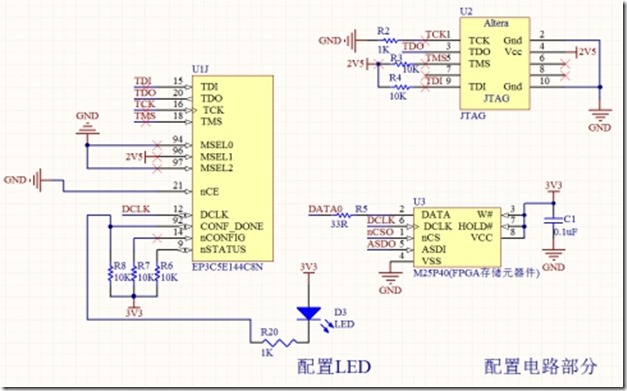

官方资料上面给出了EPCS与FPGA的连接方式,如图2.14,注意DATA处的匹配电阻可以按照官网上面的25Ω,一般常接上一个33R,注意status,conf_done和nconfig的上拉电阻,这里需要严格按照官网上指定的电路,否则有可能下载不成功。这里的配置AS模式,时钟最大可以达到40MHz。如图2.15所示。JTAG与FPGA接入部分如图2.16所示,采用VccA 专用2.5V电压进行供电,这一点需要注意的,且TMS和TDI接上拉电阻,TCK处接下拉电阻,JTAG是一种常用的下载方式,更多的说明可以查看JTAG文件夹中的文件。

下载电路部分和配置电路部分总的接入图如图2.17所示,加入一个配置LED,可以随时观察下载情况。由于选用了AS模式,注意MSEL的配置方式,如图2.18所示。

图2.12 EP3CS5配置数据量

图2.13 EPCS4支持的内存

图2.14 EPCS与FPGA通信

图2.15 EPCS与FPGA通信最高时钟频率

图2.16 JTAG与FPGA通信

图2.17 下载与配置电路

图2.18 AS模式下的MSEL配置

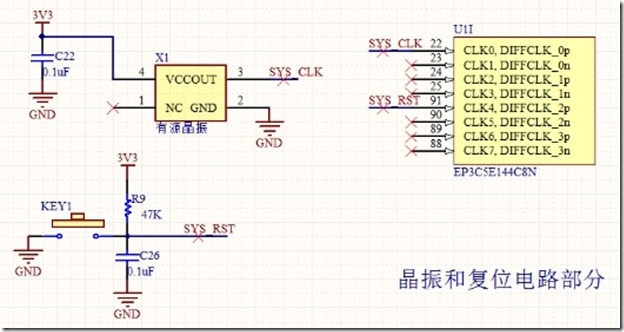

6 晶振和复位以及PLL电路确定

晶振采用有源晶振50MHz,接入3.3V电压并加上去耦电容,接入到FPGA的专用时钟引脚上。因为时钟和复位需要走全局时钟网络,已达到对时钟信号延迟达到最小。

复位电路这里根据手册上面输入电压迈过1.7V的阈值电压之后如图2.18,FPGA芯片便开始进行逻辑的配置,配置时间取决于逻辑资源的多少。对于上面配置电路来讲,在AS模式下,最高40MHz,最低20MHz,对应的周期为20ns~50ns,对应最坏情况需要3000 000 bit x 50ns/bit = 150ms,那么阻容复位时间 t = RC x Ln[(VI – V0)/( VI – Vt)],对于VI = 3.3V Vt = 1.7V,V0 = 0情况,t = 0.7239RC;对于选定R = 47K,C = 10μF,得到t = 0.34s,大于FPGA复位上电时间。PLL电路的输入端接入10μF,0.1μF电容并联,已得到干净的PLL电源输入。图2.20是整个电路图部分。

图2.19 EP3C5特性

图2.20 复位晶振和PLL电路部分

《FPGA全程进阶----实战演练》第二章之系统搭建的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第二十一章 电源常用类型:LDO和 DCDC

高速电路中的电源设计 高速电路中的电源设计大概分为两种,一种是集总式架构,一种是分布式架构.集总式架构就是由一个电源输入,然后生成多种所需要的电压.如图1所示.这种架构会增加多个DC/DC模块,这样成 ...

- 《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解. 1 模块划分 对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电 ...

- 《FPGA全程进阶---实战演练》第二十一章之 几种常用电平分析及特性

TTL,CMOS以及LVTTL,LVCMOS TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本.TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大, ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

1基础理论部分 1.1分频 分频,是的,这个概念也很重要.分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频.实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ ...

随机推荐

- Android 报错:Conversion to Dalvik format failed: Unable to execute dex: java.nio.BufferOverflowException. Check the Eclipse log for stack trace.

在android高版本开发环境(sdk 4.4)导入低版本(sdk 3.0)的工程时编译报错,报错信息如:Conversion to Dalvik format failed: Unable to e ...

- 如何恢复 Linux删除的文件

原理及普通文件的恢复 要想恢复误删除的文件,必须清楚数据在磁盘上究竟是如何存储的,以及如何定位并恢复数据.本文从数据恢复的角度,着重介绍了 ext2 文件系统中使用的一些基本概念和重要数据结构,并通过 ...

- python标准库介绍——10 sys 模块详解

==sys 模块== ``sys`` 模块提供了许多函数和变量来处理 Python 运行时环境的不同部分. === 处理命令行参数=== 在解释器启动后, ``argv`` 列表包含了传递给脚本的所有 ...

- PHP通过__call实现简单的AOP(主事务后的其他操作)比如前置通知,后置通知

/** * person class */ class Person { /** * person class -> function say */ public static function ...

- laravel5的Bcrypt加密方式对系统保存密码

laravel5文档介绍 //对 A 密码使用Bcrypt 加密 $password = Hash::make('mima'); //你也可直接使用 bcrypt 的 function $passwo ...

- 使用 bat cmd命令杀掉 删掉运行的程序

删掉所有xx.exe开启的进程 taskkill /f /im xx.exe 开启xx.exe start xx.exe 根据标题栏信息删除 taskkill /f /FI "windows ...

- centos配置nfs服务详细步骤(centos开启nfs服务)

一.NFS服务简介 NFS 是Network File System的缩写,即网络文件系统.一种使用于分散式文件系统的协定,由Sun公司开发,于1984年向外公布.功能是通过网络让不同的机器.不同的操 ...

- java刚開始学习的人常见的问题

){ out.write(c); } }finally{ if(in!=null){ ...

- [svc][op]vim常用命令汇总

vim常用命令汇总: 定位 本行第一个字符 ctrl+$ 本行最后一个字符 0gg 文章首行 ctrl+G 文章行尾 u 撤销(Undo) 删除 D 从当前位置删除到行尾 ("d$" ...

- [sh]shell小结

一 判断 -d 测试是否为目录.-f 判断是否为文件. -s 判断文件是否为空 如果不为空 则返回0,否则返回1 -e 测试文件或目录是否存在. -r 测试当前用户是否有权限读取. -w 测试当前用户 ...