DRAM(动态)存储器

一、DRAM的存储元电路

常见的DRAM存储元电路有四管式和单管式两种,它们的共同特点是靠电容存储电荷的原理来存储信息。电容上存有足够多的电荷表示“1”,电容上无电荷表示“0”。 由于电容存储的电荷会逐渐泄漏,即使电源不掉电,信息也会很快消失,应用中需要定时恢复存储的电荷。与SRAM相比,DRAM具有集成度高,功耗低等特点,目前被广泛应用于各类计算机中。

四管DRAM存储元

二、

刷新操作:由于存储的信息电荷终究是有泄漏的,时间久了,信息就会丢失。为此,必须设法由外界按一定规律不断给栅极进行充电,补足栅极的信息电荷,这就是所谓“再生”或“刷新”。

设原存信息为“1”,T1管截止,T2管导通。若经过一段时间,T2管栅极上漏失一部分信息电荷,使A端的电压稍小于存“1”时的满值电压。此时,在字选择线上加脉冲,T5、T6开启,A端与位线D相连,从而充电到满值电压,刷新了原存“1”的信息。因此,定时给全部存储单元电路执行一遍读操作,就可以实现信息再生。

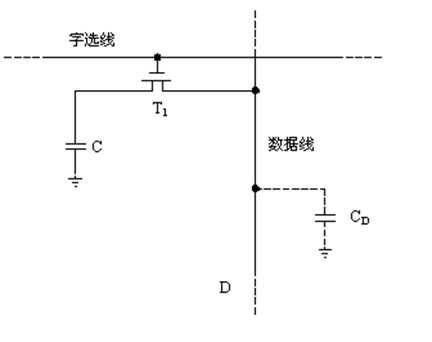

三、单管DRAM存储元

为提高芯片的存储密度,现在动态RAM芯片中一般采用图4-9所示的单管动态存储元电路,其中T1管为字选控制管,字选线有效(高电位)使其导通。

读操作:字选择线为“1”,使T1管导通。若原存“1”,则C上电荷通过T1管向位线(数据线)泄放,通过读出放大器形成读“1”信号。反之,若原存“0”,则无泄放电流。因为读出时C电荷泄放,电位下降,所以是破坏性读出,在读出后应有重写操作。

写操作:字选择线为“1”,使T1管导通。要写“1”,在位线(数据线)上加高电位,经T1管对C充电;写“0”则在数据线上加低电位,使CD上无电荷。

刷新操作:由于MOS管栅极电容上存储的电荷会缓慢泄放,超过一定时间(2~3.3ms),就会丢失信息。因此必须定时给栅级电容补充电荷,进行“刷新”操作。

单管DRAM存储元电路

四、DRAM存储器芯片的读/写周期

读周期

DRAM的读周期时序如图4-11(a)所示。

为了使芯片能正确地接收行、列地址并实现读操作,各信号的时间关系应符合下面的要求:行地址必须在RAS#信号有效之前送到芯片的地址输入端;CAS#信号应滞后RAS#一段时间,并滞后于列地址送到芯片地址输入端的时间;RAS#、CAS#应有足够的宽度;WE#信号为高,并在CAS#有效之前建立。

图为DRAM时序

写周期

DRAM的写周期时序如图4-11(b)所示。

有两点需要说明一下:

1、WE#信号为低,并在信号CAS#有效之前建立。

2、数据必须在CAS#有效之前出现在DIN端。

五、DRAM的刷新

刷新的实质是先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程。由于存储元被访问是随机的,有可能某些存储元长期得不到访问,无读出也就无重写,其原信息必然消失。为此,必须采用定时刷新的方法,规定在一定的时间内,对DRAM的全部存储元电路做一次刷新,这一段时间间隔叫做刷新周期,或叫再生周期,一般取2ms、4ms或8ms。

DRAM(动态)存储器的更多相关文章

- [CSAPP笔记][第六章存储器层次结构]

第六章 存储器层次结构 在简单模型中,存储器系统是一个线性的字节数组,CPU能够在一个常数访问每个存储器位置. 虽然是一个行之有效的模型,但没有反应现代系统实际工作方式. 实际上,存储器系统(memo ...

- 简单介绍nandflash、norflash、ram、sram、dram、rom、eeprom、flash的差别

1.nandflash Nandflash是IO设备,数据.地址.控制线都是共用的,须要软件区控制读取时序, 所以不能像nor flash.内存一样随机訪问,不能EIP(片上执行).因此不能直 ...

- 第22章 常用存储器介绍—零死角玩转STM32-F429系列

第22章 常用存储器介绍 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/firege ...

- int指令

body, table{font-family: 微软雅黑; font-size: 13.5pt} table{border-collapse: collapse; border: solid gra ...

- 深入解析内存原理:RAM的基本原理

1. 寻址原理概述RAM 主要的作用就是存储代码和数据供CPU 在需要的时候调用.但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用有格子的书架存放书籍一样,不但要放进去还要能够在需要的时候准确 ...

- 【ARM】arm系列知识框架

[ARM编程模型] 硬件: 电路原理图 软件: 体系结构, 指令集, 寄存器组 [ARM编程技术] 汇编/C语言 编译, 链接, 烧写和调试 windows: MDK linux : gcc [AR ...

- 【CSAPP】一、计算机系统漫游

一.位+上下文 文本文件 / 二进制文件: 文本文件是只由ASCII码构成的文件 二.从源代码到可执行文件的顺序 源代码 ——> 可执行文件(机器代码)共有四步: 全过程代码 gcc hello ...

- 系统启动时,BIOS与影子内存_5

问题:“当我们按下电源开关时,电源开始供电,芯片组撤去RESET信号,CPU马上就从地址FFFF0H处开始执行指令,这个地址在系统BIOS的地址范围内,无论是Award BIOS还是AMI BIOS, ...

- FPGA第一篇:SRAM工作原理

一.SRAM概述 SRAM主要用于二级快速缓存(Level2 C ache). 它利用晶体管来存储数据.与DRAM相比,SRAM的速度快,但在同样面积中SRAM的容量要比其它类型的内存小. 大部分FP ...

- 【CUDA 基础】4.1 内存模型概述

title: [CUDA 基础]4.1 内存模型概述 categories: - CUDA - Freshman tags: - CUDA内存模型 - CUDA内存层次结构 - 寄存器 - 共享内存 ...

随机推荐

- JavaScript数据结构-13.散列碰撞(开链法)

<!DOCTYPE html> <html> <head> <meta charset="UTF-8"> <title> ...

- Mac 提交代码到Github

然后在GitHub上创建版本库(Repository),在GitHub首页上,点击“Create a New Repository”,如下所示(为了便于后面演示,创建README.md这步暂不勾选): ...

- WPF中Popup等弹窗的位置不对(偏左或者偏右)

1.情况如图: 正常情况: 部分特殊情况: 在一般的电脑都能正确显示,就是第一种情况,同样的代码为什么在不同的电脑就会显示不同的位置呢,原来Windows为了满足 不同需求的用户,左撇 ...

- iOS语音播报文字

记得大学的时候学微软Window Phone时,有语音识别类似苹果的嘿,Siri.今天无聊百度搜了一下,搜到苹果语音播报文字.自己试了下还挺好玩. 1.引入框架#import <AVFounda ...

- mysql备份 小结 (三种方式的详细解读)

备份的本质就是将数据集另存一个副本,但是原数据会不停的发生变化,所以利用备份只能回复到数据变化之前的数据.那变化之后的呢?所以制定一个好的备份策略很重要 新建一个all.sqlvim all.sql在 ...

- xsl 和xml transform方法的调用

xsl 和xml生成html,兼容多个浏览器 <html> <head> <meta charset="UTF-8"/> </head&g ...

- jQuery 表格中实现“删除线”的增进方法

之前做了一个删除线的效果,就是类似这样的,在内容的中间加一条线. 但是又有点不同的是,这种删除线不是单纯的在文字之上,而是给一个Table中的一行加上这种删除线效果. 这里有两个方法,是在不同时期写的 ...

- MySQL Metadata

http://www.devart.com/dotconnect/mysql/docs/MetaData.html In this overload first parameter is name o ...

- Luogu4433:[COCI2009-2010#1] ALADIN(类欧几里德算法)

先套用一个线段树维护离散化之后的区间的每一段的答案 那么只要考虑怎么下面的东西即可 \[\sum_{i=1}^{n}(A\times i \ mod \ B)\] 拆开就是 \[\sum_{i=1}^ ...

- BZOJ4602: [Sdoi2016]齿轮(并查集 启发式合并)

题意 题目链接 Sol 和cc的一道题很像啊 对于初始的\(N\)个点,每加一条限制实际上就是合并了两个联通块. 那么我们预处理出\(val[i]\)表示的是\(i\)节点所在的联通块根节点转了\(1 ...