14-Verilog for Verification

Verilog for Verification

1.引言

Testbench也是一个模块(module...endmodule)

Testbench没有输入和输出,因为它是一个闭环,自己产生激励,灌给module,module输出响应,testbench会捕捉响应,进行比较,自己在自己内部形成闭环

完成对待测设计的例化,测试代码的封装,提供测试激励,收集测试结果

无需综合,行为级描述优先

module module_name_tb;

//测试代码

endmodule

2.变量声明

- 给待测设计的输入端口提供激励

- 通过待测实际的输出端口收集激励

- 提供激励的信号:reg类型信号进行声明,便于在initial和always中进行赋值

- 收集激励的信号:reg或wire,多数情况下使用wire

- 也可以使用logic变量进行声明

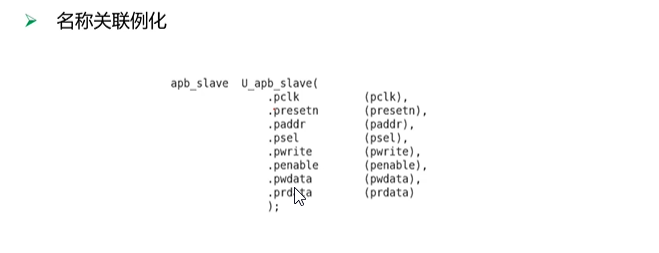

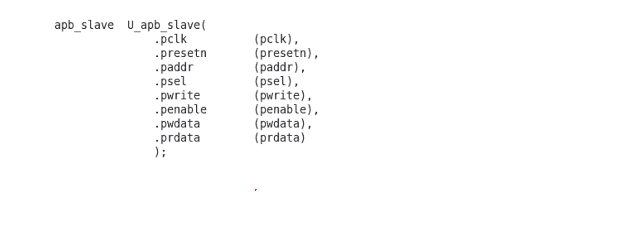

// 名称关联的方式

apd_slave U_apb_slave(

.pclk (pclk),

.prestn (prestn),

.paddr (paddr),

.psel (psel),

.pwrite (pwrite),

.penable (penable),

.pwdata (pwdata),

.prdata (prdata)

);

3.激励

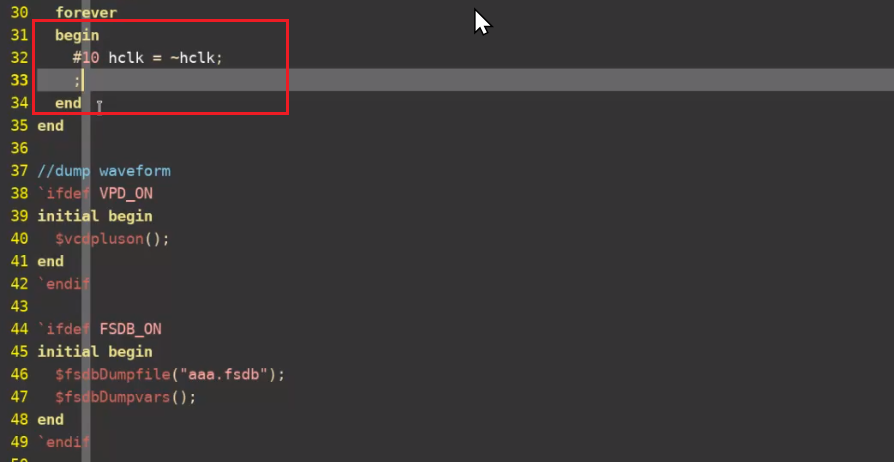

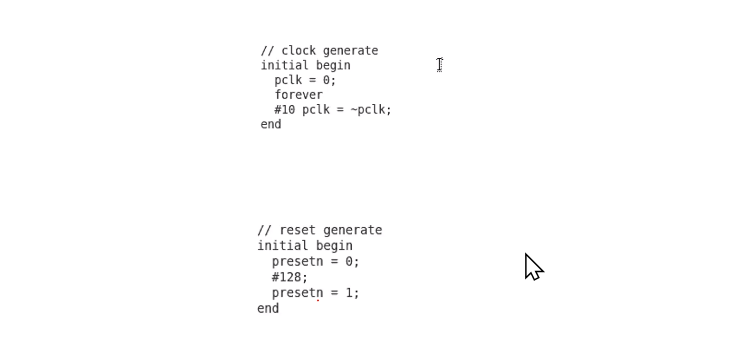

3.1 时钟产生

- forever语句,必须写在initial中

- forever后面执行多条语句,加begin end

// clock generate

initial begin

pclk = 0;

forever

begin

#10 pclk = ~pclk; // 时钟周期是20个时间单位

end

3.2 reset信号

- 低电平有效

- 在某个时间点将reset置为0

reg rst_n;

initial begin

rst_n = 1'b0; // 复位信号置为低电平

#45;

rst_n = 1'b1; // 延迟45个时间单位之后,将复位撤销

end

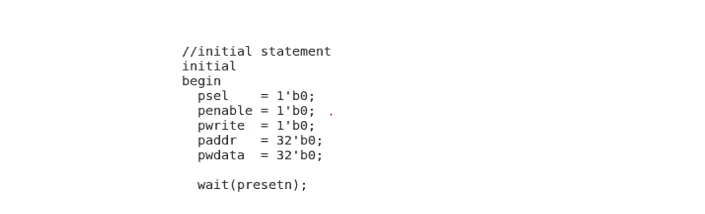

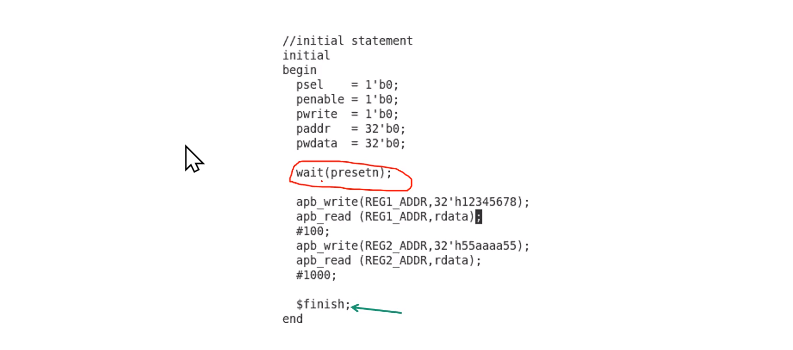

3.3 产生激励

- wait(条件表达式),条件表达式为真的时候解除等待

initial begin

......

wait(rst_n = 1'b1);

wait(sim_start)

......

end

- @(posegde clk) ...

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

a = 1'b1;

end

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

#3; // 寄存器d到q端的延迟

a = 1'b1;

end

- function是不能有延迟信息语句的

- task是可以具有延迟信息语句的

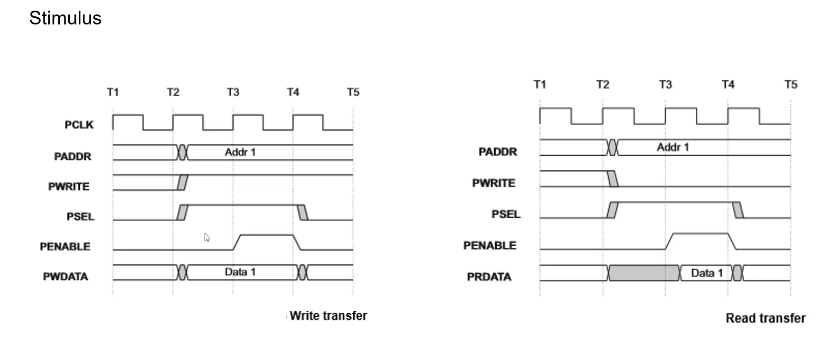

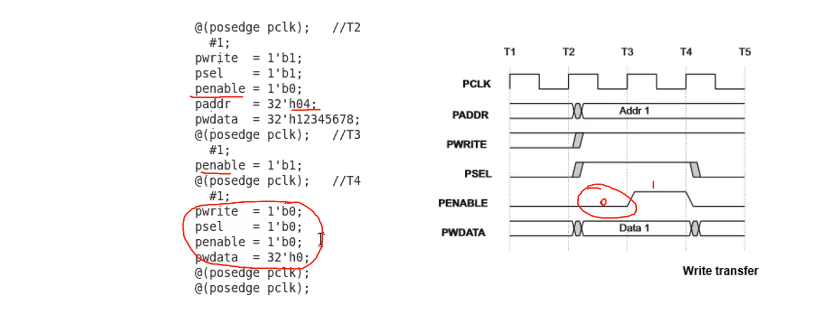

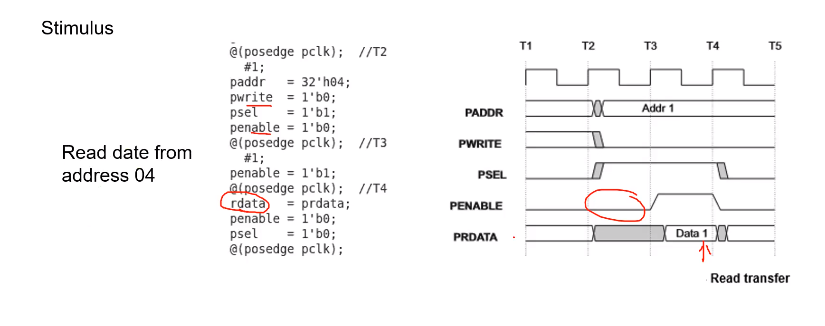

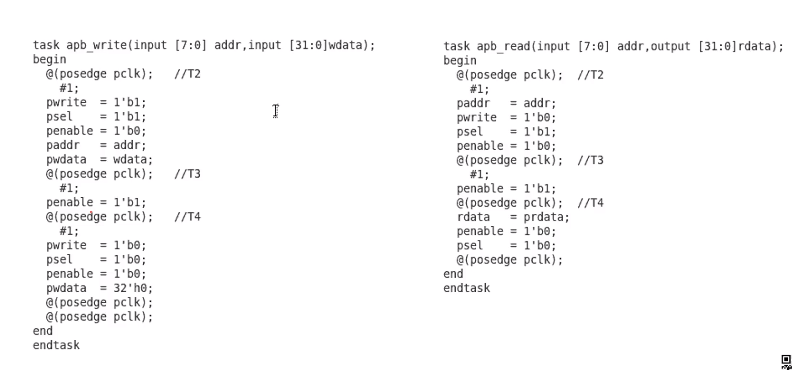

- 将读写操作封装成task

task apb_write(input [31:0] addr,input [31:0] wdata);

begin

end

endtask

task apb_read(input [31:0] addr,output [31:0] rdata);

begin

end

endtask

reg [31:0] memory [1024:0]

FILE0 = $open("block90");

for(address=32'h0,address<32'h80;address=address+1)

$fwriteh(FILE0,32'hFFFFFFFF,"\n")

$fclose(FILE0)

$readmemh("block0",memory);

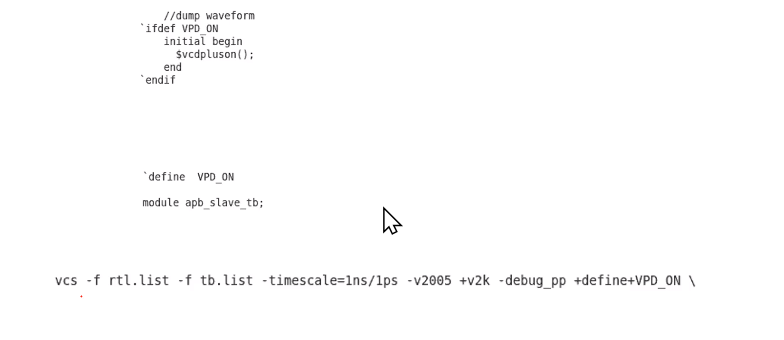

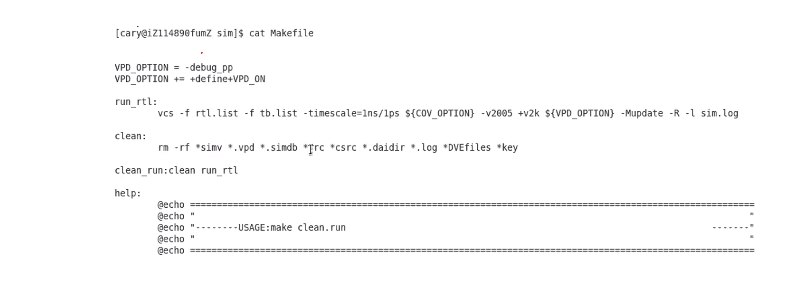

3.4 dump 波形

`ifdef VPD_ON

initial begin

$vcdpluson();

end

`endif

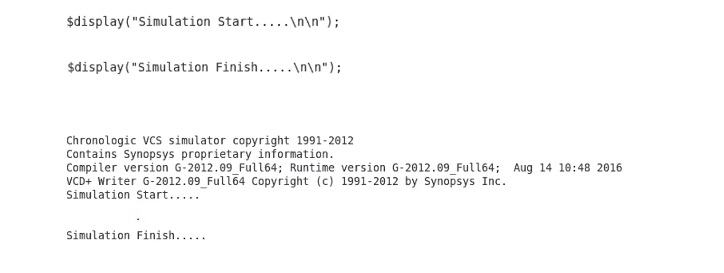

3.5 显示激励

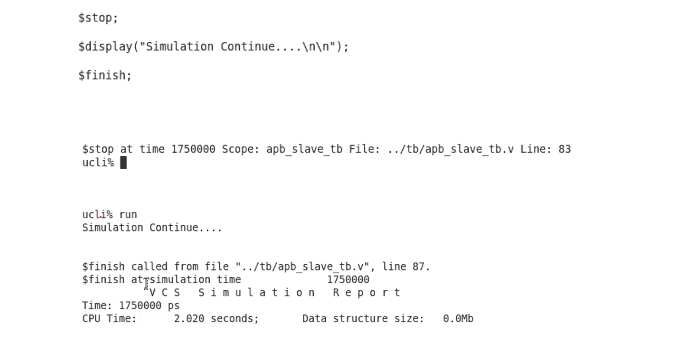

3.6 结束仿真

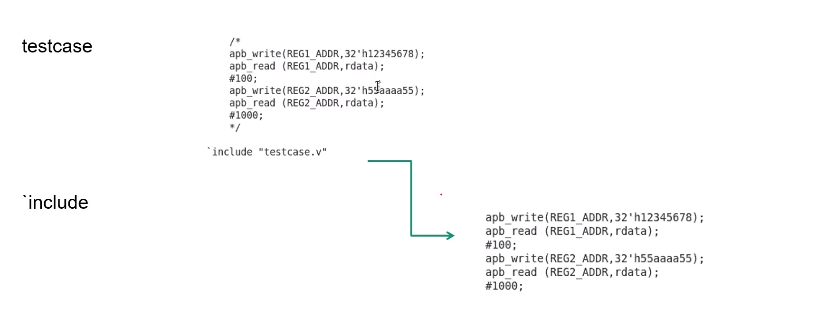

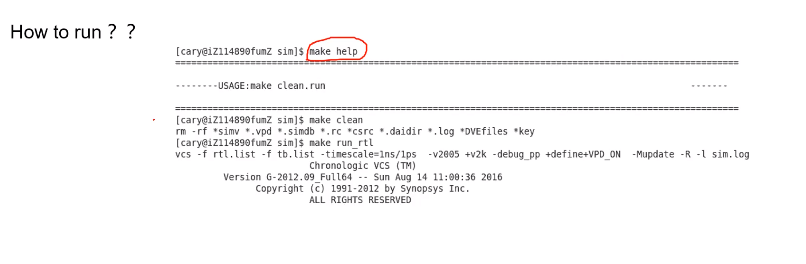

3.7 预编译

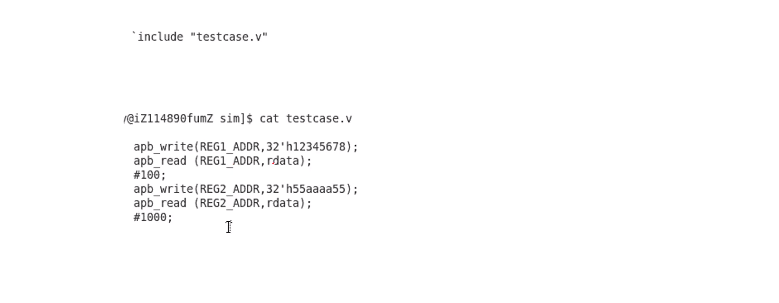

3.8 include

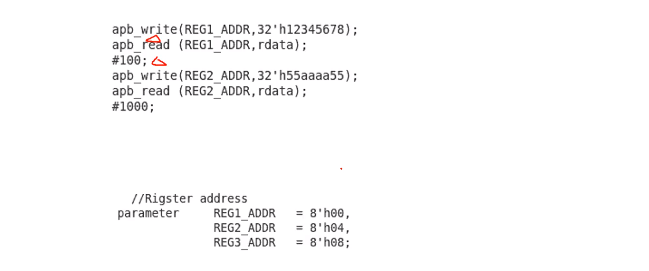

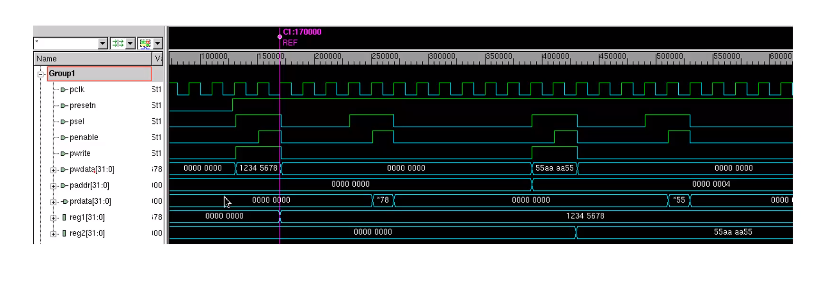

4.实例

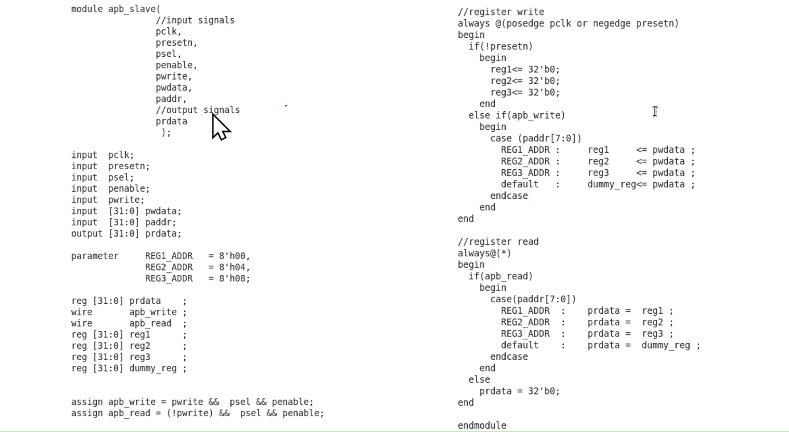

4.1 设计代码

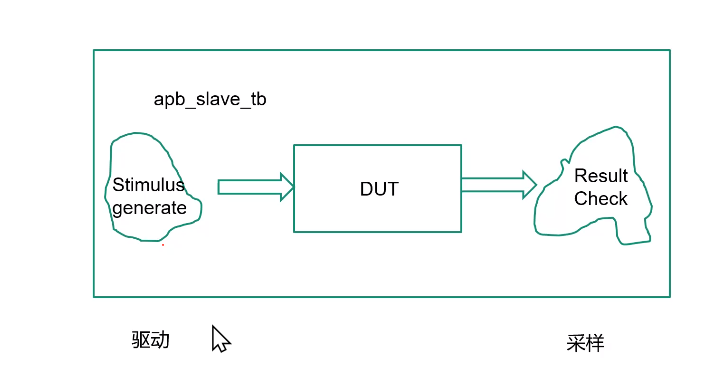

4.2 验证流程

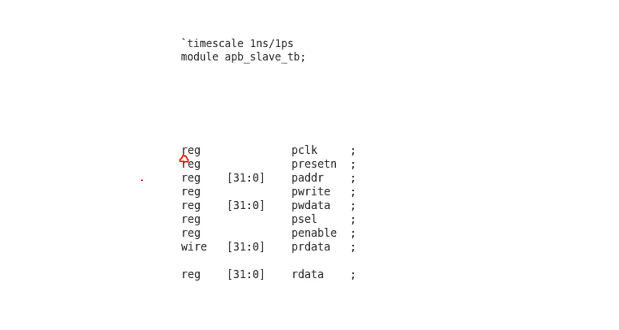

4.3 APB Slave testbench

- testbench中输入定义为reg,输出定义为wire

- 例化模块

- 产生时钟和复位

- 产生激励,产生激励的时候要给模块的输入一定的初始值,不给初始值就会产生x态

14-Verilog for Verification的更多相关文章

- Team Foundation Server 2013 with Update 3 Install LOG

[Info @10:14:58.155] ====================================================================[Info @ ...

- SpringBoot+mybatis:报错Fri Oct 19 14:29:24 CST 2018 WARN: Establishing SSL connection without server's identity verification is not recommended. According to MySQL 5.5.45+, 5.6.26+ and 5.7.6+ requiremen

报错:Fri Oct 19 14:29:24 CST 2018 WARN: Establishing SSL connection without server's identity verifica ...

- Xilinx ISE 14.1利用Verilog产生clock

<一>建立如下的Verilog Module module myClock( input clock ); endmodule <二>建立 Verilog Test Fixtu ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

- 【设计经验】5、Verilog对数据进行四舍五入(round)与饱和(saturation)截位

一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件:Vivado2015.4.2 Matlab2016a 仿真工具:Vivado自带仿真器 二.引言 在利用 ...

- Verilog对数据进行四舍五入(round)与饱和(saturation)截位

转自https://www.cnblogs.com/liujinggang/p/10549095.html 一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件 ...

- verilog FAQ(zz)

1. What is the race condition in verilog? Ans :The situation when two expressions are allowed to exe ...

- system verilog的一些总结(从其他博客复制来的)

转载自 http://blog.sina.com.cn/s/blog_e7fec2630101f5t9.html SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 136 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- Verilog语法基础讲解之参数化设计

Verilog语法基础讲解之参数化设计 在Verilog语法中,可以实现参数化设计.所谓参数化设计,就是在一个功能模块中,对于一个常量,其值在不同的应用场合需要设置为不同的置,则将此值在设计时使用 ...

随机推荐

- 使用nginx搭建creates.io镜像(稀疏索引)

在Rust开发中,经常需要使用Cargo从crates.io下载依赖,而国内几乎没有好用的crates.io镜像,大多都只对crates.io-index和crates.io进行了镜像,而最重要的st ...

- [BUG]自定义登录引发的配置加载问题-bugspringsecurity

title: [BUG]自定义登录引发的配置加载问题 date: 2021-12-10 16:43:36.311 updated: 2021-12-27 19:10:16.773 url: https ...

- Ubuntu系统 安装 Zabbix Server 6.0

Zabbix6.0简介: zabbix6.0新特性 1.开箱即用的Zabbix server高可用群集 Zabbix server高可用防止硬件故障或计划维护期的停机: 原生选择加入HA群集配置 定义 ...

- MyBatis中使用#{}和${}占位符传递参数的各种报错信息处理

在Mapper层使@Select注解进行SQL语句查询时,往往需要进行参数传入和拼接,一般情况下使用两种占位符#{参数名}和${参数名},两者的区别为: 一.两种占位符的区别 1.参数传入方式的区别 ...

- PyTorch项目源码学习(1)

PyTorch PyTorch是一个开源的深度学习框架,项目地址 https://github.com/pytorch/pytorch 在学术工作中的使用频率较高.其主体由C++开发,PyTorch是 ...

- Provider 四种消费者

Provider.of Provider.of 方法是 Provider 库中最常用的获取共享数据的方法之一.它接收一个 BuildContext 对象和一个泛型类型参数 T,会查找 Widget 树 ...

- DTSE Tech Talk 第18期丨统计信息大揭秘,数仓SQL执行优化之密钥

摘要:华为云EI DTSE技术布道师王跃,针对统计信息对于查询优化器的重要性,GaussDB(DWS)最新版本的analyze当前能力,与开发者和伙伴朋友们展开交流互动,帮助开发者快速上手使用统计信息 ...

- 6个步骤强化 CI/CD 安全

快速的数字化和越来越多的远程业务运营给开发人员带来了沉重的负担,他们不断面临着更快推出软件的压力.尽管CI/CD 加速了产品发布,但它容易受到网络安全问题的影响,例如代码损坏.安全配置错误和机密管理不 ...

- Vue 多环境配置

没有使用 package.json 进行配置 ,改配置时不需要重新打包 Vue 多环境配置 package.json settings.js window.environment="dev& ...

- STM32CubeMX教程16 DAC - 输出3.3V内任意电压

1.准备材料 开发板(正点原子stm32f407探索者开发板V2.4) STM32CubeMX软件(Version 6.10.0) keil µVision5 IDE(MDK-Arm) ST-LINK ...