DC综合简单总结(2)

DC综合简单总结(2)

建立时间和保持时间和数据输出延时时间

一、概念

建立时间和保持时间都是针对触发器的特性说的。

建立时间(Tsu:set up time)

是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time)

是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

输出相应时间(Tco)

触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化,也即触发器的输出延时。

二、数字系统设计常见与之有关的问题

1、问题提出

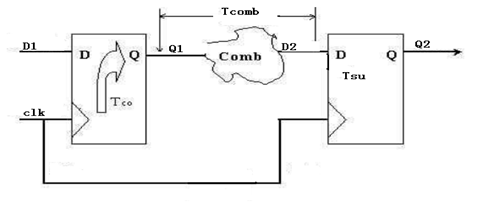

数字系统设计常见的电路图,这里需要保证数据能够正确的在这两个触发器上进行传输,由此确定中间组合逻辑电路的传输延时的范围。

Tcomb: 组合逻辑电路的传输延时

2、第二个触发器要满足建立时间的约束条件

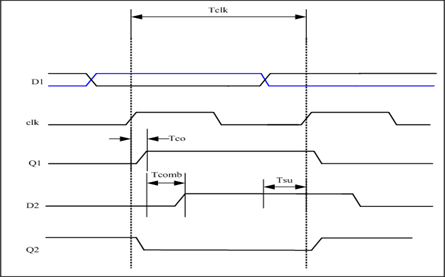

时序图如下,假设D1的输入为图中的蓝线所示

时序解释:

在第一个时钟上升沿,前边的触发器采集D1信号,将高电平打入触发器,经过Tco的触发器输出延时到达组合逻辑电路。又经过组合逻辑电路的延时Tcomb(我们假定组合逻辑电路此时没有改变信号的高低,可以把它假定为一个缓冲器)送到了D2接口上。在第二个时钟上升沿到来之前,D2数据线上的信号要满足稳定时间>触发器的建立时间Tsu。

Tclk - Tco - Tcomb > Tsu

考虑最坏的情况:触发器的输出延时最大,组合逻辑电路的延时也最大,可得:

Tclk - Tco-max - Tcomb-max > Tsu

3、第二个触发器要满足保持时间的约束条件

时序图如下,假设D1的输入为图中的蓝线所示

时序解释:

接着之前的时序图继续,在第二个时钟上升沿前边触发器采集到D1上的低电平,经过Tco的延时在Q1上得到表达。这个低电平在经过组合电路延时Tcomb到达D2。现在的问题是经过这么Tco+Tcomb的延时,D2上原本的高电平在第二个时钟上升沿到来之后的稳定时间 > 第二个触发器的保持时间。满足了这个条件,后边的触发器才能稳定的接收到最初由D1传过来的高电平。

Tco + Tcomb > Th

考虑到最坏的情况:触发器的输出延时最小,组合逻辑电路的延时也最小

Tco-min + Tcomb-min > Th

4、问题的答案

我们得到中间组合逻辑电路的输出延时范围为:

(Tclk - Tco-max - Tsu) > Tcomb > (Th - Tco-min)

FPGA基础知识(四)锁存器、触发器、寄存器和缓冲器的区别

一、锁存器

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁存器,指的是不锁存时输出对于输入是透明的。

锁存器(latch):我听过的最多的就是它是电平触发的,呵呵。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程)。应用场合:数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

缺点:时序分析较困难。

不要锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比ff要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff来组成锁存器,这样就浪费了资源。

优点:面积小。锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

二、触发器

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发。

触发器(flip-flops)电路相互关联,从而为使用内存芯片和微处理器的数字集成电路(IC)形成逻辑门。它们可用来存储一比特的数据。该数据可表示音序器的状态、计数器的价值、在计算机内存的ASCII字符或任何其他的信息。

有几种不同类型的触发器(flip-flops)电路具有指示器,如T(切换)、S-R(设置/重置)J-K(也可能称为Jack Kilby)和D(延迟)。典型的触发器包括零个、一个或两个输入信号,以及时钟信号和输出信号。一些触发器还包括一个重置当前输出的明确输入信号。第一个电子触发器是在1919年由W.H.Eccles和F.W.Jordan发明的。

触发器(flip-flop)---对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变。

T触发器(Toggle Flip-Flop,or Trigger Flip-Flop)设有一个输入和输出,当时钟频率由0转为1时,如果T和Q不相同时,其输出值会是1。输入端T为1的时候,输出端的状态Q发生反转;输入端T为0的时候,输出端的状态Q保持不变。把JK触发器的J和K输入点连接在一起,即构成一个T触发器。

应用场合:时钟有效迟后于数据有效。这意味着数据信号先建立,时钟信号后建立。在CP上升沿时刻打入到寄存器。

三、寄存器

寄存器(register):用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位寄存器、16位寄存器等。

对寄存器中的触发器只要求它们具有置1、置0的功能即可,因而无论是用同步RS结构触发器,还是用主从结构或边沿触发结构的触发器,都可以组成寄存器。一般由D触发器组成,有公共输入/输出使能控制端和时钟,一般把使能控制端作为寄存器电路的选择信号,把时钟控制端作为数据输入控制信号。

寄存器的应用

1. 可以完成数据的并串、串并转换;

2.可以用做显示数据锁存器:许多设备需要显示计数器的记数值,以8421BCD码记数,以七段显示器显示,如果记数速度较高,人眼则无法辨认迅速变化的显示字符。在计数器和译码器之间加入一个锁存器,控制数据的显示时间是常用的方法。

3.用作缓冲器;

4. 组成计数器:移位寄存器可以组成移位型计数器,如环形或扭环形计数器。

四、移位寄存器

移位寄存器:具有移位功能的寄存器称为移位寄存器。

寄存器只有寄存数据或代码的功能。有时为了处理数据,需要将寄存器中的各位数据在移位控制信号作用下,依次向高位或向低位移动1位。移位寄存器按数码移动方向分类有左移,右移,可控制双向(可逆)移位寄存器;按数据输入端、输出方式分类有串行和并行之分。除了D边沿触发器构成移位寄存器外,还可以用诸如JK等触发器构成移位寄存器。

五、总线收发器/缓冲器

缓冲寄存器:又称缓冲器缓冲器(buffer):多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。当负载不具有非选通输出为高阻特性时,将起到隔离作用;当总线的驱动能力不够驱动负载时,将起到驱动作用。由于缓冲器接在数据总线上,故必须具有三态输出功能。

它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。

Buffer:缓冲区,一个用于在初速度不同步的设备或者优先级不同的设备之间传输数据的区域。通过缓冲区,可以使进程之间的相互等待变少,从而使从速度慢的设备读入数据时,速度快的设备的操作进程不发生间断。

缓冲器主要是计算机领域的称呼。具体实现上,缓冲器有用锁存器结构的电路来实现,也有用不带锁存结构的电路来实现。一般来说,当收发数据双方的工作速度匹配时,这里的缓冲器可以用不带锁存结构的电路来实现;而当收发数据双方的工作速度不匹配时,就要用带锁存结构的电路来实现了(否则会出现数据丢失)。

缓冲器在数字系统中用途很多:

(1)如果器件带负载能力有限,可加一级带驱动器的缓冲器;

(2)前后级间逻辑电平不同,可用电平转换器加以匹配;

(3)逻辑极性不同或需要将单性变量转换为互补变量时,加带反相缓冲器;

(4)需要将缓变信号变为边沿陡峭信号时,加带施密特电路的缓冲器

(5)数据传输和处理中不同装置间温度和时间不同时,加一级缓冲器进行弥补等等。

六、锁存器与触发器的区别

锁存器和触发器是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为latch和flip-flop二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生;DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平的时候)相当于导线了,随输出而变化。在非使能状态下是保持原来的信号,这就可以看出和flip-flop的差别,其实很多时候latch是不能代替ff的。

4、latch将静态时序分析变得极为复杂。

5、目前latch只在极高端的电路中使用,如intel 的P4等CPU。 FPGA中有latch单元,寄存器单元就可以配置成latch单元,在xilinx v2p的手册将该单元配置成为register/latch单元,附件是xilinx半个slice的结构图。其它型号和厂家的FPGA没有去查证。——个人认为xilinx是能直接配的而altera或许比较麻烦,要几个LE才行,然而也非xilinx的器件每个slice都可以这样配置,altera的只有DDR接口中有专门的latch单元,一般也只有高速电路中会采用latch的设计。altera的LE是没有latch的结构的,又查了sp3和sp2e,别的不查了,手册上说支持这种配置。有关altera的表述wangdian说的对,altera的ff不能配置成latch,它使用查找表来实现latch。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

锁存器电平触发会把输入端的毛刺带入输出;而触发器由于边沿作用可以有效抑制输入端干扰。

在 CMOS 芯片内部经常使用锁存器, 但是在PCB板级结构上, 建议用触发器在时钟边沿上锁存数据。这是因为在锁存器闸门开启期间数据的变化会直接反映到输出端, 所以要注意控制闸门信号的脉冲宽度,而对于触发器,只考虑时钟的边沿。

门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。也就是晶体管->门电路->锁存器->触发器,前一级是后一级的基础。锁存器和触发器它们的输出都不仅仅取决于目前的输入,而且和之前的输入和输出都有关系。

它们之间的不同在于:锁存器没有时钟信号,而触发器常常有时钟触发信号。

锁存器是异步的,就是说在输入信号改变后,输出信号也随之很快做出改变非常快。而另外一方面,今天许多计算机是同步的,这就意味着所有的时序电路的输出信号随着全局的时钟信号同时做出改变。触发器是一个同步版锁存器。

触发器泛指一类电路结构,它可以由触发信号 (如: 时钟、置位、复位等) 改变输出状态, 并保持这个状态直到下一个或另一个触发信号来到时。触发信号可以用电平或边沿操作,锁存器是触发器的一种应用类型。

七、D触发器和D锁存器的区别

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

两个锁存器可以构成一个触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

八、寄存器与锁存器的区别

寄存器与锁存器的功能是提供数据寄存和锁存。

寄存功能是指把数据暂时保存,需要时取出。锁存功能是指总线电路中,锁定数据输出,使输出端不随输入端变化。

------------------------------------------------------

握手协议

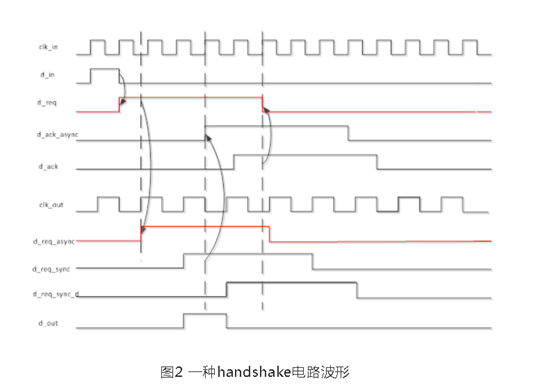

信号d_in 所处时钟域是clk_in,且d_in只有1T 的宽度,想要传送到clk_out 时钟域(clk_out 跟clk_in不相关)。

因为clk_out 和 clk_in相位关系不确定,时钟周期大小关系不确定,无法保证一定能采样到d_in。 因此需要把d_in展宽,产生d_req 信号;

d_req 信号一直拉高,经过clk_out时钟域两级DFF 同步器后,得到d_reg_sync;取d_req_sync 上升沿1T,即可得到传送到clk_out 时钟域的d_out。此时,d_in 从clk_in 传送到clk_out 的任务就算是结束了。

但对于handshake 电路来说,任务还没结束,因为d_req 还一直是高电平。因此,需要把d_req_sync 信号再用两级DFF同步器,传回clk_in 时钟域,得到d_ack信号;

当clk_in 看到d_ack拉高后,就可以把d_req 信号拉低,到这里一个handshake电路行为才算是结束了

*****************clk 需要门电路做gating 的意思****************

就想当于给clk做一个enable的功能,要用的时候有clk,不用的时候就没有

DC综合简单总结(2)的更多相关文章

- DC综合简单总结(1)

DC综合简单总结(1) *****************set_dont_touch和set_dont_touch_network**************** ? 在综合的过程中,为了不让D ...

- DC综合环境的一些概念

DC综合环境的一些概念 启动文件 .synopsys_dc_setup 采用Tcl格式,包含工艺库的路径信息和其他环境变量 不同位置启动顺序 1.Synopsys安装目录 2.用户家目录 3.项目工作 ...

- DC综合及仿真验证和DFT测试

综合技术是提高设计产能的一个很重要的技术,没有综合技术的发展就不可能用HDL实现电路的设计,因为HDL开始是用来供电路仿真建模使用的,到了后来才把其中一部分子集作为可综合的语言,也就是R ...

- ASIC DC综合的理解

ASIC DC综合的理解 DC综合流程 输入设计文件+指定的工艺库文件+约束文件 经过DC的综合,输出满足期望的门级网表及综合报告 输入输出数据 输入文件:设计文件(verilog等).工艺库(db) ...

- Tcl与Design Compiler (三)——DC综合的流程

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 1.基本流程概述 首先 ...

- DC综合:划分与编码风格

划分与编码风格 合理的设计划分和好的HDL编码风格对成功的综合影响很大. 逻辑划分是成功综合(和布局布线,如果布图是层次化的)的关键. 综合划分 "分而治之" 把复杂的设计化简为更 ...

- Tcl与Design Compiler (二)——DC综合与Tcl语法结构概述

1.逻辑综合的概述 synthesis = translation + logic optimization + gate mapping . DC工作流程主要分为这三步 Translation : ...

- DC综合与Tcl语法结构概述

转载:https://www.cnblogs.com/IClearner/p/6617207.html 1.逻辑综合的概述 synthesis = translation + logic optimi ...

- DC综合流程

Design Compiler and the Design Flow 步骤 将HDL描述的设计输入到Design Compiler中 Design Compiler使用technology libr ...

随机推荐

- MySQL二进预编译制安装

+++++++++++++++++++++++++++++++++++++++++++标题:MySQL二进预编译制安装时间:2019年2月25日内容:MySQL二进制预编译安装重点:MySQL二进制预 ...

- Google SRE

SRE_百度百科 https://baike.baidu.com/item/SRE/1141123 我们离Google SRE还有多远? - 简书https://www.jianshu.com/p/6 ...

- [转帖]5G网速那么快,基站辐射会很大吗?

5G网速那么快,基站辐射会很大吗? 鲜枣课堂 2019-04-20 21:19收藏55评论6社交通讯 题图来自东方IC,本文来自微信公众号:鲜枣课堂(ID:xzclasscom),作者:小枣君 ...

- Java8新特性(一)_interface中的static方法和default方法

什么要单独写个Java8新特性,一个原因是我目前所在的公司用的是jdk8,并且框架中用了大量的Java8的新特性,如上篇文章写到的stream方法进行过滤map集合.stream方法就是接口Colle ...

- vue.js 列表追加项写法

<ul id="app"> <template v-for="site in sites"> <li>{{ site.nam ...

- Python基础:语法基础(3)

本篇主要介绍Python中一些基础语法,其中包括:标识符.关键字.常量.变量.表达式.语句.注释.模块和包等内容. 1. 标识符和关键字 1.1 标识符 标识符是变量.常量.函数.属性.类.模块和包等 ...

- 使用TCP取样器测试Socket接口

1 JMeter下载安装 下载地址:JMeter,选择Binaries下面的zip包. 检查java环境,是否安装了jdk或者jre. 解压zip包->找到bin目录下jmeter.bat文件- ...

- Python IDLE 代码高亮主题

Python IDLE 代码高亮主题 使用方法: 打开C盘我的 C:\Documents and Settings\你的用户名.idlerc文件夹 里面会有一个 config-highlight.cf ...

- 《玩转spring全家桶》学习笔记-------------丁雪丰

一.spring 课程介绍 1.初识spring 2.数据操作 3.web开发 4.spring boot 5.spring cloud 二.初识spring Spring Boot.Spring C ...

- CSS中的BFC

CSS当中BFC介绍 在前端当中,我们都知道标准文档流,我们在开发的时候,经常会碰到block和inline.而下文要说到的BFC就是对块级盒子的格式化.当然block级别的盒子是BFC,那么inli ...