STM32 Timer : Base Timer, Input Capture, PWM, Output Compare

http://www.cs.indiana.edu/~geobrown/book.pdf

An example of a basic timer is illustrated in Figure 10.1.

This timer has four components – a controller, a prescaler (PSC), an “auto-reload” register (ARR) and a counter (CNT).

The function of the prescaler is to divide a reference clock to lower frequency.

The STM32 timers have 16-bit prescaler registers and can divide the reference clock by any value 1..65535.

For example, the 24Mhz system clock of the STM32 VL Discovery

could be used to generate a 1 Mhz count frequency with a prescaler of 23 (0..23 == 24 values). T

he counter register can be configured to count up, down, or up/down and to be reloaded from the auto reload register

whenever it wraps around (an “update event”) or to stop when it wraps around.

The basic timer generates an output event (TGRO) which can be configured

to occur on an update event or when the counter is enabled (for example on a GPIO input).

To understand the three counter modes consider Figure 10.2.

In these examples, we assume a prescaler of 1 (counter clock is half the internal clock), and a auto reload value of 3.

Notice that in “Up” mode, the counter increments from 0 to 3 (ARR) and then is reset to 0.

When the reset occurs, an “update event” is generated.

This update event may be tied to TRGO, or in more complex timers with capture/compare channels

it may have additional effects (described below).

Similarly, in “Down” mode, the counter decrements from 3 to 0 and then is reset to 3 (ARR).

In Down mode, an update “event” (UEV) is generated when the counter is reset to ARR.

Finally, in Up/Down mode, the counter increments to ARR, then decrements to 0, and repeats.

A UEV is generated before each reversal with the effect that the period in Up/Down mode

is one shorter than in either Up or Down mode.

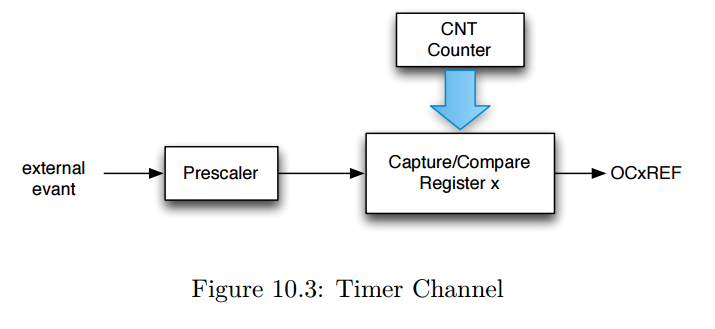

Many timers extend this basic module with the addition of counter channels such as the one illustrated in Figure 10.3.

The “x” refers to the channel number – frequently, timers support multiple channels.

With this modest additional hardware, an output can be generated whenever the count register reaches a specific value

or the counter register can be captured when a specific input event occurs (possibly a prescaled input clock).

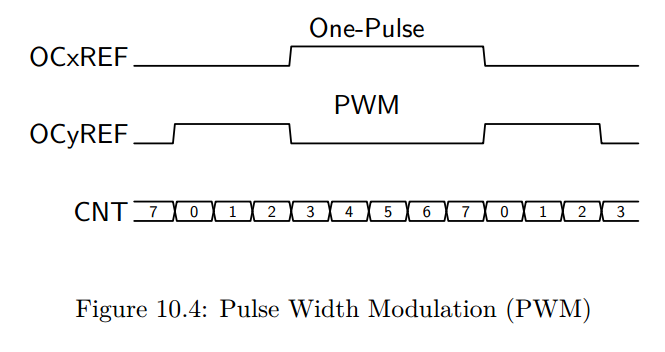

An important use of counter channels is the generation of precisely timed pulses.

There are two variations of this use – “one-pulse” pulses,

in which a single pulse is generated, and pulse width modulation, in which a series of pulses is generated with the counter UEV period.

The pulse width is controlled by the Capture/Compare Register (CCR).

For example, the channel output (OCxREF) may tied to whether the CNT register is greater (or less) than the Compare register.

In Figure 10.4 we illustrate the use of two channels for one-pulse and PWM outputs.

Here we assume that the ARR is 7 and the CCR is 3.

In PWM mode, ARR controls the period, and CCR controls the pulse width (and hence the duty cycle).

In one-pulse mode, the pulse begins CCR cycles after an initial trigger event, and has a width of ARR-CRR.

It is possible to use multiple channels to create a set of synchronized, pulses beginning at precise delays from each other.

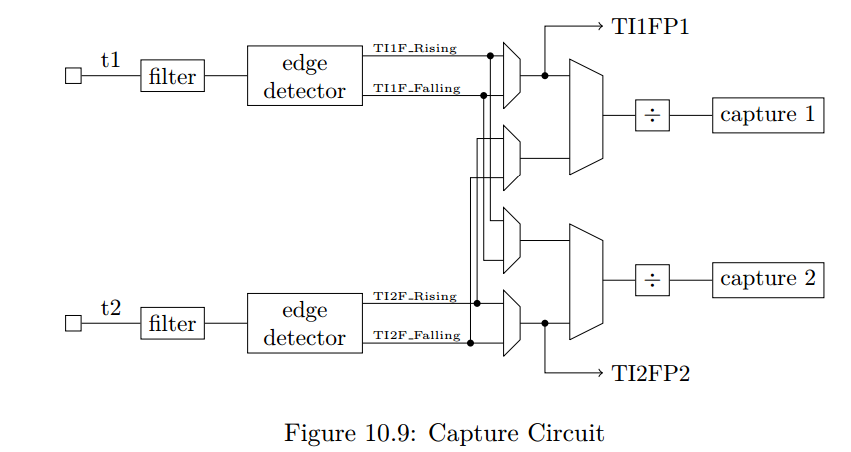

A timer channel may also be used to measure pulse widths – in effect decoding pwm signals.

There are many other configuration options for the STM32 timers including mechanisms

to synchronize multiple timers both to each other and to external signals.

In the remainder of this chapter we consider two timer applications including PWM output (Section 10.1),

input pulse measurement (Section 10.2).

In Chapter 13 we show how to use a timer to control DMA transfers for an audio player and

in Chapter 14 we use a timer to sample and analog input at regular intervals.

STM32 Timer : Base Timer, Input Capture, PWM, Output Compare的更多相关文章

- PIC32MZ tutorial -- Output Compare

Output Compare is a powerful feature of embedded world. The PIC32 Output Compare module compares the ...

- STM32 System and Timer Clock Configurations

STM32 System and Timer Clock Configurations I've started writing some software to drive a series of ...

- TIMER门控模式控制PWM输出长度

TIMER门控模式控制PWM输出长度 参照一些网友代码做了些修改,由TIM4来控制TIM2的PWM输出长度, 采用主从的门控模式,即TIM4输出高时候TIM2使能输出 //TIM2 PWM输出,由TI ...

- PIC32MZ tutorial -- Input Capture

Today I accomplish a simple application for PIC32MZ EC Starter Kit. This application uses Input Capt ...

- An Isolated DAC Using PWM Output

An Isolated DAC Using PWM Output Arduino‘s (ATmega328P) PWM outputs via analogWrite can be convenien ...

- 深入比特币原理(三)——交易的输入(input)与输出(output)

本节内容非常重要,如果你不能很好的掌握本节内容,你无法真正理解比特币的运行原理,请务必要学习清楚. 比特币的交易模型为UTXO(unspend transaction output),即只记录未花费的 ...

- Linux部署Django:报错 nohup: ignoring input and appending output to ‘nohup.out’

一.部署 Django 到远程 Linux 服务器 利用 xshell 通过 ssh 连接到 Linux服务器,常规的启动命令是 python3 manage.py runserver 但是,关闭 x ...

- STM32: TIMER门控模式控制PWM输出长度

搞了两天单脉冲没搞定,无意中发现,这个利用主从模式的门控方式来控制一路PWM的输出长度很有效. //TIM2 PWM输出,由TIM4来控制其输出与停止 //frequency_tim2:TIM2 PW ...

- STM32 Seminar 2007 -- Timer

随机推荐

- 从TFS 删除工作项

一.进入命令执行窗口的方式 1.若你的TFS服务器上安装了VS开发工作,可以按以下步骤,进入命令行方式,图如下: 2.若你TFS上没有安装VS开发工作,可以从你的开发机器上的VS安装目录下(一般情况下 ...

- Android网络框架之Retrofit + RxJava + OkHttp 变化的时代

1.什么是Retrofit框架? 它是Square公司开发的现在非常流行的网络框架,所以我们在导入它的包的时候都可以看到这个公司的名字,目前的版本是2. 特点: 性能好,处理快,使用简单,Retrof ...

- watch案例解析(element-ui el-select 无法选中问题剖析)

fire 读在最前面: 1.此文章衔接Vue 虚拟Dom 及 部分生命周期初探,相关整体知识点请先阅读后再继续本文阅读 问:子组件中明明有watch value,为什么this.$emit('inpu ...

- [图解算法] 二分查找Binary-Search——<递归与分治策略>

#include"iostream.h" int BinarySearch(int a[],int left,int right,const int& x) { if(le ...

- Windows 10安装pip方法

pip是一款非常方便的python包管理工具,本文主要介绍在windows 10下安装pip方法. 1. 下载pip 地址:https://pypi.python.org/pypi/pip#downl ...

- js如何判断访问来源是来自搜索引擎(蜘蛛人)还是直接访问

以下javascript脚本代码可以实现判断访问是否来自搜索引擎.代码如下: ? 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 <scri ...

- phpMyAdmin setup.php脚本的任意PHP代码注入漏洞

phpMyAdmin (/scripts/setup.php) PHP 注入代码 此漏洞代码在以下环境测试通过: phpMyAdmin 2.11.4, 2.11.9.3, 2.11.9.4, ...

- docker:一个支持django的dockerfile

其中,包括了主要的生产环境模块, 从alpine作起,镜像不大.保存用. FROM alpine:3.7 COPY . /target-dir WORKDIR /target-dir RUN sed ...

- 直接以管理员身份运行bat代码

https://www.cnblogs.com/dengpeng1004/p/7044441.html

- C++Primer,C++标准IO库阅读心得

IO 标准库类型和头文件 iostream istream 从流中读取 ostream 写到流中去 iostream 对流进行读写:从 istream 和 ostream 派生而来fstream if ...