verilog代码 想法验证---与寄存器输出有关

verilog代码 想法验证---与寄存器输出有关

1.

module test_mind(

input wire clk,

input wire reset,

input wire i,

output wire A,

output wire B

); reg reg_A;

always @ (posedge clk or negedge reset)

if(reset)

reg_A <= 'b0;

else if(i)

reg_A <= 'b1;

else

reg_A <= 'b0; reg reg_B;

always @ (posedge clk or negedge reset)

if(reset)

reg_B <= 'b0;

else if(reg_A)

reg_B <= 'b1;

else

reg_B <= 'b0; assign A = reg_A;

assign B = reg_B;

endmodule

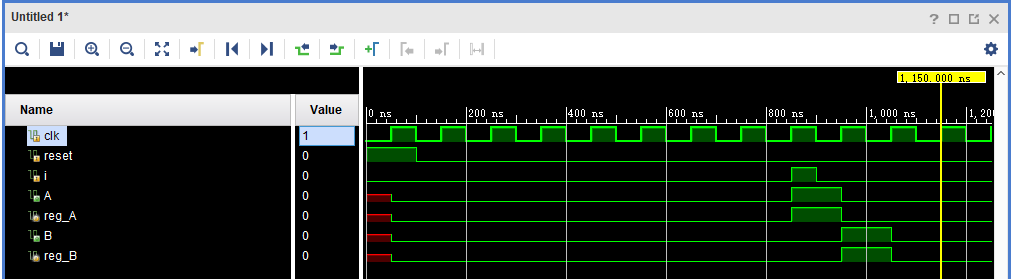

2.

add_force {/test_mind/clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex { 0ns} { 100000ps}

add_force {/test_mind/i} -radix hex { 0ns} { 850000ps} { 950000ps}

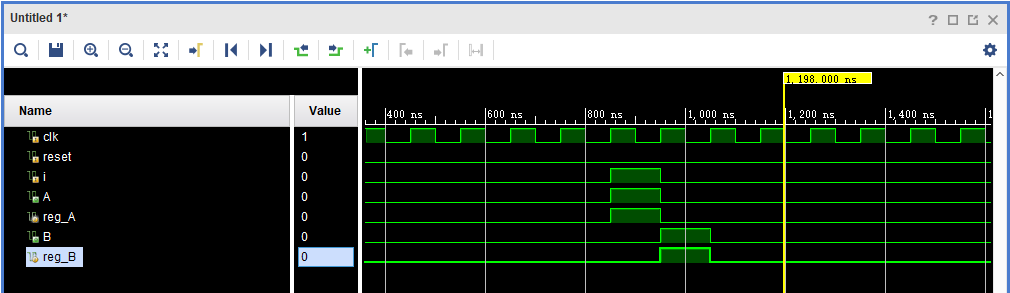

3.

4.

add_force {/test_mind/clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex { 0ns} { 100000ps}

add_force {/test_mind/i} -radix hex { 0ns} { 850000ps} { 900000ps}

5.

结论:1.第二级寄存器还是会比第一级延时一个周期

2.输入信号一点被采集到,即使在一个时钟周期内发生跳变,也不会影响寄存器的输出结果。

verilog代码 想法验证---与寄存器输出有关的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- 分享:FIFO 同步、异步以及Verilog代码实现

FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到. FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线 ...

- MVVM架构~knockoutjs系列之验证信息自定义输出

返回目录 这个文章非常重要,也是非常必要的,在我们进行项目开发时,后台无所谓,对样式无要求,而网站前台来说,对样式要求严格,你的验证信息都是前台设计好的,所以,不能使用knockoutjs自带的了,我 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- 用Sublime Text搭建简易IDE编写Verilog代码

前言 Verilog是一种硬件描述语言(HDL),该语言在Windows上有集成开发环境可以使用,如ModelSim,但ModelSim的编辑器不太好用因此笔者萌生了用Sublime Text3来编写 ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

随机推荐

- 基于NEO的私链(Private Blockchain)

1.准备工作 1.NEO-GUI 2.NEO-CLI 3..NET Core Runtime (不能是2.x版本,官方建议是1.12,实际上我用1.14也是没有问题的) 4.四台windows操作系统 ...

- [转]ZooKeeper学习第一期---Zookeeper简单介绍

ZooKeeper学习第一期---Zookeeper简单介绍 http://www.cnblogs.com/sunddenly/p/4033574.html 一.分布式协调技术 在给大家介绍ZooKe ...

- 2.4 CSS定位

前言 大部分人在使用selenium定位元素时,用的是xpath定位,因为xpath基本能解决定位的需求.css定位往往被忽略掉了,其实css定位也有它的价值,css定位更快,语法更简洁.这一篇css ...

- 全局(Global) 与本地(Local)索引的区别

一.定义说明 oracle数据库中,存在多种对象,最常见的表和索引,索引的目的是为了加快查询:oracle建议一个表>2g时,就建议进行分区,分区表的好处此处省略,分区表有维护操作,但是某些维护 ...

- jupyter环境安装

jupyter notebook环境安装 一.什么是Jupyter Notebook? 1. 简介 Jupyter Notebook是基于网页的用于交互计算的应用程序.其可被应用于全过程计算:开发.文 ...

- Twisted 安装

1,官网: https://www.twistedmatrix.com/trac/ 2,下载 https://twistedmatrix.com/Releases/Twisted/18.7/Twist ...

- XXS level1

level1 (1)查看PHP源码,发现可以通过调用window,alert()完成任务 window.alert = function() { confirm("完成的不错!") ...

- lesson2-cnn-fastai

%mkdir的做法glob('.jpg')np.random.permutation(图片)np.random.rename(,)#save_array:utils中,连接每个btch得到的数组#ke ...

- CDN是如何工作的?

CDN的原理非常简单.当浏览器请求一资源时,第一步是做DNS解析,DNS解析就像是从通讯录根据姓名找号码,浏览器发送域名,然后得到DNS服务器返回的IP地址.浏览器通过IP地址和服务器连接并获取资源( ...

- 实验吧—隐写术——WP之 SB!SB!SB!

我们先打开解题链接,里面是一张愤怒的小鸟里的小猪~ 既然这是隐写题,那么肯定要把图片下载下来进行分析咯~ 下载下来之后,我们看到题目中提示:LSB 什么是LSB? LSB(Least Signific ...