FPGA小白学习之路(2)error:buffers of the same direction cannot be placed in series

锁相环PLL默认输入前端有个IBUFG单元,在输出端有个BUFG单元,而两个BUFG(IBUFG)不能相连,所以会报这样的错:

ERROR:NgdBuild:770 - IBUFG 'u_pll0/clkin1_buf' and BUFG 'BUFG_inst' on net

'clkin_w' are lined up in series. Buffers of the same direction cannot be

placed in series.

ERROR:NgdBuild:924 - input pad net 'clkin_w' is driving non-buffer primitives:

如下示例代码:

[Demo1]

// demo1 two bufg connect

module iobuf(

input clk,

input rst,

output led

);

wire clkin_w;

BUFG BUFG_inst(

.O(clkin_w), // Clock buffer output

.I(clk) // Clock buffer input

);

pll0 u_pll0(

.CLK_IN1(clkin_w), // IN

.CLK_OUT1(clkout), // OUT

.RESET(rst)); // IN

assign led = clkout;

endmodule

普通IO不能直接做锁相环的输入,所以会报这样的错:

ERROR:Place:1397 - A clock IOB / MMCM clock component pair have been found that

are not placed at an optimal clock IOB / MMCM site pair. The clock IOB

component <clk> is placed at site <A18>. The corresponding MMCM component

<u_pll0/mmcm_adv_inst> is placed at site <MMCME2_ADV_X0Y0>. The clock IO can

use the fast path between the IOB and the MMCM if the IOB is placed on a

Clock Capable IOB site that has dedicated fast path to MMCM sites within the

same clock region. You may want to analyze why this problem exists and

correct it. If this sub optimal condition is acceptable for this design, you

may use the CLOCK_DEDICATED_ROUTE constraint in the .ucf file to demote this

message to a WARNING and allow your design to continue. However, the use of

this override is highly discouraged as it may lead to very poor timing

results. It is recommended that this error condition be corrected in the

design. A list of all the COMP.PINs used in this clock placement rule is

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

如果有ucf中加上这句约束:

NET clk CLOCK_DEDICATED_ROUTE = FALSE;

依旧会报错,在ZYNQ7000系列,这样还是通不过,如下:

ERROR:PhysDesignRules:2256 - Unsupported MMCME2_ADV configuration. The signal

u_pll0/clkin1 on the CLKIN1 pin of MMCME2_ADV comp u_pll0/mmcm_adv_inst with

COMPENSATION mode ZHOLD must be driven by a clock capable IOB.

ERROR:Pack:1642 - Errors in physical DRC.

如下示例代码

[Demo2]

// demo2 regular io directly connect to PLL

module iobuf(

input clk,

input rst,

output led

);

pll0 u_pll0(

.CLK_IN1(clk), // IN

.CLK_OUT1(clkout), // OUT

.RESET(rst)); // IN

assign led = clkout;

endmodule

使用普通的IO,再连接bufg来连到时钟线上,

仍会报这样的错误,因为还是两bufg相连了:

ERROR:NgdBuild:770 - IBUFG 'u_pll0/clkin1_buf' and BUFG 'BUFG_inst' on net

'clkin_w' are lined up in series. Buffers of the same direction cannot be

placed in series.

ERROR:NgdBuild:924 - input pad net 'clkin_w' is driving non-buffer primitives:

修改为如下:

[Demo3]

// dem3 regular io with BUFG then connect to PLL which with"No Buffer" setting

module iobuf(

input clk,

input rst,

output led

);

wire clkin_w;

BUFG BUFG_inst (

.O(clkin_w), // Clock buffer output

.I(clk) // Clock buffer input

);

pll0 u_pll0(

.CLK_IN1(clkin_w), // IN

.CLK_OUT1(clkout), // OUT

.RESET(rst)); // IN

assign led = clkout;

endmodule

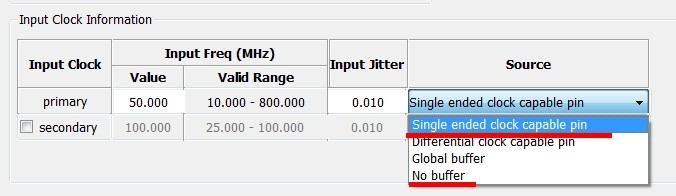

PLL的设置如下图,

这样普通IO就可以当作PLL的时钟输入了,顺利产生bit;

时钟还是最好用全局时钟IO,画图时一定要注意:)

zc702里没有global clock的概念了,但有了很多专用时钟脚,用起来一样;

[结论]

不能将两个PLL进行串联

普通IO不能直接作PLL的时钟输入,专用时钟管脚可以;

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

具体内部布局分配可以通过 Xilinx的FPGA Editor来查看,

ZYNQ的时钟管理也和之前的片子略有不同,之后在另一篇介绍,相关文档 <ug472_7Series_Clocking.pdf>

FPGA小白学习之路(2)error:buffers of the same direction cannot be placed in series的更多相关文章

- FPGA小白学习之路(5)clk为什么要用posedge,而不用negedge(转)

clk为什么要用posedge,而不用negedge 转自:http://www.cnblogs.com/dangxia/archive/2012/03/07/2383744.html Verilog ...

- FPGA小白学习之路(6)串口波特率问题的处理

串口波特率问题的处理 此博文一共包含三个方面的内容:(1)异步串口通信的数据格式:(2)为何串口通信中接收端采样时钟频率是传输的波特率的16倍:(3)串口波特率等概念. 1.异步串口通信的数据格式 串 ...

- FPGA小白学习之路(4)PLL中的locked信号解析(转)

ALTPLL中的areset,locked的使用 转自:http://www.360doc.com/content/13/0509/20/9072830_284220258.shtml 今天对PLL中 ...

- FPGA小白学习之路(1) System Verilog的概念以及与verilog的对比(转)

转自CSDN:http://blog.csdn.net/gtatcs/article/details/8970489 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证 ...

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

- USB小白学习之路(7) FPGA Communication with PC by CY7C68013,TD_init()解析

注:这个TD_Init()只对EP6进行了配置,将其配置成为Bluk_In端口,而没有对EP2进行配置.这篇文章直接把寄存器的图片贴上来了,看起来比较杂.感兴趣的可以看下一篇文章,是转自CSDN,对E ...

- Python小白学习之路(二)—【Pycharm安装与配置】【创建项目】【运算符】【数据类型】

写在前面: 第二天的学习,感觉比昨天学习相对轻松一些,但是对于我这个编程语言功底很弱的人来说,还是稍稍微有些.....哈尔滨的天气一天天冷了下来,还飘着小雨,不过还是挺有意境的.充实而又忙碌的生活,让 ...

- Python小白学习之路(二十)—【打开文件的模式二】【文件的其他操作】

打开文件的模式(二) 对于非文本文件,我们只能使用b模式,"b"表示以字节的方式操作(而所有文件也都是以字节的形式存储的,使用这种模式无需考虑文本文件的字符编码.图片文件的jgp格 ...

随机推荐

- [原]win10开机时开启NumLock

修改如下注册表项下的InitialKeyboardIndicators的值为80000002,重启即可. HKEY_USERS\.Default\Control Panel\Keyboard\ HKE ...

- [HNOI2003]操作系统 优先队列用法

题:https://www.cometoj.com/problem/1046 #include<bits/stdc++.h> using namespace std; typedef lo ...

- 001.前端开发知识,前端基础HTML(2020-01-07)

一.开发工具: chrome . sublime . photoshop 二.Web标准:不是某一个标准,而是由W3C和其他标准化组织制定的一系列标准的集合. 三.HTML的语言语法骨架格式 < ...

- 代码审计中的CSRF

0x00 背景 CSRF漏洞中文名为“跨站请求伪造”,英文别名为“one-click-attack”.从字面上我们就可以看出,这是一种劫持其他用户进行非法请求的攻击方式,主要用于越权操作,与XSS相比 ...

- ios Alamofire网络插件的使用

pod 'Alamofire' import Alamofire let headers:HTTPHeaders = [ "aa":"bb" ] let par ...

- 查看linux系统安装的服务

如何查看linux系统安装了哪些服务呢,因不同版本的操作系统可能使用的命令不一样或者有些命令在某些操作系统不可用,现列举一些常用查看命令(基于我的linux版本). 我的操作系统版本如下: 1.ser ...

- 倾斜摄影数据转cesium 3D tiles工具介绍

软件操作:http://jingyan.baidu.com/article/3aed632e3912c8701080912c.html 软件测试数据: 数据,油库链接: http://pan.baid ...

- Exchange Online合规性管理

一.就地电子数据展示和保留 就地电子数据展示允许组织内的授权合规性管理员搜索整个Exchange组织的邮箱数据.预览搜索结果,并可以复制到发现邮箱将其导出到以pst为拓展名的文件. 就地电子数据展示使 ...

- 之前工作过程中自定义的代码生成器模版,codesimit

动软代码生成器 和codesmith 5年前的东西,或许有些过时 动软的功能有限,改的也比较简单,已弃. codesmith可定制性强,当时自已改的,提高了团队的整体工作效率. codesmith代码 ...

- interrupt 停止线程

该方法只是给线程设置了一个停止的标记 并不是真正的立即停止线程 interrupted() 测试当前线程是否已经中断 isInterrupted() 测试线程是否已经中断 停止线程的方法: .异常法 ...