scan design flow(二)

在scan stitch之后,scan synthesis就已经完成,

Scan extraction主要用来从scan design中extracing所有的instance,来保证scan chain的完整性。

并保证所有的design change都整合到scan design。

Scan Verificaiton

1)在shift operate中的hold time violation,如果两个scan cell是同时钟,需要由CTS来保证clock skew有一个

minimum的值。如果clock属于异步clock,需要插入lock_up latch。

2)错误的scan initialization sequence,不能进入test mode。

3)不完整的scan design rule的check和repair,reg的set/reset以及clock的enable/gate等。

4)scan synthesis的错误,将positive放在negative之前等。

scan capture操作可能会在zero_delay和full_timing之间有mismatch。

Verifying the scan shift operate:

使用一种flush test的测试用例,用full_timing的simulator,来保证数据从scan input到scan output的时钟数相同。

为了保证clock skew也满足要求,用例使用"01100"这样的数值,包含0-0,0-1,1-0,1-1所有的场景。

为了快速定位错误的scan cell的位置,flush testbench需要有可以observe到内部scan cell的处理。

1)scan hold time violation in different clock,Lock-up latch插入。

如果一条scan chain中有多个clock,每个clock之间的latency不同,design要求,保持在半个cycle之内,

所以加入一个negative的latch可以解决这个问题。

2)scan hold time和setup time in same clock,CTS redone或者插入buffer。

3)保证所有的negative-edge都在positive-edge前边,或者加入lock-up FF。

Verify the scan Capture operate:

1)通常应用一个broadside-load的testbench,直接将整个test pattern移动到scan cell中,只包含一个clock的

shift cycle和一个clock的capture cycle。

目前也都可以通过STA的方式来进行scan shift和scan capture的verify。

Scan Design Costs:

1)area overhead cost,包括两部分,scan cell与FF的替换,以及scan routing的部分。

2)I/O pin cost,包括一个dedicate test mode pin(可以通过一个initial sequence来避免)

以及I/O的shared with function。

3)performance degradation cost,增加了functional path的delay。

4)Design effort cost,在正常flow之外还需要进行design rule checking and repair,scan synthesis,

scan extraction,scan verification。

scan design的其他purpose:

总结来看,有enhanced scan,snapshot scan,error_resilient scan,system debug,soft error protection。

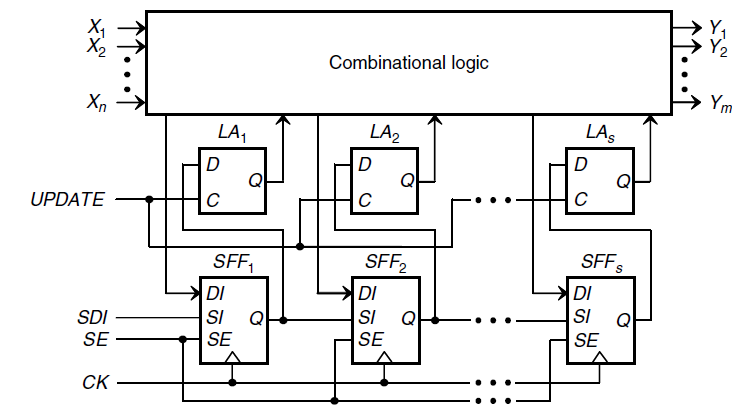

1)enhanced design,增加的delay fault detection。其中一种结构中增加一个Latch,每次锁存两bit的数据。

同时做STA时,也会增加很多false path。

2)Snapshot Scan,可以在不打断logic的functional operation的同时,capture到internal states of element。

设计通过在需要的storage element上增加scan cell来实现(不是替换),这样的设计叫做,scan set。

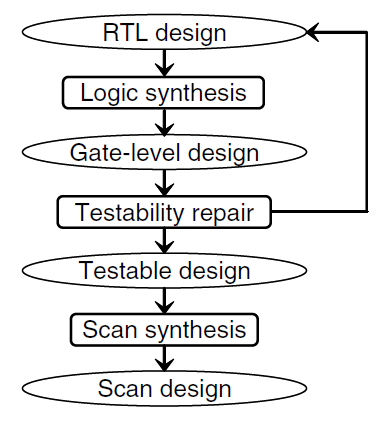

RTL DESIGN FOR TESTABILITY:

由于time-to-market的关系,越来越多的testability issues希望在RTL阶段得到fixed。

通过在netlist进行testability repair来,形成一个环路,每做一次testability repair需要进行重新DC。

scan design flow(二)的更多相关文章

- scan design flow(一)

一个典型的scan实现的flow: clock mux和一些rst,在Scan中都被bypass掉,是不能测到的.所以DFT的test coverage一般就在97%或98%. scan design ...

- Atitit vod click event design flow 视频点播系统点击事件文档

Atitit vod click event design flow 视频点播系统点击事件文档 重构规划1 Click cate1 Click mov4 重构规划 事件注册,与事件分发管理器分开 ...

- scan design rules

为了更好的设计一个scan design,一些scan design的rule必须遵循. 1)tristate bus在shift mode下必须保持bus contention: 2)bidirec ...

- Material Design入门(二)

本文主要包括以下内容 侧滑菜单DrawerLayout实现 CardView实现 DrawerLayout介绍 drawerLayout是Support Library包中实现了侧滑菜单效果的控件,可 ...

- Dynamics CRM2016 业务流程之Task Flow(二)

接上篇,Page页设置完后,按照业务流程管理也可以继续设置Insert page after branch 或者 Add branch,我这里选择后者,并设置了条件,如果Pipeline Phase ...

- Material Design (二),TextInputLayout的使用

前言 一般登录注冊界面都须要EditText这个控件来让用户输入信息,同一时候我们通常会设置一个标签(使用TextView)和EditText的hint属性来提示用户输入的内容,而设计库中高级组件T ...

- FPGA design flow

FPGA engineering process usually involves the following stages: Architecture design. This stage invo ...

- SystemVerilog for design 笔记(二)

转载请标明出处 1. System Verilog文本值和数据类型 1.1. 增强的文本值赋值 相对于verilog,SV在文本值赋值时可以1.无需指定进制 2.赋值可以是逻辑1 用法: reg ...

- flutter学习之二Material Design设计规范

前言: 最近在自学flutter跨平台开发,从学习的过程来看真心感觉不是那么一件特别容易的事.不但要了解语法规则, 还要知晓常用控件,和一些扩展性的外延知识,所以套一句古人的话“路漫漫其修远矣,无将上 ...

随机推荐

- php--求几个数中的最小值

<?phpecho min(2, 3, 1, 6, 7); // 1echo min(array(2, 4, 5)); // 2echo min(0, 'hello'); // 0ec ...

- threading多线程

什么是线程? 线程是操作系统能够进行运算调度的最小单位.它被包含在进程之中,是进程中的实际运作单位.一条线程指的是进程中一个单一顺序的控制流,一个进程中可以并发多个线程,每条线程并行执行不同的任务.一 ...

- ligerui ligerTip气泡提示信息

onAfterShowData:function(){ $('.l-grid-row-cell-inner').hover(function (){ $(this).ligerTip({content ...

- ACCESS自动编号重新从1开始

方法一: 删掉自动编号的字段,再建一个同样的自动编号字段. 方法二: 选择工具,再选择数据库实用工具,单击压缩和修复数据库,这样就OK了. 方法三:(提示错误“无效的数据字段类型” 尝试失败) ...

- HBASE架构解析(二)

http://www.blogjava.net/DLevin/archive/2015/08/22/426950.html HBase读的实现 通过前文的描述,我们知道在HBase写时,相同Cell( ...

- Interview How to Count Squares

火柴拼出多少个正方形 http://matchstickpuzzles.blogspot.com/2011/06/55-4x4-square-how-many-squares.html 输入是两个二维 ...

- Linux内核socket优化项

Linux内核socket优化项 vi /etc/sysctl.confnet.core.netdev_max_backlog = 30000 每个网络接口接收数据包的速率比内核处理这些包的速率快时 ...

- saltstack之(六)配置管理state

配置管理是saltstack工具最重要的模块之一,也是学习saltstack之后使用最多的一个功能.可以轻松实现上百台上千台甚至上万台服务器的管理工作. 1.使用state模块进行配置管理,编写sls ...

- Java控制语句——switch语句

上述if语句的等值判断,可以用switch来代替. 注意每个case后面一般要添加break,表示当前这个case执行完了:防止出现case穿透,即继续执行case,直到遇到break才跳出. 下面例 ...

- string函数分析

string函数分析string函数包含在string.c文件中,经常被C文件使用.1. strcpy函数原型: char* strcpy(char* str1,char* str2);函数功能: 把 ...