基于Verilog的串口接收程序

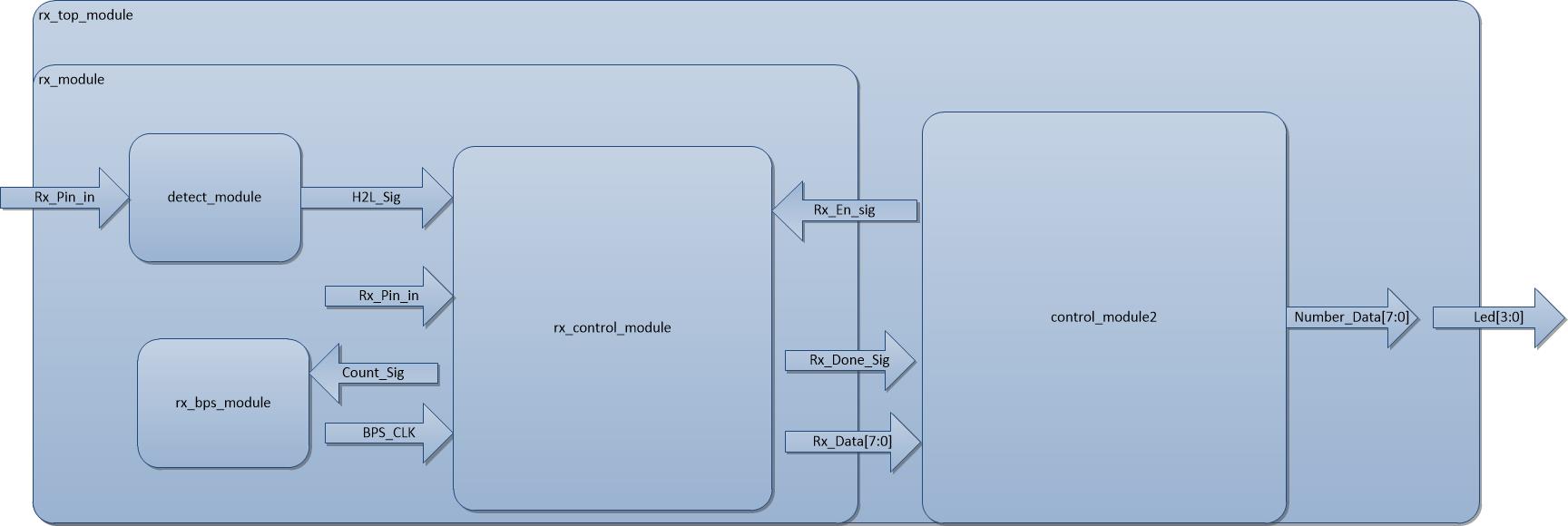

一、模块框图及基本思路

detect_module:检测输入引脚的下降沿,以此判断一帧数据的开始

rx_bps_module:波特率时钟产生模块

rx_control_module:串口接收的核心控制模块

rx_module:前三个模块的组合

control_module2:接受控制模块,不断接收串口数据

rx_top_module:将接收到数据的第四位以LED的形式显示

二、软件部分

detect_module:

module detect_module(

CLK,RSTn,

RX_Pin_in,

H2L_Sig

);

input CLK,RSTn;

input RX_Pin_in;

output H2L_Sig; /**********************************/

reg RX_r1;

reg RX_r2; always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

RX_r1<='b1;

RX_r2<='b1;

end

else

begin

RX_r1<=RX_Pin_in;

RX_r2<=RX_r1;

end

end

/*********************************/ assign H2L_Sig=RX_r2&(!RX_r1); endmodule

rx_bps_module:

module rx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

rx_control_module:

module rx_control_module(

CLK,RSTn,

H2L_Sig,BPS_CLK,RX_Pin_in,

Count_Sig,RX_En_Sig,RX_Done_Sig,RX_Data

); input CLK,RSTn;

input H2L_Sig,BPS_CLK,RX_En_Sig,RX_Pin_in;

output Count_Sig,RX_Done_Sig;

output [:] RX_Data; reg[:] i;

reg isCount;

reg isDone;

reg [:] rData;

/********************************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

i<='d0;

isCount<='b0;

isDone<='b0;

rData<='d0;

end

else if(RX_En_Sig)

begin

case(i)

'd0:if(H2L_Sig) begin i<=i+1'b1;isCount<='b1; end //接收到下降沿开始启动波特率计数

'd1:if(BPS_CLK) begin i<=i+1'b1; end //起始位

'd2,4'd3,'d4,4'd5,'d6,4'd7,'d8,4'd9:

if(BPS_CLK) begin rData[i-]<=RX_Pin_in;i<=i+'b1;end //数据位

'd10:if(BPS_CLK) begin i<=i+1'b1; end //校验位

'd11:if(BPS_CLK) begin i<=i+1'b1; end //停止位

'd12:if(BPS_CLK) begin i<=i+1'b1;isDone<='b1;isCount<=1'b0; end //一个时钟脉冲的 isDone 信号

'd13:begin i<=1'b0;isDone<='b0; end

endcase

end end /********************************************/

assign Count_Sig=isCount;

assign RX_Done_Sig=isDone;

assign RX_Data=rData; endmodule

rx_module:

module rx_module(

CLK,RSTn,

RX_Pin_in,RX_Done_Sig,RX_Data,RX_En_Sig

); input CLK,RSTn;

input RX_Pin_in,RX_En_Sig;

output RX_Done_Sig;

output [:] RX_Data; wire Count_Sig;

wire BPS_CLK;

wire H2L_Sig; rx_bps_module U0(

.CLK(CLK),.RSTn(RSTn),

.Count_Sig(Count_Sig),

.BPS_CLK(BPS_CLK)

); detect_module U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.H2L_Sig(H2L_Sig)

); rx_control_module U2(

.CLK(CLK),.RSTn(RSTn),

.H2L_Sig(H2L_Sig),.BPS_CLK(BPS_CLK),.RX_Pin_in(RX_Pin_in),

.Count_Sig(Count_Sig),.RX_En_Sig(RX_En_Sig),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data)

); endmodule

control_module2:

module control_module2(

CLK,RSTn,

RX_Done_Sig,

RX_En_Sig,

RX_Data,

Number_Data

); input CLK;

input RSTn;

input RX_Done_Sig;

input [:]RX_Data;

output RX_En_Sig;

output [:] Number_Data; /***************************************/

reg[:] rData;

reg rEn;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rData<='d0;

rEn<='b0;

end

else if(RX_Done_Sig)

begin

rEn<='b0;

rData<=RX_Data;

end

else rEn<='b1;

end

/***************************************/

assign Number_Data=rData;

assign RX_En_Sig=rEn; endmodule

rx_top_module:

module rx_top_module(

CLK,RSTn,

RX_Pin_in,Led

);

input CLK,RSTn;

input RX_Pin_in;

output [:]Led; wire RX_Done_Sig;

wire RX_En_Sig;

wire [:] Number_Data;

wire [:] RX_Data; rx_module U0(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data),.RX_En_Sig(RX_En_Sig)

); control_module2 U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Done_Sig(RX_Done_Sig),

.RX_En_Sig(RX_En_Sig),

.RX_Data(RX_Data),

.Number_Data(Number_Data)

); assign Led=Number_Data[:];

endmodule

三、硬件部分

黑金SPARTAN-6开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "RX_Pin_in" LOC = C11;

NET "Led[0]" LOC = P4;

NET "Led[1]" LOC = N5;

NET "Led[2]" LOC = P5;

NET "Led[3]" LOC = M6;

基于Verilog的串口接收程序的更多相关文章

- 基于Verilog的串口发送程序

一.模块框图及基本思路 tx_bps_module:波特率时钟产生模块 tx_control_module:串口发送的核心控制模块 tx_module:前两个模块的组合 control_module: ...

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- Qt编写串口通信程序全程图文解说

(说明:我们的编程环境是windows xp下,在Qt Creator中进行,假设在Linux下或直接用源代码编写,程序稍有不同,请自己修改.) 在Qt中并没有特定的串口控制类,如今大部分人使用的是第 ...

- 转:Qt编写串口通信程序全程图文讲解

转载:http://blog.csdn.net/yafeilinux/article/details/4717706 作者:yafeilinux (说明:我们的编程环境是windows xp下,在Q ...

- Qt编写串口通信程序全程图文讲解 .

在Qt中并没有特定的串口控制类,现在大部分人使用的是第三方写的qextserialport类,我们这里也是使用的该类.我们可以去 http://sourceforge.net/projects/qex ...

- 【转】Qt编写串口通信程序全程图文讲解

本文章原创于www.yafeilinux.com 转载请注明出处. (说明:我们的编程环境是windows xp下,在Qt Creator中进行,如果在Linux下或直接用源码编写,程序稍有不同,请自 ...

- C#中缓存的使用 ajax请求基于restFul的WebApi(post、get、delete、put) 让 .NET 更方便的导入导出 Excel .net core api +swagger(一个简单的入门demo 使用codefirst+mysql) C# 位运算详解 c# 交错数组 c# 数组协变 C# 添加Excel表单控件(Form Controls) C#串口通信程序

C#中缓存的使用 缓存的概念及优缺点在这里就不多做介绍,主要介绍一下使用的方法. 1.在ASP.NET中页面缓存的使用方法简单,只需要在aspx页的顶部加上一句声明即可: <%@ Outp ...

- 018_STM32程序移植之_串口接收中文

(一)在平时数据传输中很少用到接收中文的情况,但是最近需要用到就花了半天时间来弄弄 (二)接收原理,从现在接收情况分析:一个中文占两个数据的空间,也就是两个十六进制可以转化成为一个中文 (三)示例情况 ...

随机推荐

- 基于ABP模块组件与依赖注入组件的项目插件开发

注意,阅读本文,需要先阅读以下两篇文章,并且对依赖注入有一定的基础. 模块系统:http://www.cnblogs.com/mienreal/p/4537522.html 依赖注入:http://w ...

- js 计算后样式封装

function getStyle(obj,attr){ // 需要获取的元素 属性 if(obj.currentStyle){ return obj.currentStyle[attr]; }els ...

- flask的简单使用

一.Flask中的CBV from flask import Flask, render_template from flask import views app = Flask(__name__, ...

- php 把一个数组分成几个数组

<?php /* * * 把一个数组分成几个数组 * $arr 数组 * $num 获取的数量 * */ function sliceArr($arr, $num) { //数组的个数 $lis ...

- rangeOfString 和 containsString 兼容iOS7处理

//查找字符串是否包含"心" NSString *str = @"每天都有好心情"; if ([str containsString:@"心" ...

- Python爬虫(一)——开封市58同城租房信息

代码: # coding=utf-8 import sys import csv import requests from bs4 import BeautifulSoup reload(sys) s ...

- 02: OpenStack

1.1 OpenStack各组件 1.Horizon(控制台),又名Dashboard 就是web展示界面操作平台,方便用户交互的 2.Nova(计算) 负责创建,调度,销毁云主机 3.Neutron ...

- vc++2010如何新建项目并在控制台打印helloworld

关于写c++使用什么集成开发环境的问题其实挺纠结的.我找了好久找到codeblocks,发现这款IDE还是最适合用在最标准的c++语法环境中.其实先前装过vs2015旗舰版,但是这款软件太大了,非常消 ...

- Redis setnx命令 分布式缓存

setnx命令 将 key 的值设为 value,当且仅当 key 不存在. 若给定的 key 已经存在,则 SETNX 不做任何动作. SETNX 是SET if Not eXists的简写. re ...

- esay-ui学习笔记(一)

JavaScript prototype用法 prototype 属性使您有能力向对象添加属性和方法. object.prototype.name=value <script type=&quo ...