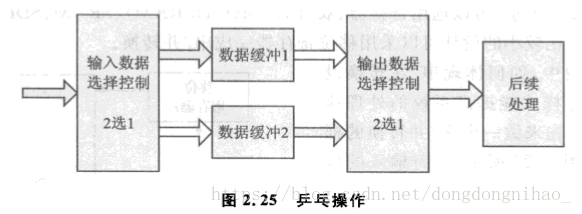

FPGA之乒乓操作

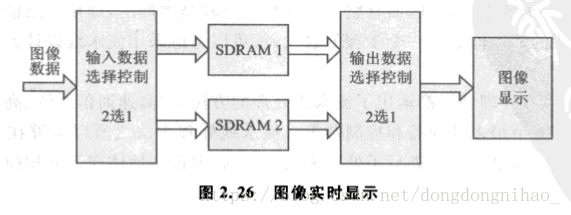

比如将乒乓操作运用在液晶显示的控制模块上,如图所示。

module pingpang

(

input clk ,

input rst_n ,

input [:] data_in , // 输入数据

output reg [:] data_out // 输出数据

); // ------------------------------------------------------ //

reg [:] buffer1 ; // 缓存1

reg [:] buffer2 ; // 缓存2

reg wr_flag ; // 写标志,wr_flag=0,写buffer1,wr_flag=1,写buffer2

reg rd_flag ; // 读标志,rd_flag=0,读buffer2,rd_flag=1,读buffer1

reg state ; // 状态机,0:写1读2,1:写2读1,状态转移和输出分开编码

// ------------------------------------------------------ //

// 状态转移

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

state <= 'b0;

end

else

begin

state <= !state;

//case(state)

// 1'b0 : state <= 1'b0; // 写1读2->写2读1

// 1'b1 : state <= 1'b1; // 写2读1->写1读2

// default : state <= 1'b0;

//endcase

end

end

// ------------------------------------------------------ //

// 状态输出

always @ (state)

begin

case(state)

'b0:

begin

wr_flag = 'b0; // 写1

rd_flag = 'b0; // 读2

end

'b1:

begin

wr_flag = 'b1; // 写2

rd_flag = 'b1; // 读1

end

default:

begin

wr_flag = 'b0;

rd_flag = 'b0;

end

endcase

end

// ------------------------------------------------------ //

// 写buffer数据

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

buffer1 <= 'b0;

buffer2 <= 'b0;

end

else

begin

case(wr_flag)

'b0 : buffer1 <= data_in; // wr_flag = 0,写buffer1

'b1 : buffer2 <= data_in; // wr_flag = 1,写buffer2

default :

begin

buffer1 <= 'b0;

buffer2 <= 'b0;

end

endcase

end

end

// ------------------------------------------------------ //

// 读buffer数据

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

data_out <= 'b0;

end

else

begin

case(rd_flag)

'b0 : data_out <= buffer2; // rd_flag=0,读buffer2

'b1 : data_out <= buffer1; // rd_flag=1,读buffer1

default : data_out <= 'b0;

endcase

end

end

// ------------------------------------------------------ //

endmodule

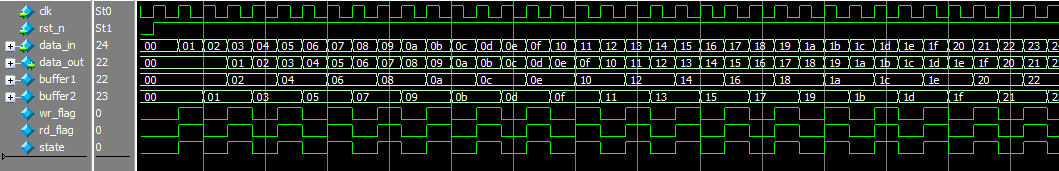

2.2 FPGA仿真代码

`timescale 1ns / 1ps

module pingpang_tb();

reg clk ;

reg rst_n ;

reg [:] data_in ;

wire[:] data_out;

always # clk = ~clk;

initial

begin

rst_n <= 'b0 ;

clk <= 'b0 ;

#;

rst_n <= 'b1 ;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data_in <= 'd0;

else

data_in <= data_in + 'b1;

end

pingpang dut

(

.clk (clk ),

.rst_n (rst_n ),

.data_in (data_in ),

.data_out (data_out )

);

endmodule

3.仿真结果

FPGA之乒乓操作的更多相关文章

- 【FPGA技巧篇一】FPGA设计的四种常用思想与技巧之一 :乒乓操作

本文篇章将讨论一下的四种常用 FPGA 设计思想与技巧: 乒乓操作. 串并转换. 流水线操作. 数据接口同步化, 都是 FPGA 逻辑设计的内在规律的体现, 合理地采用这些设计思想能在FPGA设计工作 ...

- FPGA SD 卡 之 乒乓操作 、同步fifo

这里记录一个实际的需要使用乒乓操作的例子:读sd卡数据的时,在spi的模式下.发送单数据块的读取命令,在回应之后会有 512字节的数据.使用乒乓操作,可以用两个八位的寄存器,就可以完成连续的512字节 ...

- sdram之乒乓操作

在实时显示时,为了保证画面显示的完整性需要对SDRAM进行乒乓操作. SDRAM 中有 4 个bank ,地址分别为00 01 10 11,后面将用 0 1 2 3来描述 bank 0和1 作为第一个 ...

- DMA缓冲区乒乓操作的处理

http://www.51hei.com/bbs/dpj-141761-1.html https://blog.csdn.net/sunnydreamrain/article/details/8288 ...

- FPGA重要设计思想

FPGA重要设计思想 1.速度和面积互换原则.以面积换速度可以实现很高的数据吞吐率,其实串/并转换.就是一种以面积换速度的思想 2.乒乓操作. 3.串/并转换的思想. 高速数据处理的重要技巧之一. ...

- [华清远见]FPGA公益培训

本套视频教程为华清远见 网络公益培训活动,主讲人:姚远老师,华清远见高级讲师. ------------------------------------------------------------ ...

- 【转】 FPGA设计的四种常用思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

- CPLD VS FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL.GAL.CPLD等可编程器件的基础上进一步发展的产物.它是作为专用集成电路(ASIC)领域中的 ...

- FPGA/CPLD设计思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

随机推荐

- es6 set简析

1.数据结构Set类似于数组,但是成员的值都是唯一的,没有重复的值. var s = new Set(); [,,,,,,].map(x => s.add(x)) for (i of s) {d ...

- ViewPager封装工具类: 轻松实现APP导航或APP中的广告栏

相信做app应用开发的,绝对都接触过ViewPager,毕竟ViewPager的应用可以说无处不在:APP第一次启动时的新手导航页,APP中结合Fragment实现页面滑动,APP中常见的广告栏的自动 ...

- Project Euler Problem 26-Reciprocal cycles

看样子,51nod 1035 最长的循环节 这道题应该是从pe搬过去的. 详解见论文的(二)那部分:http://web.math.sinica.edu.tw/math_media/d253/2531 ...

- @hdu - 6427@ Problem B. Beads

目录 @description@ @solution@ @accepted code@ @details@ @description@ 有 m 种不同颜色的珠子,颜色分别为 1~m,每一种颜色的珠子有 ...

- 使用基于Apache Spark的随机森林方法预测贷款风险

使用基于Apache Spark的随机森林方法预测贷款风险 原文:Predicting Loan Credit Risk using Apache Spark Machine Learning R ...

- hdu 1556 Color the ball(区间更新,单点求值)

Color the ball Time Limit: 9000/3000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)To ...

- Vue 路由的嵌套使用

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- Python--day41--threading中的定时器Timer

定时器Timer:定时开启线程 代码示例: #定时开启线程 import time from threading import Timer def func(): print('时间同步') #1-3 ...

- Linux 内核中的数据类型

在我们进入更高级主题之前, 我们需要停下来快速关注一下可移植性问题. 现代版本的 Linux 内核是 高度可移植的, 它正运行在很多不同体系上. 由于 Linux 内核的多平台特性, 打算做认真使用的 ...

- linux下mysql5.7忘记root密码修改

朋友最近开始学服务器,mysql密码忘了又不会弄,让我帮忙解决一下.重置或修改mysql的root密码这种事平时很少做,还是得google辅助一下,于是弄完了写篇博客记录一下,方便若干月后又有人遇到这 ...