69.Spartan-6的SelectIO资源

2.1.6 SelectIO资源

Spartan-6有丰富的I/O资源,包括SelectIO和RocketIO。

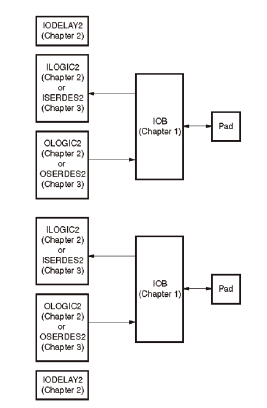

Spartan-6每个I/O片(Tile)包含两个IOB、两个ILOGIC2、两个OLOGIC2和两个IODELAY2,见图2-37。

在这一小节里,分以下几个方面介绍Spartan-6的SelectIO资源。

- SelectIO的电气特性。

- SelectIO的逻辑资源(ILOGIC2、OLOGIC2)。

- SelectIO的高级逻辑资源(ISERDES、OSERDES、Bitslip)。

图2-37 I/O片结构图

一、 SelectIO IOB的电气特性

所有的Spartan-6 FPGA有高性能的可配置SelectIO驱动器与接收器,支持非常广泛的接口标准。可以通过编程控制I/O的输出强度、斜率以及片上终端OCT。

每个IOB包含输入、输出和三态SelectIO驱动器。这些驱动器可以按照各种I/O标准配置。

- 单端I/O标准(LVCMOS、LVTTL、HSTL、SSTL、PCI)。

- 差分I/O标准(LVDS、RSDS、TMDS、差分HSTL和SSTL)。

注意:差分输入和VREF相关输入是由VCCAUX供电。

Xilinx软件库提供了很多Spartan-6 I/O的原语,包括用于单端信号的IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器);以及用于差分信号的IBUFDS(输入缓冲器)、IBUFGDS(时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)和IOBUFDS(输入/输出缓冲器)。

二、 SelectIO的逻辑资源

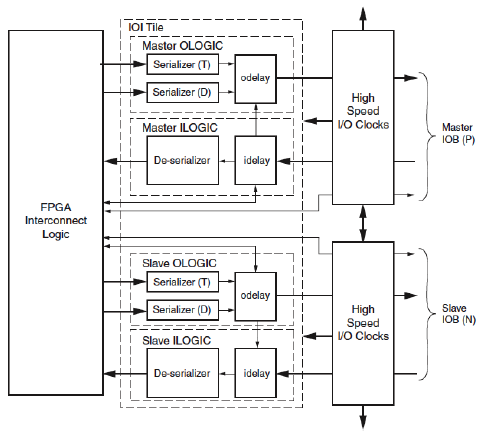

SelectIO的逻辑资源是指I/O驱动器与接收器之后的逻辑,包含了Spartan-6 FPGA的所有基本I/O逻辑资源,如图2-38所示。其中包括的资源如下。

- 组合输入/输出。

- 三态输出控制。

- 寄存器输入/输出。

- 寄存器三态输出控制。

- 双倍数据速率(DDR)输入/输出。

- DDR输出三态控制。

- IODELAY2提供对高分辨率可调延迟单元的控制。

- 支持NONE、C0和C1三种对齐模式的DDR输出。

- 支持NONE、C0和C1三种对齐模式的DDR输入。

- ISERDES。

- OSERDES。

图2-38 I/O片内的SelectIO逻辑资源

一个I/O片(IOI)管理两个IOB。IOI包含两个单端输入/输出,或者一个差分输入/输出的完整电路和一个内部互联模块。两个IOB组合在一起是为支持高速的差分接口。

在单端模式下,主IOB驱动引脚P,从IOB驱动引脚N。在差分模式下,主从IOB组合在一起可以实现串并转换,其数据速率是单端模式下的1~2倍。每个I/O支持3种配置模式:锁存型I/O、非锁型I/O和寄存器型I/O。I/O还可以配置为2:1/3:1/4:1的SERDES。锁存/寄存器时钟来自GCLK驱动的全局时钟网络或者高速I/O时钟网络。

IODELAY2是一种可选资源,设计者可以根据需要在输入/输出路径上加入此延时模块,IODELAY2的延时是可编程的,可以通过DRP指定或者通过例化IODELAY2原语指定。此延时可以是固定延时,也可以是可变延时。

三、 ILOGIC2资源

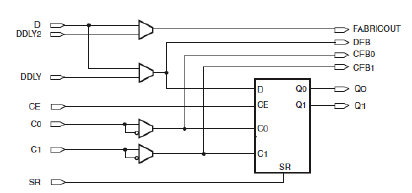

图2-39所示为ILOGIC2逻辑框图,它可支持以下功能。

- 边沿触发D型触发器。

- IDDR(NONE、C0或C1)模式。

- 锁存器。

- 异步/组合逻辑。

图2-39 ILOGIC2逻辑框图

(1) 异步/组合逻辑。

当有下列情况之一时,软件会自动生成组合通路,使输入驱动器与FPGA内部逻辑资源直接连接。

- FPGA的输入数据与内部逻辑直接相连,而没有用寄存器。

- “打包I/O寄存器/锁存器到IOB中”的属性设置为OFF。

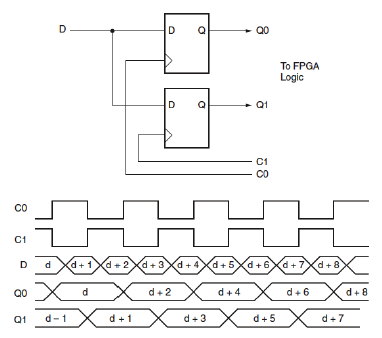

(2) IDDR模式。

Spartan-6器件的ILOGIC2中有专用寄存器来实现输入双倍数据速率(DDR)寄存器。可以通过例化IDDR2的原语来使用此功能。

IDDR2的属性DDR_ALIGNMENT有3种模式:NONE、C0和C1。

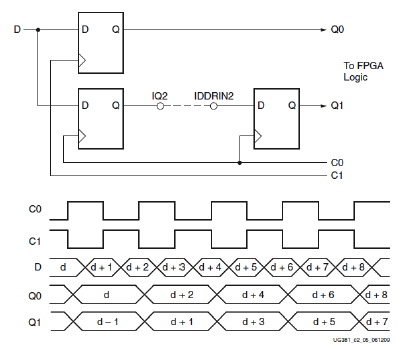

在NONE模式下,输入DDR时序如图2-40所示。寄存器在C0上升沿将输入数据D寄存到Q0,C1上升沿将下一输入数据D寄存到Q1。

图2-40 DDR_ALIGNMENT=NONE时输入DDR时序示意图

在某些情况下,输入数据必须同步到一个时钟域里,通常C0同步。但是在频率比较高的情况下,这种同步相对比较困难,因为有效时间仅为时钟周期的一半(50%占空比的情况下)。Spartan-6器件中的IDDR2包含了专用的逻辑,可以在ILOGIC2内部进行时钟域的同步。

当DDR_ALIGNMENT为C0(或C1),信号Q0(Q1)在C1(C0)再次寄存,通过内部互联将输入数据同步到同一时钟域。时序图如图2-41所示。

图2-41 DDR_ALIGNMENT=C0\C1 的输入DDR

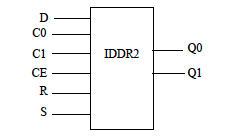

IDDR 的原语如图2-42 所示。

图2-42 IDDR2 的原语

四、 OLOGIC2 资源

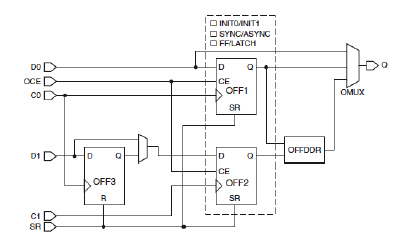

如图2-43所示,OLOGIC2主要由两部分组成,分别是输出数据路径和三态控制路径。

这两个部分可以配置成以下模式。

- 边沿触发D 型触发器。

- DDR 模式(NONE、C0 或C1 同步方式)。

- 电平敏感锁存器。

- 异步/组合逻辑。

图2-43 OLOGIC2 逻辑模块

(1) 组合数据输出和三态控制路径。

当有下列情况之一时,软件会自动生成组合通路,将FPGA 内部数据直接输出到输出驱动器或驱动器的控制端。

- FPGA 内部逻辑数据直接输出到输出驱动器或驱动器的三态控制端,而没有经过寄存器。

- “打包I/O 寄存器/锁存器到IOB 中”的属性设置为OFF。

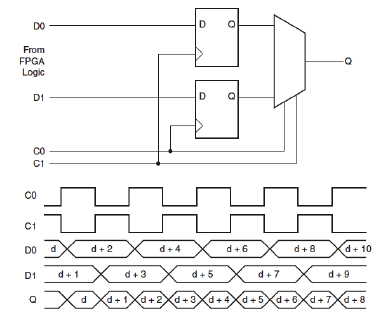

(2) ODDR模式。

Spartan-6器件的OLOGIC2中具有专用寄存器,用来实现DDR输出寄存器。例化ODDR2原语可以使用此功能。当使用OLOGIC2时,会自动使用多路复用器,多路复用器的控制端产生于时钟信号,不需要手动控制。ODDR2 有两个时钟输入,相位差180°。

ODDR2 支持以下操作模式。

- NONE 模式:允许设计人员在C0 和C1 时钟的上升沿将两个数据通过DDR多路复用器送至输出引脚,如图2-44所示。

图2-44 DDR_ALIGNMENT=NONE 下的ODDR2

- C0模式:在时钟C0上升沿时,将两个数据通过DDR多路复用器送至输出引脚。

- C1模式:在时钟C1上升沿时,将两个数据通过DDR多路复用器送至输出引脚。

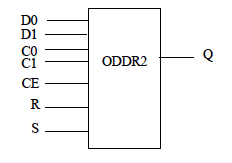

ODDR原语如图2-45所示。

图2-45 ODDR原语

五、 可编程延迟单元IODELAY2

每个IOB包含一个延时单元,可以配置成输入延时或者输出延时,当引脚用作双向口时,还可以通过T端来控制输入/输出延时的切换。Spartan-6中IODELAY2的延时不会自动补偿温度或电压带来的延时差异,但是用户可以通过精确计算,来设置IODELAY2的具体延时值。

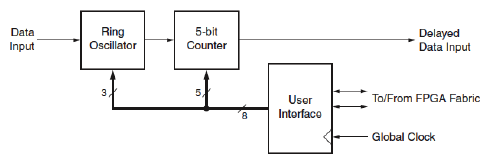

图2-46所示为延时单元的结构图。8位延时值对应0~255个延时Tap,该延时值最低三位控制RING晶振的起始点。该晶振由输入信号触发,经过0~7个Tap的延时之后,其输出作为时钟,用来钟控5位计数器。5位计数器中装载了延时值的高5位,它会一直在0~31循环,直到它的输出翻转到最初输入到该模块时的输入值Data Input。延时精度范围为1~255TAP。

图2-46 延时单元的结构图

此延时单元有两个局限,第一,延时最大值为1个位周期,超过此限制,接收数据会出错;第二,在下一个边沿到来之前,必须完成对第一个边沿的处理,这种情况会发生在接收高速数据流时。

如何避免上述两个局限呢?

对于第一个限制,通过确保延时值小于一个输入数据的位周期(1UI)就可以避免,通常设置为0.5UI,使数据采样点位于眼图的中心。

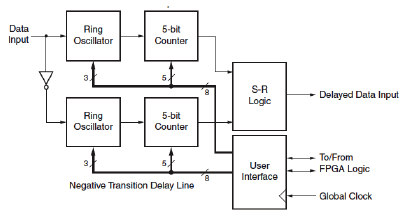

对于第二个限制,可以通过图2-47所示的两个延时链解决。一个延迟链延时输入数据的正值部分,另一个延时链延时输入数据的负值部分,这个处理机制的价值在于:通过设置两个延迟链的不同延时值,校正了输入数据的占空比。读者可以在设计中调用IODRP2原语使用此功能。

图2-47 每个延时模块使用两个延时链

六、 SelectIO的高级特性

除了上述SelectIO资源之外,Spartan-6还提供了更高级的逻辑特性,介绍如下。

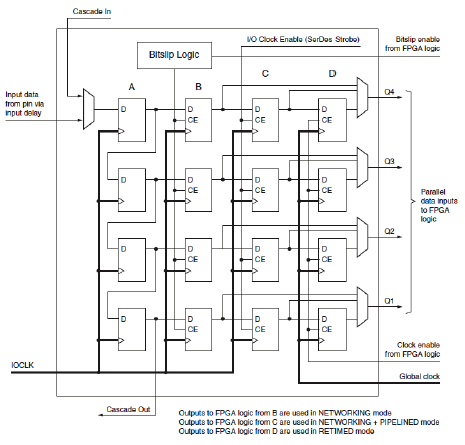

(1) 串并转换器ISERDES2。

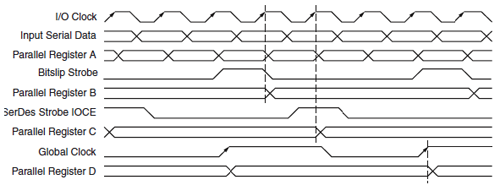

图2-48和图2-49分别为ISERDES2接收串行数据时的逻辑框图和时序图,利用ISERDES2将串行数据接收为4位并行数据。从时序图中可以看到,Bitslip为4位数据的同步使能控制信号。

图2-48 ISERDES2逻辑框图

图2-49 ISERDES2时序图(1:4)

ISERDES2可以实现1:2、1:3或1:4串并转换器功能,而且通过级联的方式还可以实现1:5、1:6、1:7、1:8串并转换器功能。

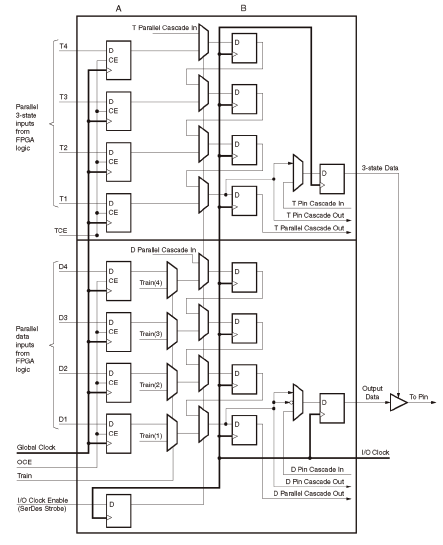

(2) 并串转换器OSERDES2。

图2-50与图2-51分别为OSERDES2的逻辑框图和时序图,利用OSERDES2将4位并行数据转换为串行数据输出。

一个OSERDES2可以实现2:1、3:1、4:1并口转换功能。当用差分输出时,相关的2个IOB中的OSERDES2可以级联,从而可以实现5:1、6:1、7:1和8:1并串转换功能。设计者可以在HDL设计中,例化ISERDES2/OSERDES2原语来实现输入数据解串和输出数据串行化操作。

利用这些资源,可以很方便地实现高速串行数据的收发,例如用它实现LVDS接口。

更多资料请参考附带光盘中的《Spartan-6 IO资源用户手册》。

图2-50 OSERDES2逻辑框图

图2-51 OSERDES2时序图(4:1)

69.Spartan-6的SelectIO资源的更多相关文章

- Xilinx FPGA LVDS应用

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用.Xilinx FPGA中,主要通过原语实现差分信号的收发:OBUFDS(差分输出BUF),IBUFDS(差分输入BUF). 注意在分 ...

- 2013年第四届蓝桥杯javaB组 试题 答案 解析

1.世纪末的星期 曾有邪教称1999年12月31日是世界末日.当然该谣言已经不攻自破. 还有人称今后的某个世纪末的12月31日,如果是星期一则会.... 有趣的是,任何一个世纪末的年份的12月31日都 ...

- 【进阶修炼】——改善C#程序质量(4)

46, 显示释放资源,需要实现IDisposable接口. 最好按照微软建议的Dispose模式实现.实现了IDisposable接口后,在Using代码块中,垃圾会得到自动清理. 47, 即使提供了 ...

- 算法笔记_109:第四届蓝桥杯软件类省赛真题(JAVA软件开发本科B组部分习题)试题解答

目录 1 马虎的算式 2 黄金连分数 3 有理数类 4 幸运数 5 连号区间数 前言:以下试题解答代码部分仅供参考,若有不当之处,还请路过的同学提醒一下~ 1 马虎的算式 标题: 马虎的算式 小明 ...

- 第四届蓝桥杯JavaB组省赛真题

解题代码部分来自网友,如果有不对的地方,欢迎各位大佬评论 题目1.世纪末星期 题目描述 曾有邪教称1999年12月31日是世界末日.当然该谣言已经不攻自破. 还有人称今后的某个世纪末的12月31日,如 ...

- java实现第四届蓝桥杯幸运数

幸运数 题目描述 幸运数是波兰数学家乌拉姆命名的.它采用与生成素数类似的"筛法"生成. 首先从1开始写出自然数1,2,3,4,5,6,- 1 就是第一个幸运数. 我们从2这个数开始 ...

- 编写高质量代码改善C#程序的157个建议——建议69:应使用finally避免资源泄漏

建议69:应使用finally避免资源泄漏 除非发生让应用程序中断的异常,否则finally总是会先于return执行.finally的这个语言特性决定了资源释放的最佳位置就是在finally块中:另 ...

- [原创]java WEB学习笔记69:Struts2 学习之路-- 消息处理与国际化,概述,配置国际资源文件,访问国际化消息,通过超链接切换语言

本博客的目的:①总结自己的学习过程,相当于学习笔记 ②将自己的经验分享给大家,相互学习,互相交流,不可商用 内容难免出现问题,欢迎指正,交流,探讨,可以留言,也可以通过以下方式联系. 本人互联网技术爱 ...

- Android反编译获取资源文件-android学习之旅(69)

有时候你看到一些很好看的布局,会考虑别人怎么实现的,回想参考一下,那么这时候反编译一下是很必要的. 要用到的工具apktool.bat和aapt.exe和apktool.jar(要最新版本) 下载前两 ...

随机推荐

- 在64位系统上部署BDE的要点

首先,据我所知,Borland/CodeGear没有发布过支持64bit windows的BDE安装包,如果你在网上看到了相关的BDE安装包,很有可能是使用者自己重新打包发布的. 无论是在32bit ...

- 第209天:jQuery运动框架封装(二)

运动框架 一.函数------单物体运动框架封装 1.基于时间的运动原理 动画时间进程 动画距离进程 图解: 物体从0移动到400 当物体移动到200的时候 走了50% 同样的,物体总共运行需要4秒 ...

- Repository HDU - 2846 (trie)

题中没给范围 所以控制不好数组范围..不是超内存就是runtime.. 好吧 到了晚上终于调出来数组模拟的了 题意: 求含有某字符段的个数 解析: 把每个字符串遍历一遍 以每个元素为起点建树就好了.. ...

- list的4种遍历方式

import java.util.ArrayList;import java.util.Iterator;import java.util.List; import com.hbut.domain.P ...

- After ZJOI2017 day2

4.28早上6点左右就起了床,怀着紧张的心情,候到了7:45进考场 看到题,先0.5h看了看题意,yy一下,至少10+20+10. 首先是觉得T3可以搞一搞,先想到SA,很快就X掉了,思索一会儿,感觉 ...

- 洛谷 P3102 [USACO14FEB]秘密代码Secret Code 【区间dp】

农民约翰收到一条的消息,记该消息为长度至少为2,只由大写字母组成的字符串S,他通过一系列操作对S进行加密. 他的操作为,删除S的前面或者后面的若干个字符(但不删光整个S),并将剩下的部分连接到原字符串 ...

- 手脱PE Pack v1.0

1.PEID查壳 PE Pack v1.0 2.载入OD,一上来就这架势,先F8走着 > / je ; //入口点 -\E9 C49D0000 jmp Pepack_1.0040D000 004 ...

- 协程-遇到I/O自动切换

参考博客:http://www.cnblogs.com/alex3714/articles/5248247.html 一.前言 Gevent 是一个第三方库,可以轻松通过gevent实现并发同步或异步 ...

- tomcat maven插件启动报错tomcat-users.xml cannot be read

tomcat maven插件启动报错tomcat-users.xml cannot be read [ERROR] Failed to execute goal org.codehaus.mojo:t ...

- libxml2在mingw下编译

1.配置MingW路径,在环境变量path中加入/mingw32/bin2.解压libxml,进入win32目录3.记事本打开configure.js,找到var compiler = "m ...