scan design flow(一)

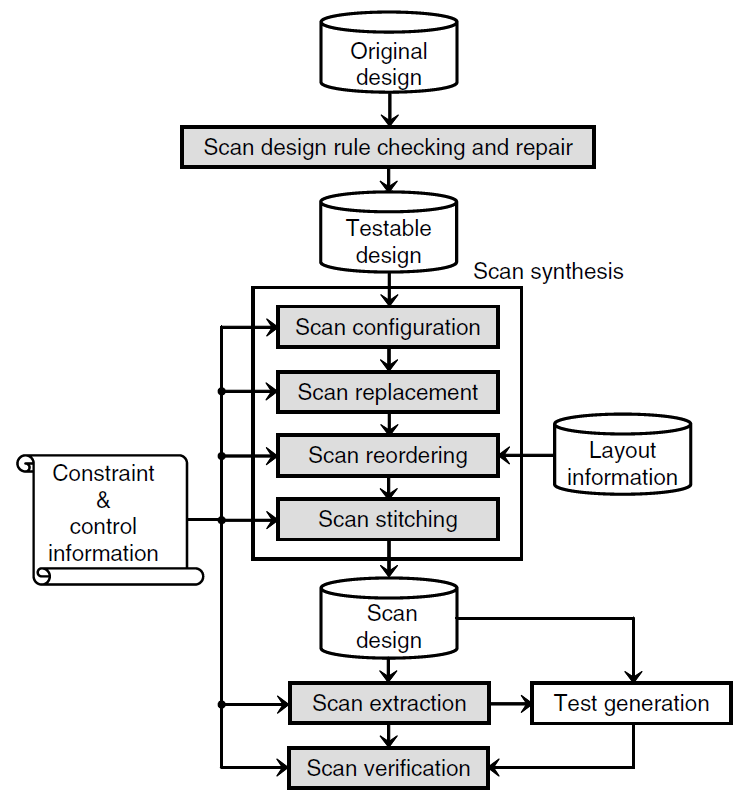

一个典型的scan实现的flow:

clock mux和一些rst,在Scan中都被bypass掉,是不能测到的。所以DFT的test coverage一般就在97%或98%。

scan design rule checking and repair:

可以在presynthesis RTL design或者postsynthesis gate-level design上进行,

经过scan repair之后的design,称为testable design。

scan synthsis是将一个testable design转换为一个scan design,目前design中会包含好几条scan chain。

scan extraction是将最终scan chain的结构提取出来,供ATPG使用。

scan verification针对shift,capture操作,进行response的验证。

Scan Design Rule Checking and Repair

进行scan design rule的check,某些clock control structure需要修改来增加at-speed test。

scan design rule的check也可以在scan synthesis之后,来保证没有新的violation出现。

在shift操作中,所有的clock都可以通过external pin来控制,在相邻的两个scan cell之间的

clock skew必须保证不会引起shift failure。

在capture操作中,data path的originate/terminate的clock可能是不一样的,这时需要考虑

timing来保证capture操作的正确。

Scan Synthesis

scan synthesis将一个testable design转变为一个scan design。

在1990年,scan synthesis的操作是一些分散的tools,将logic synthesis后的gate_level

netlist进行处理。

最近,scan synthesis的操作已经集成在了logic synthesis中,这样的处理,称为one-pass

synthesis或者single-pass synthesis。

主要包括四个部分:1)scan configuration; 2)scan replacement; 3)scan reordering;

4)scan stitching;

scan chain主要包括:

1)the number of scan chain;

2)the type of scan cells to implement these scan chain;

3)storage element to be excluded from scan synthesis;

4)the way of scan cell arranged in scan chain;

scan chain number主要由电路的input和output的个数来决定,high-speed的IO pad是不能

被用来做scan IO复用的。

scan cell的type,主要由lib来决定,一般每一种使用的storage element都会有相应的scan cell type,

来保证functionality和timing在正常操作下,被影响的最小。

exclude的storage element主要因为critical path或者security reason等。

storage element的arrange,主要由这些scan chain上的clock domain的多少来决定。

一般情况下,一个scan chain由属于同一个clock domain的scan cell组成,(因为在DC过程中,整个scan chain是一条data path

此时的异步逻辑在DFT中也会是同步的处理。)

当一个clock domain包含很多的scan cells时,一些scan chain会被结构化的实现,scan-chain operation被用来减小scan-chain的长度。

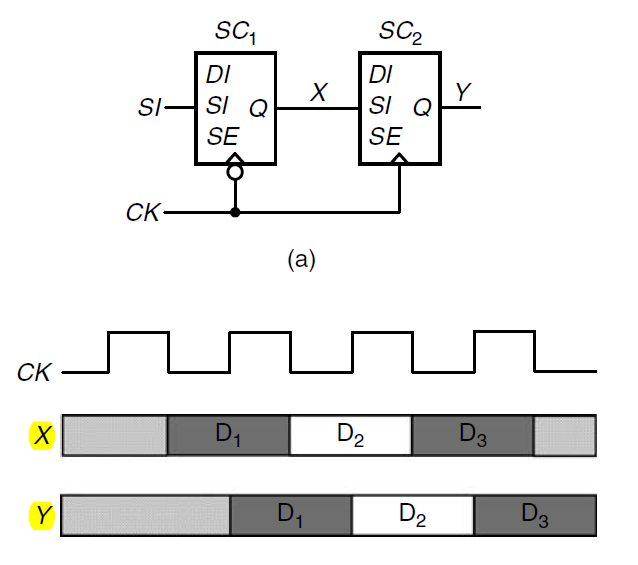

当一个scan-chain中既包含negative-edge scan cell又包括positive-edge scan cell时,negative的scan cell

应该放在positive scan-cell的前边。(为了clock一个周期只移动一位)

scan-chain的长度尽量平衡,方便并行化。

如果positive scan-cell放在前边,那么这两个cell在一个clock周期内,都会shift data。

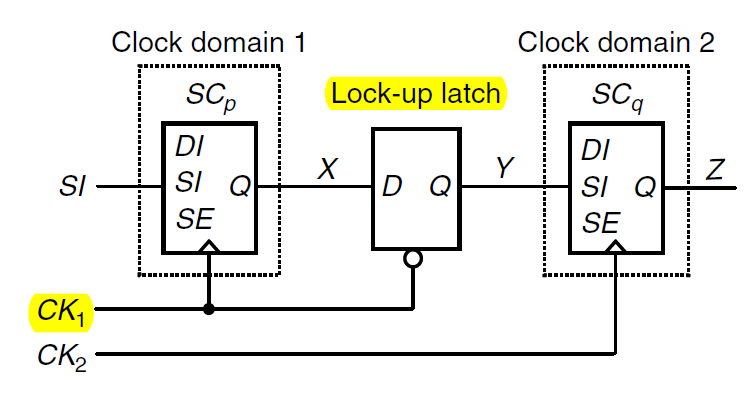

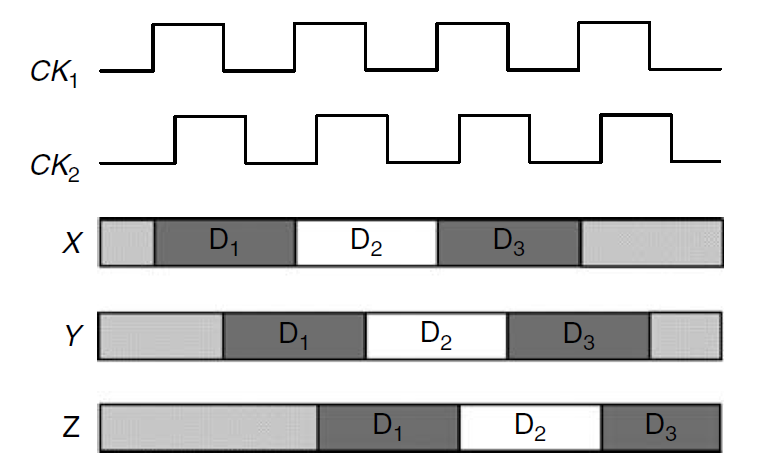

当一个scan-chain的scan cell来自不同的clock domain时,一个lock-up latch需要插入。

这样可以保证,不论CK2优先CK1还是CK1优先CK2,shift的操作都是正确的。

但是必须保证CK1和CK2之间的skew少于一个duty cycle。

当scan chain的clock结构定下来以后,进行scan cell的stitch到scan chain以及这些scan cell的

place,stitch以最小化scan routing为目标。

Scan Replacement:

经过scan configuration,scan replacement将storage element替换为functionally equivalent scan cell

这时的design叫做,scan-ready design。

这些scan cell的input通常连接到同一个scan cell的output来避免floating。这些连接在stitch阶段去除。

目前,在RTL阶段也可以实现部分的scan replacement。

Scan Reordering

反应scan chain中scan cell的reorder。在物理实现之前,一个random的scan order被design使用。

在进行physical implementation时,scan order可以使用intra_scan_chain reordering(scan cell只在该scan

chain内进行reorder)和inter_scan_chain reordering(scan cell在不同的scan chain之间reorder)

scan stitching

将所有的scan cell stitch到一起,组成scan chain。将每一个scan cell的output连接到下一级的input。

将第一个scan cell的input连接到primary input,最后一个scan cell的output连接到primary output。

在stitch的过程中,需要插入一些lock_up的latch和lock_up的FF来保证shift操作正确。

scan design flow(一)的更多相关文章

- scan design flow(二)

在scan stitch之后,scan synthesis就已经完成, Scan extraction主要用来从scan design中extracing所有的instance,来保证scan cha ...

- Atitit vod click event design flow 视频点播系统点击事件文档

Atitit vod click event design flow 视频点播系统点击事件文档 重构规划1 Click cate1 Click mov4 重构规划 事件注册,与事件分发管理器分开 ...

- scan design rules

为了更好的设计一个scan design,一些scan design的rule必须遵循. 1)tristate bus在shift mode下必须保持bus contention: 2)bidirec ...

- FPGA design flow

FPGA engineering process usually involves the following stages: Architecture design. This stage invo ...

- scan cell

scan cell有两种不同的input: 1)data input:由电路的combinational logic驱动: 2)scan input:由另一个scan cell驱动,从而形成scan ...

- scan & ATPG

Testability用来表征一个manufactured design的quality. 将testability放在ASIC前端来做,成为DFT(Design For Test),用可控(cont ...

- SMTS Silicon Design Engineer Location: Beijing, Beijing, CN

https://jobs.amd.com/job/Beijing-Physical-Design-Engineer-Beij/603603700/?locale=en_US What you do a ...

- ARM JTAG 信号 RTCK 应该如何处理?

用户在调试内嵌可综合内核的 CPU 如 ARM7TDMI-S 时,需要通过打开仿真器的自适应时钟功能. 此时,ARM仿真器根据 RTCK 时钟信号的频率,产生可用于 CPU 内核当前时钟主频的最快的 ...

- DFT 问答 III

1.Boundary scan Boundary Scan就是我们俗称的边界扫描.Boundary Scan是上世纪90年代由 Joint Test Action Group(JTAG)提出的,它的初 ...

随机推荐

- Python排列组合实验

import itertools 排列: 4个数内选2个 >>> print list(itertools.permutations([1,2,3,4],2)) [(1, 2), ( ...

- for循环数据节点

1.需要实现的功能,动态填充多条银行卡信息 2.dom结构 3.数据节点 4.实现方式 //获取银行卡基本信息 CmnAjax.PostData("Handler/Users/Users.a ...

- JQuery:JQuery捕获HTML

JQuery:捕获HTML1.jQuery - 获取内容和属性介绍: jQuery 拥有可操作 HTML 元素和属性的强大方法. jQuery 中非常重要的部分,就是操作 DOM 的能力. jQuer ...

- Java native关键字

在String类中 public native String intern(); native关键字是干嘛的? Java不是完美的,Java的不足除了体现在运行速度上要比传统的C++慢许多之外,Jav ...

- 第五篇 Integration Services:增量加载-Deleting Rows

本篇文章是Integration Services系列的第五篇,详细内容请参考原文. 在上一篇你学习了如何将更新从源传送到目标.你同样学习了使用基于集合的更新优化这项功能.回顾增量加载记住,在SSIS ...

- MongoDB是?

MongoDB是? MongoDB是一个基于分布式文件存储的数据库 由C++编写 旨在为 WEB 应用提供可扩展的高性能数据存储解决方案 是一个介于关系数据库和非关系数据库之间的产品,是非关系数据库当 ...

- 用仿ActionScript的语法来编写html5——第八篇,图片处理+粒子效果

用仿ActionScript的语法来编写html5系列开发到现在,应该可以做出一些东西了,下面先来研究下图片的各种效果预览各种效果看下图效果和代码看这里,看不到效果的请下载支持html5的浏览器 ht ...

- ipmi使用

1.安装ipmitool Linux: yum -y install OpenIPMI-tools 备注:Linux机器也可以安装ipmi yum -y install OpenIPMI OpenI ...

- 多配置文件部署mysql单机多实例

1.安装gcc-c++.ncurses依赖包 # yum install gcc-c++ ncurses-devel 2.安装cmake,用来编译mysql # tar -xvf cmake-3.2. ...

- openSuSE DNS SERVER CONFIG

system:openSuSE 12.3(much better and frendly than the 12.1 in network config)1,network config,attent ...