s3c2440裸机-内存控制器(四、SDRAM原理-cpu是如何访问sdram的)

1.SDRAM原理

black

(1)SDRAM内部存储结构:

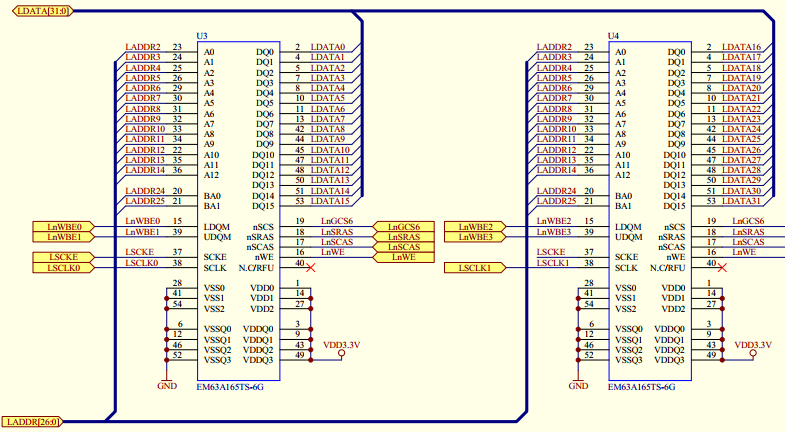

(2)再看看与2440连接的SDRAM原理图:

sdram引脚说明:

A0-A12:地址总线

D0-D15:数据总线(位宽16,2片级联成位宽32)

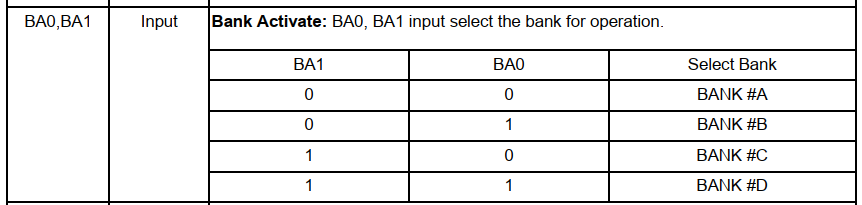

BA0-BA1:bank选择

nSCS:片选

nSRAS:行地址选择

nSCAS:列地址选择

nWE:写使能

SCLK:时钟

SCKE:时钟使能

(3)SDRAM的地址范围:

之前我们讲“二、不同位宽外设与CPU地址总线的连接”这一节的时候,我们留下了一个问题,SDRAM的地址范围是多少?

我们知道地址范围肯定是base_addr + size。我们根据片选接了nGCS6,base_addr=0x3000,0000,那么size是多大呢?

下图是我截取的sdram手册上的特性描述:

我们看见容量为:4M word x 16-bit x 4-bank = 32M,再看原理图我们是两片级联,所以容量为4M word x 32-bit x 4-bank=64M。所以地址范围是[0x3000_0000 ~ 0x33ff_ffff]

(4)SDRAM数据访问原理:

我们知道64M=220*26=226,那么需要26条地址线,再看看原理图,我们发现SDRAM的地址线A[12:0]只有13条,那么最多只能访问213=8K的数据,地址线明显配不上这么大的容量,那么它是如何解决的呢?

答:当然是拆分地址了,地址分多次传输。我们从SDRAM的内部存储结构得知要确定SDRAM的一个存储单元,先确定是哪个bank,然后再确定在哪一行、哪一列即可。

SDRAM有4个bank,由BA0、BA1决定选中哪个bank,查看SDRAM手册见下图;

然后通过选中nSRAS选中行地址,从而发送行地址;最后通过选中nSCAS选中列地址,从而发送列地址。

举个栗子:

CPU执行如下指令:

ldr r0, =0x30000000;

ldr r1, [r0]; 从SDRAM基地址读取4byte数据

过程分析:

1.发出片选信号nGCS6,选中SDRAM

2.发出bank选中信号(BA0,BA1),确定是SDRAM上的哪个bank,从原理图得知CPU的ADDR24、ADDR25对应SDRAM上的BA0,BA1,所以让BA0、BA1=00,选中bankA。

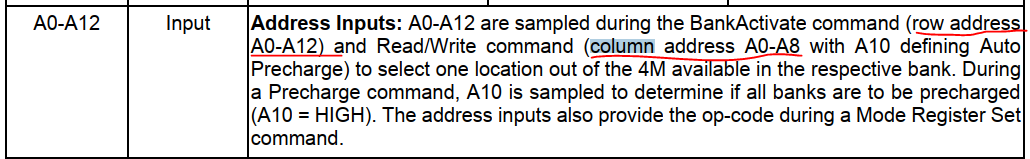

从SDRAM手册确定行列地址的数目,如下图:

3.发出行地址信号nSRAS,使能行地址传输。传输行地址,确定是哪一行(看SDRAM手册确定行地址数(A12-A0)13条)

4.发出列地址信号nnSCAS,使能列地址传输。传输列地址,确定是哪一列(看SDRAM手册确定列地址(A8-A0)9条)

从而发送完整的0x30000000地址到了SDRAM,SDRAM返回4byte数据给CPU。

s3c2440裸机-内存控制器(四、SDRAM原理-cpu是如何访问sdram的)的更多相关文章

- s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)

不同位宽设备的连接 black 我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的. 8bit rom与CPU地址线的连接 8bit*2 rom与CPU地址线的连接 8bit*4 r ...

- s3c2440裸机-内存控制器(一、内存控制器的原理)

1.内存接口概念 S3C2440是个片上系统,有GPIO控制器(接有GPIO管脚(GPA-GPH)),有串口控制器 (接有TXD RXD引脚),有memory controller内存控制器,有Nan ...

- s3c2440裸机-内存控制器(五、SDRAM编程实现)

配置内存控制器-SDRAM编程配置 2440内存控制器共有13个寄存器. BANK0--BANK5只需要设置BWSCON和BANKCONx(x为0-5)两个寄存器: BANK6.BANK7外接SDRA ...

- s3c2440裸机-内存控制器(三、norflash初始化-时序设置)

1.norflash与2440的硬件连接 2.初始化nor,配置nor时序 1.如图是S3C2440的内存控制器的可编程访问周期读写时序,里面的时间参数要根据外部设备的性能进行配置,这里先列出时间参数 ...

- s3c2440内存控制器与SDRAM基本测试

前面我们实验的LED和串口程序,是cpu发送地址给特定的寄存器,在寄存器中写相应的位,达到控制要求. 第一类是GPIO门电路如LED,第二类是协议类如串口,这些都不是cpu直接给地址信息,而是通过寄存 ...

- 十二、S3C2440 裸机 — SDRAM

12.1 SDRAM 介绍 12.1.1 SDRAM 定义 SDRAM(Synchronous Dynamic Random Access Memory):同步动态随机存储器-内存条 同步是指内存工作 ...

- S3C2440内存控制器详解

S3C2440A Memory Map after Reset S3C2440的内存空间划分为不同的块,当CPU向内存控制器发出地址,内存控制器根据地址范围,发出对应片选信号到片选引脚,实现对不同设备 ...

- S3C2440—7.存储控制器访问外设

文章目录 一.内存接口的概念 二.存储控制器(内存控制器) 2.1 什么是存储控制器? 2.2 S3C2440存储控制器介绍 2.3 存储控制器如何处理不同位宽的外设 2.4 怎么确定芯片的访问地址? ...

- CPU缓存是位于CPU与内存之间的临时数据交换器,它的容量比内存小的多但是交换速度却比内存要快得多。CPU缓存一般直接跟CPU芯片集成或位于主板总线互连的独立芯片上

一.什么是CPU缓存 1. CPU缓存的来历 众所周知,CPU是计算机的大脑,它负责执行程序的指令,而内存负责存数据, 包括程序自身的数据.在很多年前,CPU的频率与内存总线的频率在同一层面上.内存的 ...

随机推荐

- mysql主从复制原理及实践

Mysql主从复制原理及实践 mysql主从框架 MySQL主从架构是MySQL集群中最基本也是最常用的一种架构部署,能够满足很多业务需求,常见的有一主一从或者一主多从.可以防止单一主机的 ...

- 十大C++实战项目,你会几个?【高薪必备】

前言 本文的文字及图片来源于网络,仅供学习.交流使用,不具有任何商业用途,版权归原作者所有,如有问题请及时联系我们以作处理.作者:实验楼 市面上有很多C++的实战项目,从简单到进阶,学习每个项目都 ...

- 用FPGA设计LCD 转 VGA

这个东西其实是在上一个冬天就做完了,而且似乎已经产业化了,当时是为一位朋友做的,这个朋友再卖给产业化的人,就像流于俗套的故事一样,这个朋友拿到了钱,不过不像项目开始时说的那样与我有关.想想多年前一起吃 ...

- Orleans[NET Core 3.1] 学习笔记(一).NET环境下的分布式应用程序

前言 Orleans是一个跨平台的框架,用于搭建可扩展的分布式应用程序 第一次接触Orleans还是两年前做游戏服务器的时候,用SignalR+Orleans的组合,写起代码来不要太爽. 即将进入20 ...

- 2019年Java并发精选面试题,哪些你还不会?(含答案和思维导图)

Java 并发编程 1.并发编程三要素? 2.实现可见性的方法有哪些? 3.多线程的价值? 4.创建线程的有哪些方式? 5.创建线程的三种方式的对比? 6.线程的状态流转图 7.Java 线程具有五中 ...

- 3年java开发竟然还不知道Lambda的这个坑

背景 有朋友反馈zk连接很慢.整理出zk连接的关键逻辑如下: 上面的代码造成第一次调用ClientZkAgent.getInstance的时候,需耗时10s, 这个时间恰好跟semaphore的超时时 ...

- 2016/10/21 java中的参数传方式

参考:http://blog.sina.com.cn/s/blog_59ca2c2a0100qhjx.html http://www.cnblogs.com/caiyao/p/4964176.html

- 冒泡排序(表格说明)(js)

冒泡排序我自己的理解是(假设从大到小): 比较每一对相邻元素的值,如果前面的元素小于后面的元素那么就将它们交换过来,每次排序的比较次数逐次递减,最后的比较次数为1.总的排序轮数为数组长度减1.为了便于 ...

- GHOST CMS - 结构 Structure

Structure Ghost主题包含静态HTML模板,这些模板使用helper类从站点输出数据,并使用定制的CSS进行样式化 A Ghost theme contains static HTML t ...

- Python是什么?你真的了解Python吗?

一.Python是什么相信混迹IT界的很多朋友都知道,Python是近年来最火的一个热点,没有之一.从性质上来讲它和我们熟知的C.java.php等没有什么本质的区别,也是一种开发语言,而且已经进阶到 ...