多线程 - 内存屏障和cpu缓存

CPU性能优化 - 缓存

为了提高程序运行的性能,现代CPU在很多方面会对程序进行优化。CPU的处理速度是很快的,内存的速度次之,硬盘速度最慢。在cpu处理内存数据中,内存运行速度太慢,就会拖累cpu的速度。为了解决这样的问题,cpu设计了多级缓存策略。

CPU分为三级缓存: 每个CPU都有L1,L2 但是L3是多核公用的。

- L1 Cache (一级缓存)是CPU第一层告诉缓存,分为数据缓存和指令缓存。一般服务器的CPU的L1缓存的容量通常在32-4096K

- L2 Cache (二级缓存)由于L1高速缓存的容量限制,为了再次提高CPU的运算速度,在CPU外部放置一告诉存储器,即二级缓存。

- L3 Cache (三级缓存) 都是内置的,它的作用是进一步降低内存延迟,同事提升大数据量计算时处理器的性能。具有较大L3缓存的处理器,能提供更有效的文件系统缓存行为及较短的消息和队列长度。一般多核共享一个L3缓存。

CPU查找数据的顺序为: CPU -> L1 -> L2 -> L3 -> 内存 -> 硬盘

缓存同步协议

因为每个CPU都有自己的缓存,容易导致一种情况就是 如果多个CPU的缓存(多CPU读取同样的数据进行缓存,进行不同运算后,写入内存中)中都有同样一份数据,那这个数据要如何处理呢?已谁的为准? 这个时候就需要一个缓存同步协议了!

MESI协议 规定每条缓存都有一个状态位,同时定义了一下四种状态:

- 修改态 (Modified) 此缓存被修改过,内容与住内存不同,为此缓存专有

- 专有态 (Exclusive) 此缓存与主内存一致,但是其他CPU中没有

- 共享态 (Shared) 此缓存与住内存一致,但也出现在其他缓存中。

- 无效态 (Invalid) 此缓存无效,需要从主内存中重新读取。

多处理器,单个CPU对缓存修改,需要通知其他CPU. 也就意味着,CPU需要控制自己的读写,还需要监听其他CPU发出的通知,从而保持最终一致性。

CPU性能优化 - 运行时指令重排序

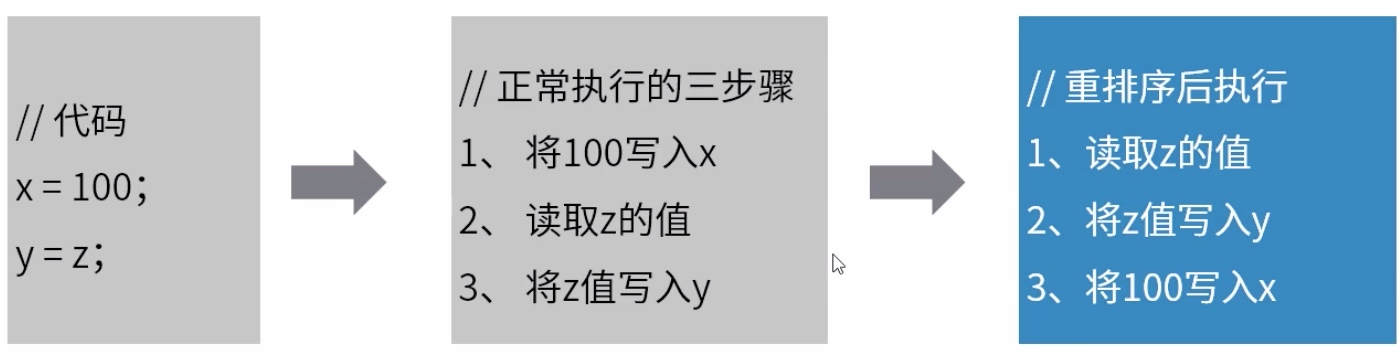

例如如下代码是:

指令重排:当CPU 写缓存 时发现缓存区被其他CPU占用,为了提高CPU处理性能,可能将后面的读缓存命令优先执行。

指令重排序,遵循 as-if-serial语义。即指令重排序前后,程序执行的结果不能变化。对于数据有依赖的部分,不会进行重排序。

问题

1、CPU高速缓存的问题:

缓存中的数据与主内存的数据不是实时同步的,各个CPU间缓存的数据也不是实时同步的,在同一时间点,各个CPU所看到的的同一内存地址的数据可能是不一致的

2、CPU指令重排优化问题:

虽然遵循 as-if-serial语义,但是它是仅在单个CPU自己执行的情况下保证结果正确,多核多线程,指令逻辑无法分辨因果关联,可能出现乱序执行,导致程序结果出现错误。

内存屏障解决以上问题

写内存屏障(Store Memory Barrier):在指令后插入Store Barrier,能让写入缓存中最新数据更新写入主内存中,让其他线程可见。 强制写入主内存,这种显示调用,不会让CPU去进行指令重排序

读内存屏障(Load Memory Barrier):在指令后插入Load Barrier,可以让高速缓存中的数据失效,强制重新从住内存中加载数据。 也是不会让CPU去进行指令重排。

多线程 - 内存屏障和cpu缓存的更多相关文章

- C和C++中的volatile、内存屏障和CPU缓存一致性协议MESI

目录 1. 前言2 2. 结论2 3. volatile应用场景3 4. 内存屏障(Memory Barrier)4 5. setjmp和longjmp4 1) 结果1(非优化编译:g++ -g -o ...

- JMM内存模型、CPU缓存一致性原则(MESI)、指令重排、as-if-serial、happen-before原则

JMM三大特性原子性 汇编指令 --原子比较和交换在底层的支持 cmp-chxg 总线加锁机制 Synchronized Lock锁机制 public class VolatileAtomicSamp ...

- 内存屏障在CPU、JVM、JDK中的实现

前言 内存屏障(英语:Memory barrier),也称内存栅栏,内存栅障,屏障指令等,是一类同步屏障指令,它使得 CPU 或编译器在对内存进行操作的时候, 严格按照一定的顺序来执行, 也就是说在内 ...

- volatile 和 内存屏障

接下来看看volatile是如何解决上面两个问题的: 被volatile修饰的变量在编译成字节码文件时会多个lock指令,该指令在执行过程中会生成相应的内存屏障,以此来解决可见性跟重排序的问题. 内存 ...

- 【C# 线程】内存屏障 MemoryBarrier

背景 同步基元分为用户模式和内核模式 用户模式:Iterlocked.Exchange(互锁).SpinLocked(自旋锁).易变构造(volatile关键字.volatile类.Thread.Vo ...

- 基于JVM原理、JMM模型和CPU缓存模型深入理解Java并发编程

许多以Java多线程开发为主题的技术书籍,都会把对Java虚拟机和Java内存模型的讲解,作为讲授Java并发编程开发的主要内容,有的还深入到计算机系统的内存.CPU.缓存等予以说明.实际上,在实际的 ...

- LINUX内核内存屏障

================= LINUX内核内存屏障 ================= By ...

- java内存屏障

为什么会有内存屏障 每个CPU都会有自己的缓存(有的甚至L1,L2,L3),缓存的目的就是为了提高性能,避免每次都要向内存取.但是这样的弊端也很明显:不能实时的和内存发生信息交换,分在不同CPU执行的 ...

- [SPDK/NVMe存储技术分析]006 - 内存屏障(MB)

在多核(SMP)多线程的情况下,如果不知道CPU乱序执行的话,将会是一场噩梦,因为无论怎么进行代码Review也不可能发现跟内存屏障(MB)相关的Bug.内存屏障分为两类: 跟编译有关的内存屏障: 告 ...

随机推荐

- Vue 使用v-bind:style 绑定样式

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...

- javascript二叉树

javascript中的二叉树一(binary tree) 毕业也快2年了,毕业之后就没有认真写过博客了,都是那里学习一下,这里弄一下.学习了也不做笔记,过后就忘记了.我对这种状态打从心里是讨厌的. ...

- node.js npm 操作 模块化开发 cnpm镜像安装

模块(包) 传统引入 js 的缺点 整个网页,我们写了一个 js 文件,所有的特效都在里面 耦合度太高,代码之间关联性太强,不便于后期维护 变量容易 全局污染 如果将 复杂的 js 文件,拆成多个功能 ...

- vivo 部分链表反转

方法一:使用栈交换需要反转的数字 #include <iostream> #include <stack> #include "list.h" using ...

- ASP.NET对路径"C:/......."的访问被拒绝 解决方法小结 [转载]

问题: 异常详细信息: System.UnauthorizedAccessException: 对路径“C:/Supermarket/output.pdf”的访问被拒绝. 解决方法: 一.在IIS中的 ...

- 是否被封禁ip或端口的检测网站 ping

国内的: http://tool.chinaz.com/port (可以检测端口) https://tools.ipip.net/ping.php (貌似不可以检测端口) 国外的: https://w ...

- C# user32.dll找窗口时,使用GetClass方法解决 【带有系统自动编译的窗体类后缀名】 问题

[DllImport("user32.dll", SetLastError = true, CharSet = CharSet.Auto)] static extern int G ...

- 设置了responseType:Blob之后,如果返回json错误信息,如果获取?

最近做了一个文件下载功能,于是设置了responseType: Blob的方式, 什么是Blob呢,MDN官方解释:Blob 对象表示一个不可变.原始数据的类文件对象.Blob 表示的不一定是Java ...

- oracle ogg--ogg搭建过程中遇到的错误及处理

1 PRVF-0002 : Could not retrieve local nodename---# Begin Stacktrace #---------------------------ID: ...

- 【ABAP系列】SAP ABAP 取两个内表的交集 比较两个内表的不同

公众号:SAP Technical 本文作者:matinal 原文出处:http://www.cnblogs.com/SAPmatinal/ 原文链接:[ABAP系列]SAP ABAP 取两个内表的交 ...