基于AHB_BUS的eflash控制器设计-02

基于AHB-BUS的eflash控制器设计

1.Flash Spec

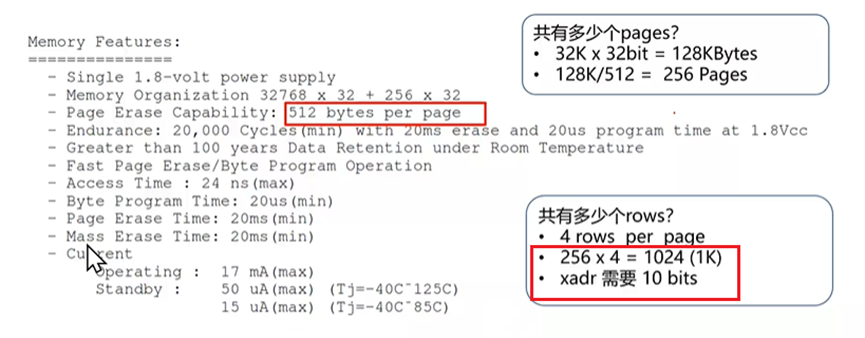

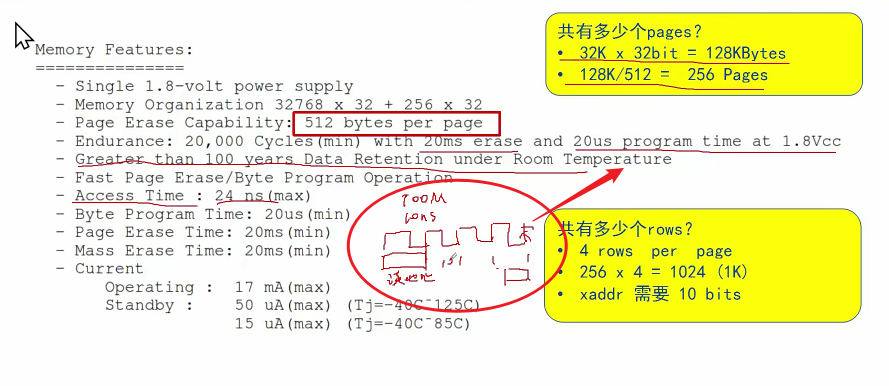

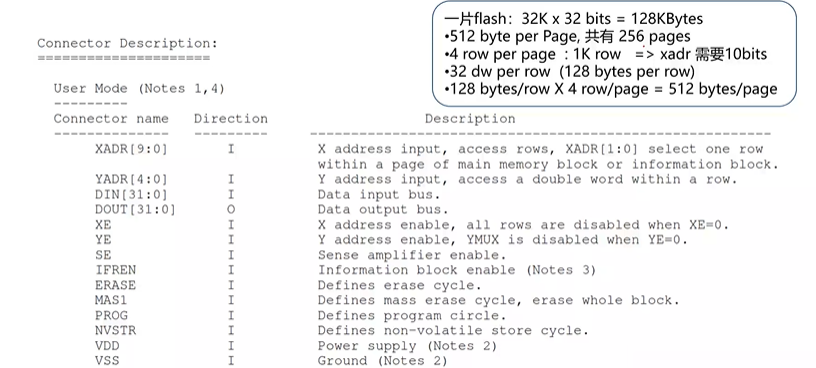

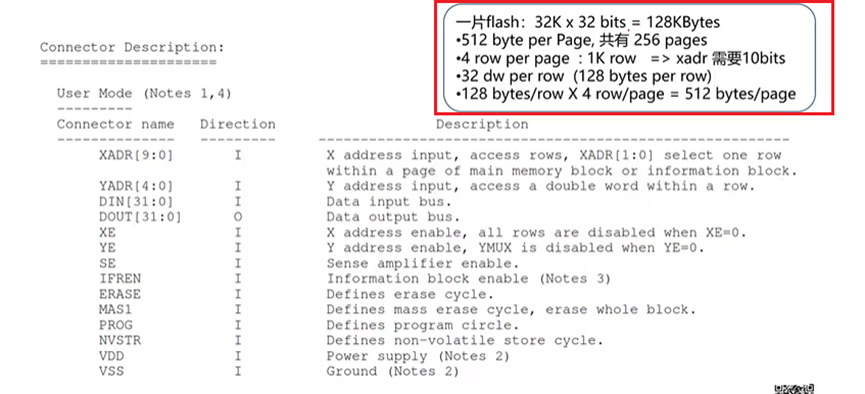

1.1 地址映射

- XADR是10bit?因为一共有1024行

- 每一行128byte容量,每次读取的粒度就是一个double word-32bit-4byte,所以一行有32个dw。

- 如果要读取一个dw的数据,除了需要知道其存在与哪一行,还需要知道它存在于哪一列。所以需要一个纵坐标地址YADR,32个dw每行,所以需要5bit的地址。

- 地址映射:首先将memory分成page,page分成row,row分成double word。

- 如果是information block,其容量为256*32bit(256个dw),一行有32dw,所以需要8行,地址表示为YADR的五位加上XADR的低三位一共8bit地址,表示寻址256个dw

- XADR表示选中某一个行,YADR表示选中某行中的32bit,如果存储容量变为64K*32bit,XADR变为[10:0]的11位,YADR仍然是[4:0],每行存储的容量不变

- XADR表示选中行,如何通过XADR得到page地址,XADR中的[9:2]表示page地址,[1:0]表示每个page中的行

- 两片存储体选择,在最高位添加一位进行选择

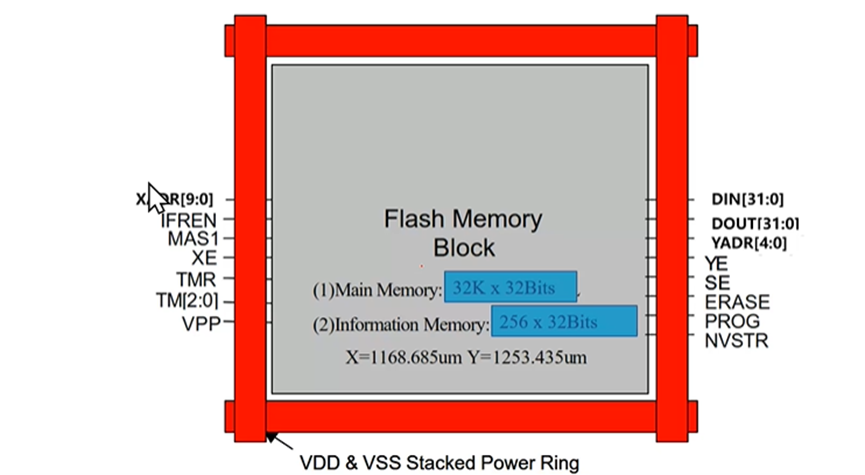

1.2 信号

- eFlash没有clock,所以信号要自己生成

- XADR—寻址的是行,10bit,低两位表示page中的哪一行,[9:2]表示选择的page,[1:0]表示 选择page中的哪一行

- YADR -- 一行中有32个dw,所以使用5bit

- DIN [31:0]—写数据

- DOUT [31:0]—读数据

- XE—拉高表示XADR是有效的,使能每一行的数据,地址驱动到端口上之后需要在enable的作用下确定是否开启行选择

- YE—拉高表示YADR是有效的

- SE—灵敏放大器的使能信号,读数据的时候,读某行某列中存储单元的数据,存储在晶体管中,驱动能力不够,需要灵敏放大器,将信号读到的数据送到输出端

- IFREN—拉高表示访问的是information block,拉低表示访问的是main block,通常可以设置为1

- ERASE—按页擦除

- MSA1—按块擦除

- PROG—数据写入,程序烧录

- NVSTR—非易失性操作(erase和program)

- VDD—电源

- VSS—地

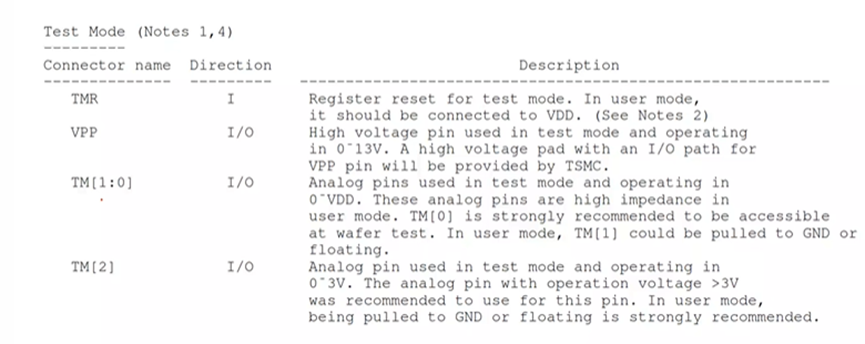

1.3 测试信号

上述都是function mode下的信号,它依然会有测试mode的接口,它的测试更多的是通过基台进行输入激励进行测试。

1.4 电流\电压

- Standby的时候,电流以微安形式存在,在工作状态下的时候,电流以毫安形式存在,在不同的模式下,电流相差一个数量级。不同情况下,电流不同,功耗不同。

- SRAM是一维的寻址,eFlash是二维地址。

- Word是多少位的(32位或者是16位),是根据不同的系统确定的。

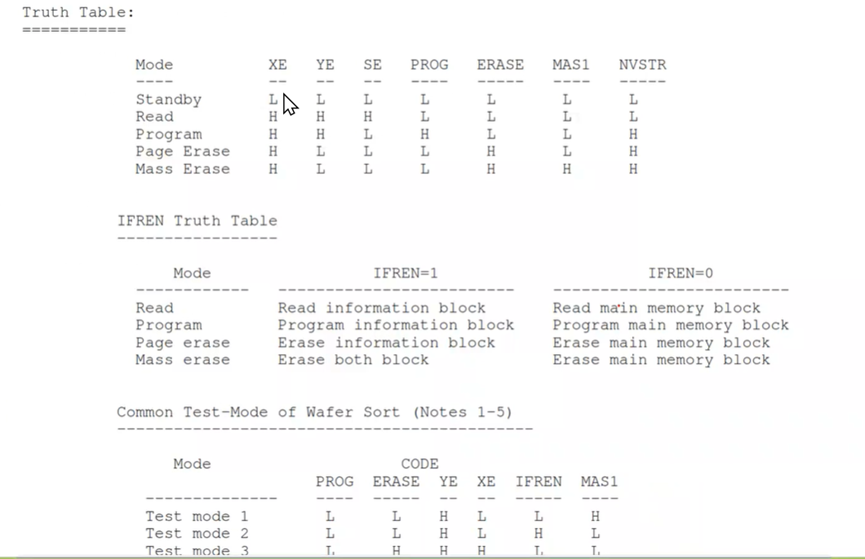

1.4 读写擦信号

- Standby—所有的信号都拉低,可以认为eFlash没有被片选到,此时的功耗是最低的

- Read—SE需要拉高(SE信号只有在读的时候拉高),读的时候需要知道dw的位置,XE,YE都需要被拉高;不是擦除和写入操作,所以PROG和ERASE拉低;不进行eFlash内部数据的更改,所以NVSTR拉低。

- Program—Read和Program的访问单位都是32bit,PROG需要拉高,XE,YE需要进行拉高;当前对于eFlash进行内容操作,非易失性操作NVSTR需要拉高。

- Page Erase—ERASE信号拉高,XE信号拉高,NVSTR信号拉高

- MAS1 Erase-- ERASE信号拉高,MAS1信号拉高,XE信号拉高,NVSTR信号拉高。进行Page Erase和MAS1 Erase的时候,以页为单位,以行为粒度进行擦除,所以YE拉低。

- IFREN—为1的时候,操作的是Information block,为0的时候,操作的是main block。

- Test mode信号主要通过基台进行测试,不需要进行内建自测试

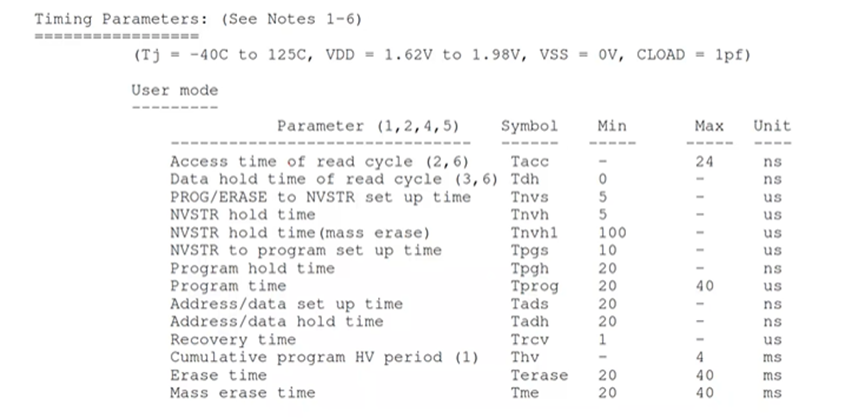

1.5 时序参数(Timing Parameter)

- 设计—》配置寄存器—》将这些参数写成灵活可变的,方便进行修改/更新换代

2.时序说明

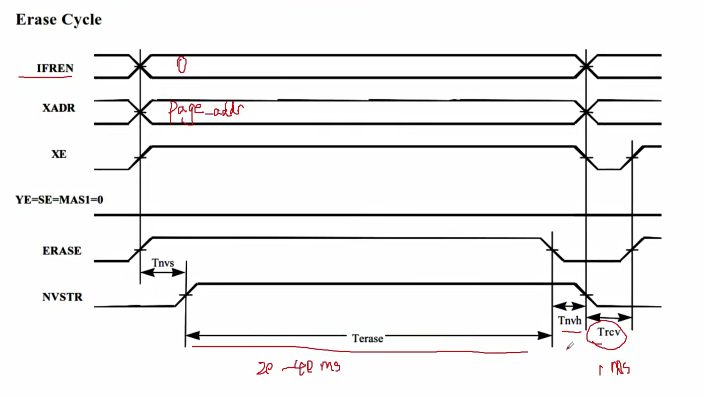

2.1 擦除时序

- 将IFREN信号拉起来,表示擦除那一部分(information block还是main block)

- Page擦除,需要将4个row对应的地址XADR驱动到总线上,不需要考虑YE

- XADR是有效的

- SE是拉低的

- ERASE信号需要拉高,在实际进行擦除的时候ERASE和NVSTR信号同拉高(进行与操作),才会进行擦除。

- 时序约束:PROG/ERASE to NVSTR setup time-Tnvs,NVSTR信号上升沿到达之前,ERASE信号需要保持的时间。上述表中给出Tnvs=5us,如果100M时钟频率,一个周期是0.1us,那么需要维持50个cycle的Tnvs时间。

- Terase = 20-40ms,通过计数器counter进行计数,当达到Terase时间之后,撤销ERASE信号

- 撤销ERASE信号之后,还有一个时间约束,NVSTR需要保持一段时间,Tnvh,之后才能撤销NVSTR

- 撤销NVSTR信号之后,紧接着有一个Trcv,在这段时间内不能进行任何的操作,用于系统恢复

2.2 eFlash时序是异步设计

eFlash是没有时钟的设计,异步设计。SRAMC是同步设计,在时钟的上升沿或者下降沿进行采样操作。

异步设计规范的是不同信号变化的时间间隔,谁先拉高,谁后拉高,两个信号之间信号间隔多久。具体信号保持多久需要使用计数器进行。

如何实现擦写的时序?FSM+counter

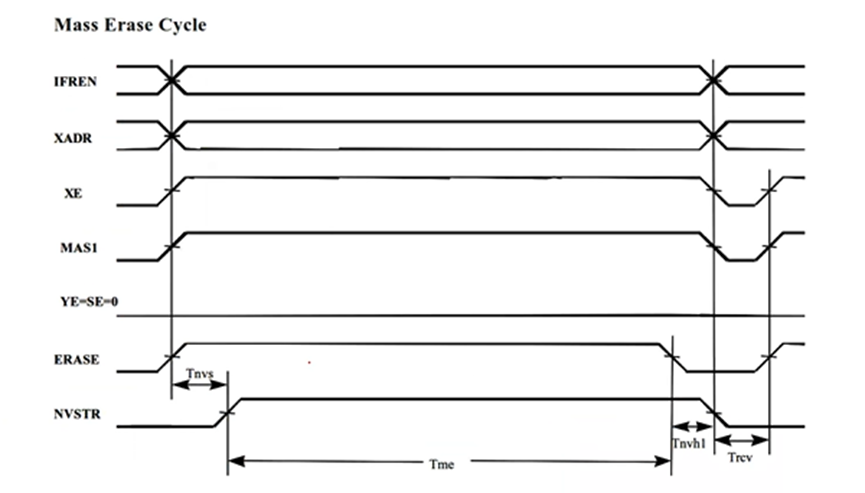

2.3 块擦除(Mass Erase Cycle)

- MAS1—信号需要进行拉高

- Tme和Terase信号可能是不同的(Page Erase和Mass Erase擦除的时间可能是不同的)

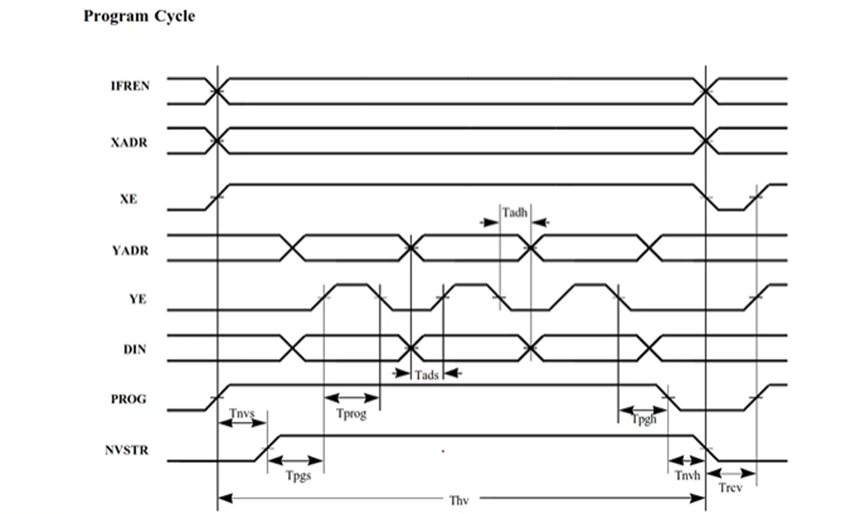

2.4 写时序(Program Cycle)

进行程序的烧录,也就是写时序

- IFREN—编程哪一部分

- XADR,XE需要进行拉高

- Y地址控制之前,PROG信号拉高,表示当前正在进行编程,在进行编程的时候可能对于一行当中的几个dw进行操作;编程操作更改了eFlash中的内容,需要NVSTR拉高。

- NVSTR信号拉高之前,PROG信号需要保持一段时间,满足NVSTR建立时间Tnvs

- Tnvs满足之后,经过一个Tpgs,之后就可以正常编程。Tpgs就是第一个NVSTR经过Tnvs之后到YE上升沿之间的时间,需要PROG保持稳定。

- YE拉高之前,需要将数据准备好,DIN并不是与YE同时拉高,在YE拉高之前DIN需要稳定一段时间,满足Tads。

- YE写一笔数据至少拉高Tprog时间,才能将数据写入。

- YE撤销之后,DIN和YADR需要保持一段时间,满足Tadh。PROG信号撤销之后,NVSTR需要维持一段时间Tnvh。

- NVSTR撤销之后,在之后的Trcv时间内不能进行操作。

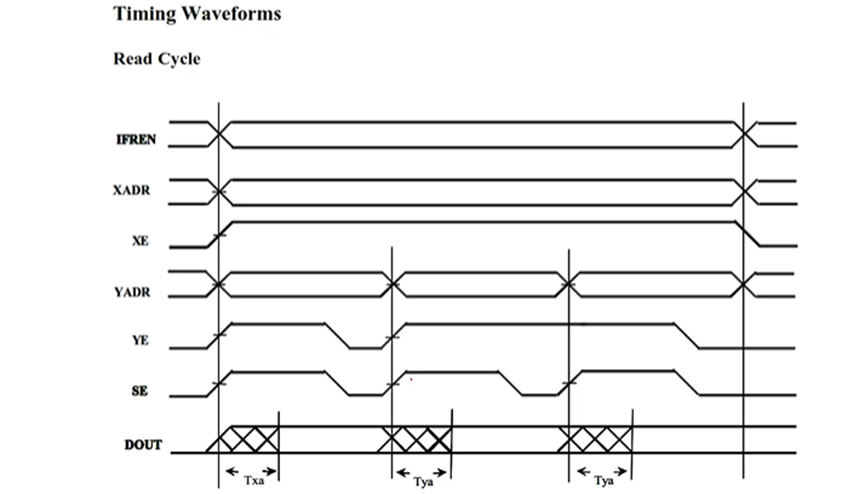

2.5 读时序(Read Cycle)

- IFREN—拉起

- XADR,YADR,XE,YE,SE,信号拉高

- 经过Txa之后,才能访问到读数据

- Txa是首次XADR之后,到首次读取数据的时间间隔;Tya是非首次XADR,切换列数据读取的时间

2.6 时序的控制

使用状态机控制

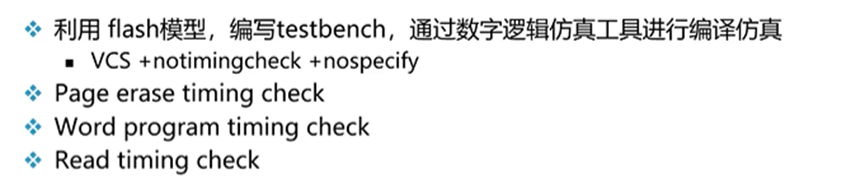

2.7 Flash模型编译仿真

- 拿到Flash模型之后,可以编写testbench进行测试,将激励打到Flash,对Flash进行读写操作,对比结果。

- Tiiming check—eFlash对于时序要求比较高,如果时序不满足要求,仿真的时候会警告,数据写入不了,所以将timing check关闭

- nospecify –关闭延迟模型

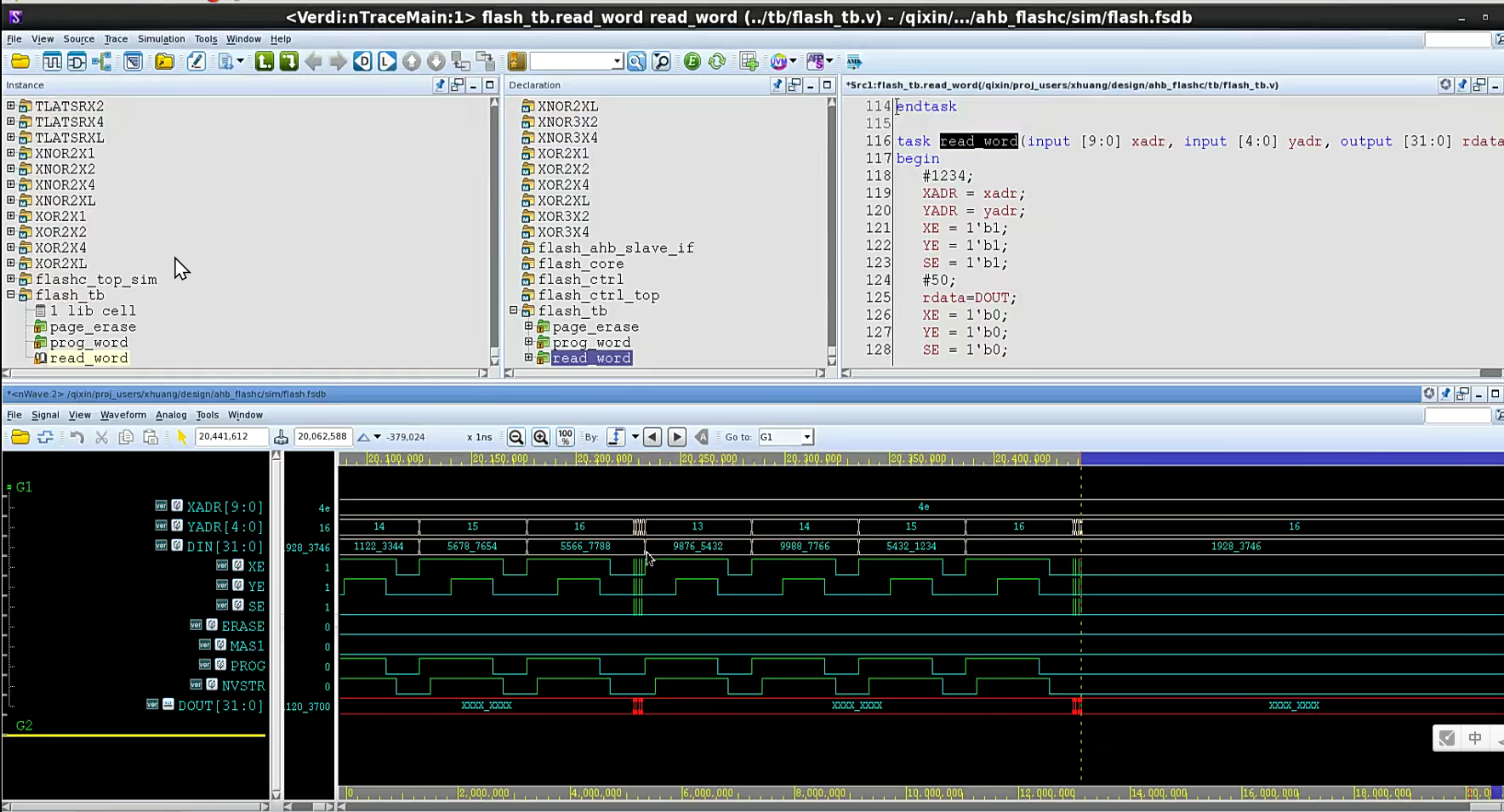

3.对于eFlash存储体的仿真

# 在Makefile设置一个verdi选项,产生fsdb文件

make run_rtl_verdi -- 产生fsdb波形文件

基于AHB_BUS的eflash控制器设计-02的更多相关文章

- 基于ABP落地领域驱动设计-02.聚合和聚合根的最佳实践和原则

目录 前言 聚合 聚合和聚合根原则 包含业务原则 单个单元原则 事务边界原则 可序列化原则 聚合和聚合根最佳实践 只通过ID引用其他聚合 用于 EF Core 和 关系型数据库 保持聚合根足够小 聚合 ...

- 基于ABP落地领域驱动设计-03.仓储和规约最佳实践和原则

目录 系列文章 仓储 仓储的通用原则 仓储中不包含领域逻辑 规约 在实体中使用规约 在仓储中使用规约 组合规约 学习帮助 围绕DDD和ABP Framework两个核心技术,后面还会陆续发布核心构件实 ...

- 基于ABP落地领域驱动设计-00.目录和小结

<实现领域驱动设计> -- 基于 ABP Framework 实现领域驱动设计实用指南 翻译缘由 自 ABP vNext 1.0 开始学习和使用该框架,被其优雅的设计和实现吸引,适逢 AB ...

- 基于ABP落地领域驱动设计-04.领域服务和应用服务的最佳实践和原则

目录 系列文章 领域服务 应用服务 学习帮助 系列文章 基于ABP落地领域驱动设计-00.目录和前言 基于ABP落地领域驱动设计-01.全景图 基于ABP落地领域驱动设计-02.聚合和聚合根的最佳实践 ...

- 基于ABP落地领域驱动设计-05.实体创建和更新最佳实践

目录 系列文章 数据传输对象 输入DTO最佳实践 不要在输入DTO中定义不使用的属性 不要重用输入DTO 输入DTO中验证逻辑 输出DTO最佳实践 对象映射 学习帮助 系列文章 基于ABP落地领域驱动 ...

- 基于ABP落地领域驱动设计-06.正确区分领域逻辑和应用逻辑

目录 系列文章 领域逻辑和应用逻辑 多应用层 示例:正确区分应用逻辑和领域逻辑 学习帮助 系列文章 基于ABP落地领域驱动设计-00.目录和前言 基于ABP落地领域驱动设计-01.全景图 基于ABP落 ...

- 基于FPGA的XPT2046触摸控制器设计

基于FPGA的XPT2046触摸控制器设计 小梅哥编写,未经许可,文章内容和所涉及代码不得用于其他商业销售的板卡 本实例所涉及代码均可通过向 xiaomeige_fpga@foxmail.com 发 ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

- 2014.04.28基于CPLD的LCOS场序彩色视频控制器设计

基于CPLD的LCOS场序彩色视频控制器设计 作者:宋丹娜,代永平,刘艳艳,商广辉 发表刊物:液晶与显示,2009 学习时间:2014.04.28 文章讲述了-- (和上一篇论文有些相似之处) 1. ...

- 基于cocos2d-x的游戏框架设计——李成

视频:http://v.youku.com/v_show/id_XMzc5ODUyMTI4.html?f=17330006 网易科技讯 3月31日,第四届CocoaChina开发者大会暨Cocos2d ...

随机推荐

- ClickHouse(19)ClickHouse集成Hive表引擎详细解析

目录 Hive集成表引擎 创建表 使用示例 如何使用HDFS文件系统的本地缓存 查询 ORC 输入格式的Hive 表 在 Hive 中建表 在 ClickHouse 中建表 查询 Parquest 输 ...

- 微软成为PostgreSQL主要贡献者

微软成为PostgreSQL主要贡献者 微软对PostgreSQL贡献的很多新功能都来自于客户在使用微软Azure上的PostgreSQL管理实例数据库,所以这些新功能都来自于真实的客户需求 微软对P ...

- Win10 SFC& Dism修复系统

在Win10开始按钮上点击右键(或按Win + X快捷键),在弹出的系统快捷菜单中点击 Windows PowerShell(管理员)或者 命令提示符CMD (管理员) 方法 1 SFC输入&qu ...

- 4.elasticsearch中聚合查询

elasticsearch聚合查询 什么是聚合,就是目的不是查询具体的文档,而是查询文档的相关性,此外还可以对聚合的文档在按照其他维度再聚合. 包含以下四种聚合 Bucket Aggregation ...

- 十分钟教你在 k8s 中部署一个前后端应用

转载至我的博客https://www.infrastack.cn ,公众号:架构成长指南 大家好,我是蜗牛哥,好多开发人员,尤其是没接触过 k8s 的人员对如何在k8s中部署一个 前后端应用很模糊,不 ...

- 一行代码解决Three.js中只能在一侧看到物体的问题

项目场景: 因为该项目比较复杂庞大,在此就简单介绍一下: 通过Three.js创建若干个物体进行了组装,从而形成了一个类似眼球模拟模型的项目,用户可以通过拖动鼠标来达到控制视角(摄像机)的目的 ...

- 手把手教你使用ModelArts的自动学习识别毒蘑菇分类

摘要:本文介绍了ModelArts如何通过自动学习进行毒蘑菇的识别. 想当年,白雪公主吃了毒蘑菇,换来了白马王子的一吻.如果白雪公主没有吃毒蘑菇,还会遇到白马王子吗?张小白觉得不见得--说不定她会遇到 ...

- 从架构设计理念到集群部署,全面认识KubeEdge

摘要:本篇文章将从KubeEdge架构设计理念.KubeEdge代码目录概览.KubeEdge集群部署三方面带大家认识KubeEdge. KubeEdge即Kube+Edge,顾名思义就是依托K8s的 ...

- 云原生势不可挡,华为云GaussDB加速企业数字化转型

4月8日,华为云TechWave全球技术峰会在深圳成功举办,其中,在围绕"数据使能,驱动业务增长"为主题的数据使能分论坛会上,华为云GaussDB技术专家胡彦军现场分享了云原生数据 ...

- DamiBus v0.51 发布

DamiBus,专为本地多模块之间通讯解耦而设计(尤其是未知模块.隔离模块.领域模块).零依赖,特适合 DDD. 特点 结合 Bus 与 RPC 的概念,可作事件分发,可作接口调用,可作响应订阅. 支 ...