report_delay_calculation/check_timing/report_annotated_parasitics/report_analysis_coverge

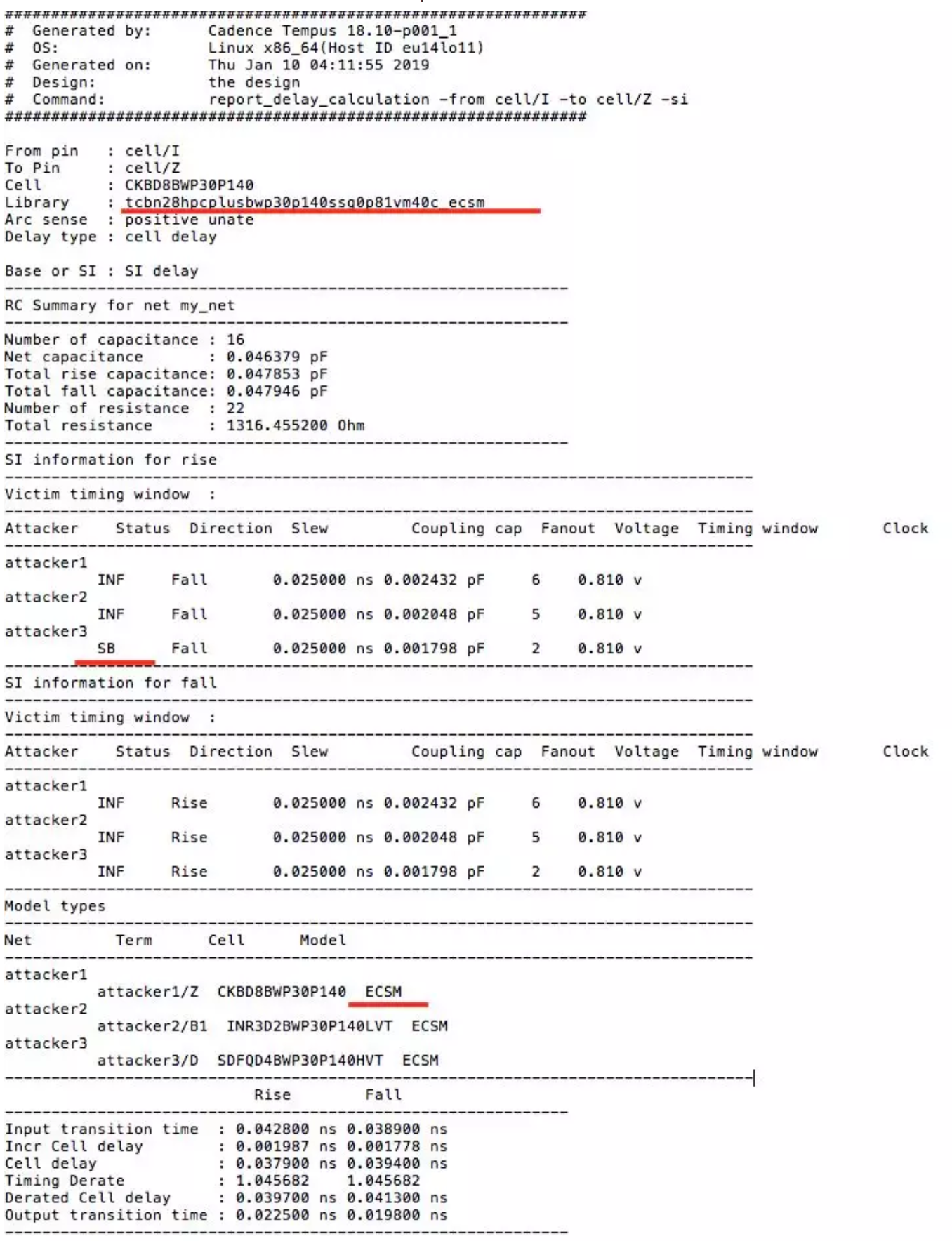

如何debug 一颗cell 或一段net 的delay, 常用的办法是用report_delay_calculation 报这颗cell 或这段net, 会得到形式如下的report, 从该report 中可以得到:

表头需要特别关注的是command, 确定report 的对象及加的option;

From/To pin: cell 的input pin 和 output pin;

Cell: 该cell 对应的lib cell;

Library: 该cell 来自哪个lib, 需要特别关注一下,确定用的lib 正确,避免低级错误;

Arc sense: Arc sense 分三种positive unate, negetive unate, non unate; 输出信号同输入信号跳变方向相同的称为positive unate 如buffer 的timing arc; 输出信号同输入信号跳变方向相反的称为negetive unate 如inverter 的timing arc; 输出信号的跳变方向由另一个输入信号的值决定称为non unate 如xor 的timing arc;

Delay type: 标示是cell delay 还是net delay;

Base or SI: 因为加了option -si, 所以当前是SI delay;

RC summary for net: 从这一块可以得到电容电阻个数、net 电容值、总上升电容值、总下降电容值、总电阻值。这部分信息在debug 不同工具间的correlation 时非常有用。

SI information: 从这一块可以得到所有的attacker 信息,及每个attcker 的status, direction, slew, coupling cap, fanout, voltage, timing window, clock. 另外还可以得到attacker 的model type 要特别注意用的是什么model, 是NLDM, CCS, ECSM, 示例中是ECSM, 这一点同样在debug 不同工具间的correlation 时至关重要。

delay information: 从这一块可以分别得到rise/fall 的输入transition, incr cell delay (由cross talk 造成的delay), cell delay, timing derate, derated cell delay, output transition.

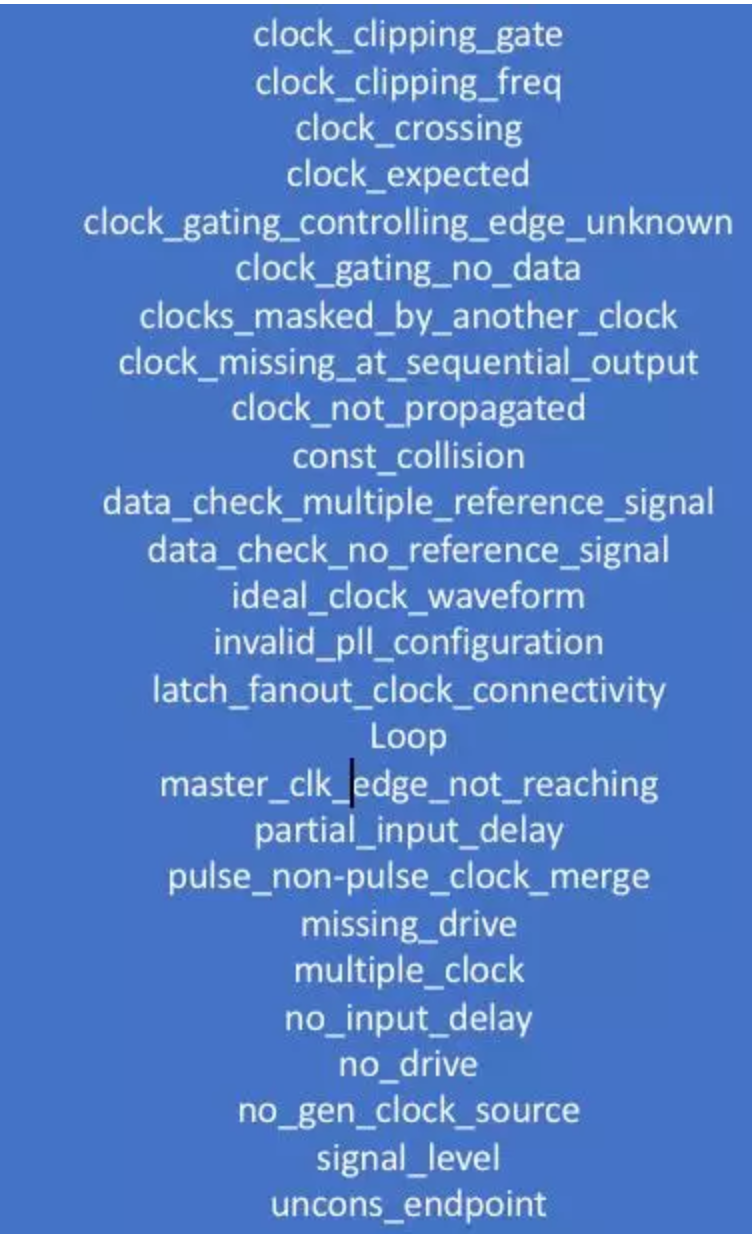

check_timing

用于check SDC 的quality, 会check 以下列出的内容,可以概括为:少了什么、多了什么、冲突了什么、错了什么;SDC 可以看作是STA 的『法规』,所以对制定者要高要求,STA 工具并不能check 出SDC 中所有的问题,有一些问题必须由设计者负责,如multi-cycle 设多少,写SDC 时是否手一抖把不该设false path 的地方设了false path, 这些人为大坑是STA 工具没办法check 到的。复杂SDC 的quality 通常需要用CDC 工具去做check, 除了SDC 本身还需要check 设计中是否放了正确的同步电路等。

需要对check_timing 报出的warning 做细致check, 把需要修的都修掉,可以忽略的都要有明确的原因。

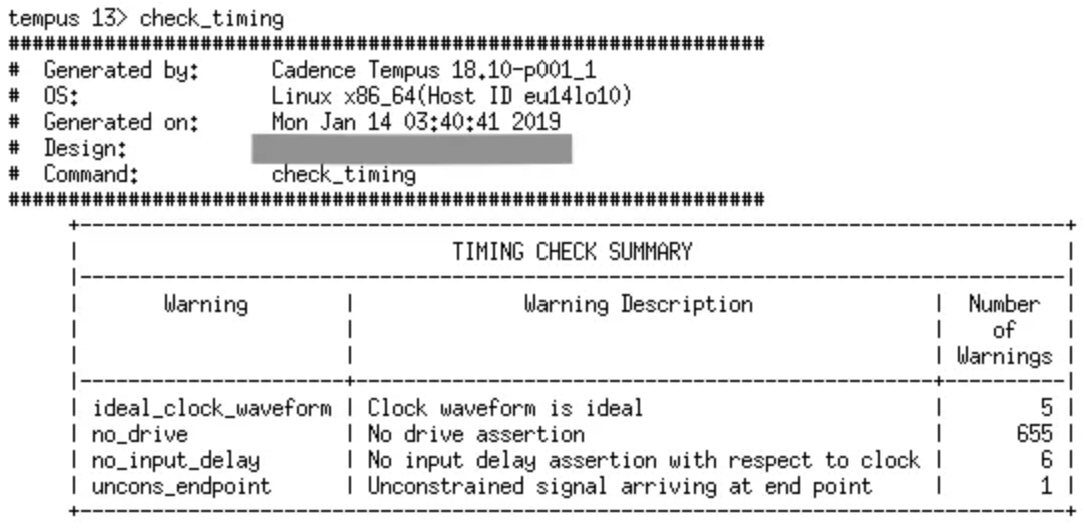

report_annotated_parasitics

用于check RC的反标情况,要保证所有的real net 都可以被正确反标上,如果有未反标的net, 需要去找抽RC 的坑友确认。首先确认数据是否匹配,再确认是否做了该做的change_name 动作,再确认除了real net 之外的其他warning, 为什么有assign 为什么有dangling net, 最好让坑友一齐处理掉,看着清爽。

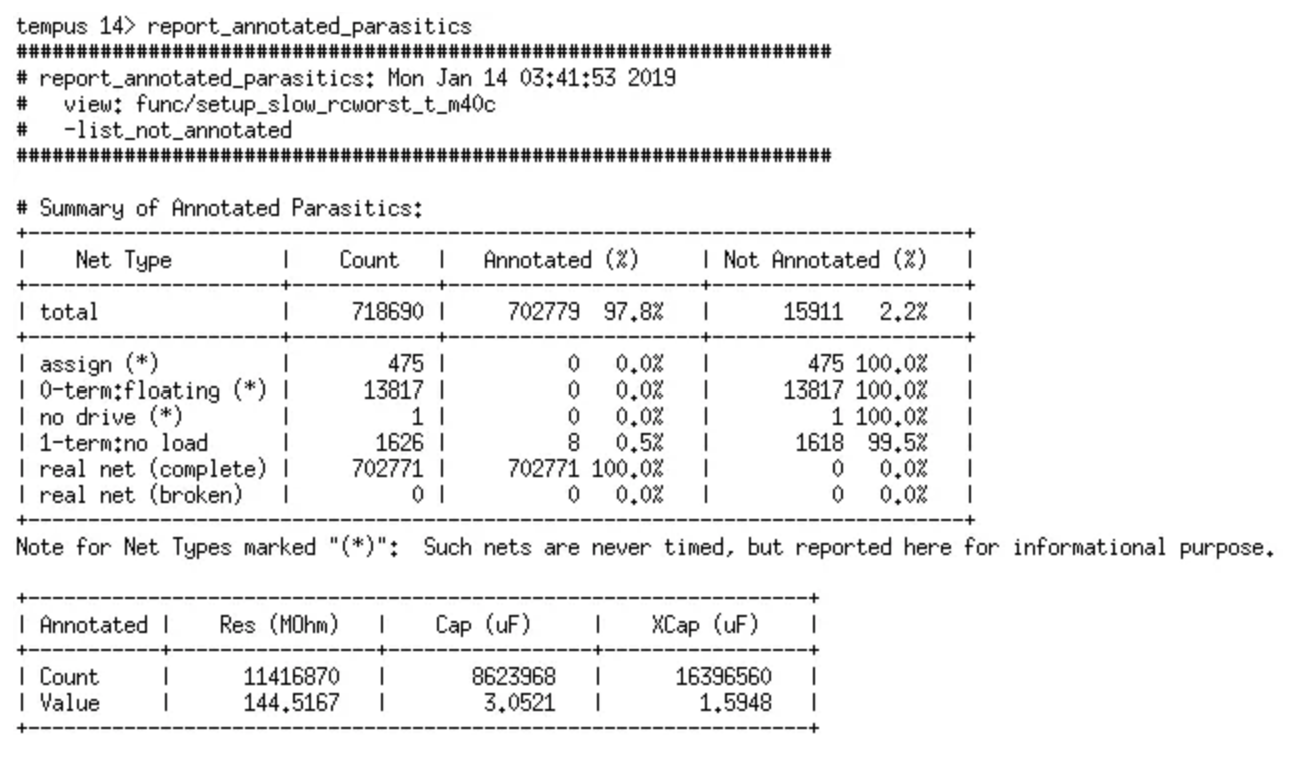

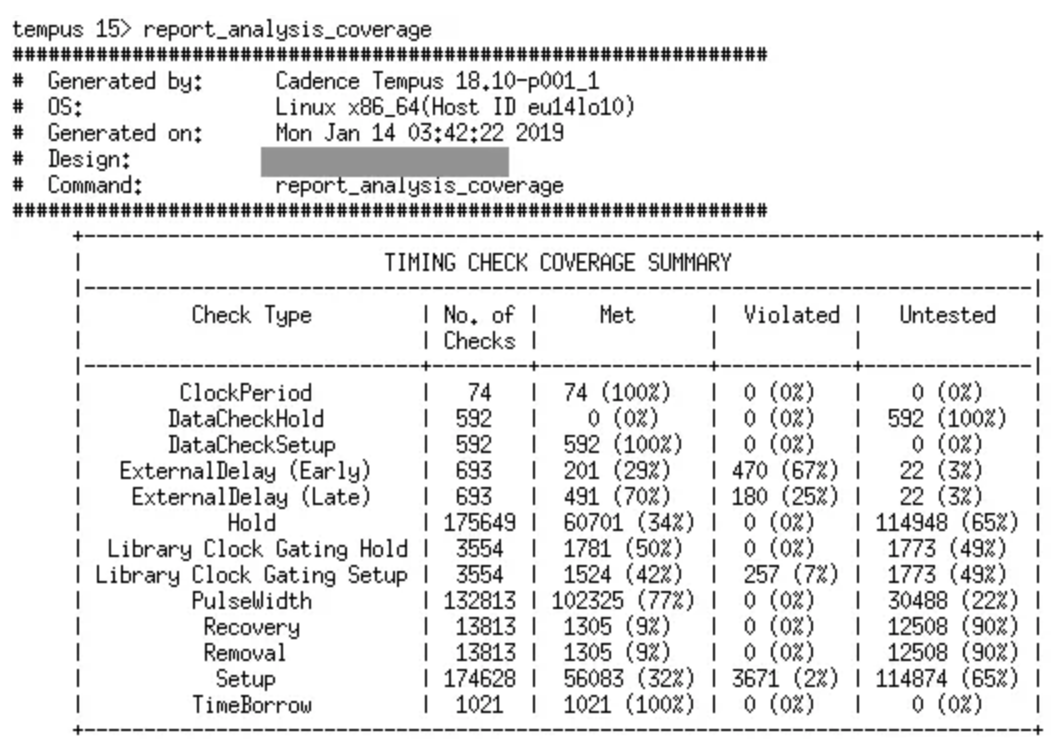

report_analysis_coverge

check STA coverge: check 设计中有多少需要check 的东西,在当前约束下,总共有多少被check 到了,多少没有被check 到,check 到的有哪些满足了需求有哪些没有满足。这个report 很重要,如果是初次分析最好把每一项的详细信息报出来,列一张表,对没有被check 到的部分进行分类,并对每一类归因。

Tempus 中分成以下几类check , 不同工具大同小异。

report_delay_calculation/check_timing/report_annotated_parasitics/report_analysis_coverge的更多相关文章

- Prime Time使用

PrimeTime一般用作sign off的timing check,也可用在DC之后的netlist的timing analysis 一般的使用流程: 1) Read design data,--- ...

- Timing path

Timing path:从register clock/input port开始,经过一些combinational logic,终止在register data/output port. PT以pa ...

- Tcl与Design Compiler (六)——基本的时序路径约束

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 时序约束可以很复杂,这 ...

- Tcl与Design Compiler (八)——DC的逻辑综合与优化

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 对进行时序路径.工作环 ...

- Tcl与Design Compiler (十二)——综合后处理

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 概述 前面也讲了一些综合后的需要进行的一些工作,这 ...

- Tcl与Design Compiler (十三)——Design Compliler中常用到的命令(示例)总结

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 本文将描述在Design Compliler中常用 ...

- Tcl与Design Compiler (五)——综合库(时序库)和DC的设计对象

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 前面一直说到综合库/工艺库这些东西,现在就来讲讲讲 ...

- Vivado Design Suite用户指南之约束的使用第二部分(约束方法论)

Constraints Methodology(约束方法论) 关于约束方法论 设计约束定义了编译流程必须满足的要求,以使设计在板上起作用. 并非所有步骤都使用所有约束在编译流程中. 例如,物理约束仅在 ...

- standard cell timing model

standard cell timing model 主要包括两方面的信息: Cell Delay calculation Output Transition calculation 首先,cel ...

随机推荐

- 互联网的“ip分组交换技术”

(1)从名字分析 从“ip分组交换”这个名字中,我们看看涉及哪些事情. 1)交换 主要涉及两类交换. · 交换机:负责网内部数据交换 · 路由器:负责网间的数据交换. ip分组交换技术的核心就是路由器 ...

- C++——指针4

8.对象指针 声明: 类名 *对象指针名 Point A(5,10): Point *ptr; ptr=&A;//通过指针访问对象成员:对象指针名->成员名.ptr->getX( ...

- PyQt5+Eric6开发的一个使用菜单栏、工具栏和状态栏的示例

前言 在做一个数据分析的桌面端程序遇到一些问题,这里简单整理下,分享出来供使用者参考. 1.网上查使用PyQt5工具栏的示例,发现很多只是一个简单的退出功能,如果有几个按钮如何处理?如何区分点击的究竟 ...

- Qt中的Label和PushButton背景图自动缩放设置

Label 背景图自动缩放 QPixmap* pixmap = new QPixmap(":/images/HeadIcon/1.png"); pixmap->scaled( ...

- fastadmin 框架中图片点击放大

fastadmin的原生图片预览,重新打开一个窗口太麻烦,使用layui做一个弹窗式的图片预览 1.将下面代码放在backend-init.js文件中 $('body').on('click', '[ ...

- 《NVM-Express-1_4-2019.06.10-Ratified》学习笔记(8.20)-- ANA

8.20 非对称namespace访问报告 8.20.1 非对称namespace访问报告概况 非对称Namespace访问(ANA)在如下场景下产生,基于访问这个namespace的controll ...

- sysbench下载与安装

目标:下载.安装sysbench软件,做数据库压测 准备: 在sysbench启动的linux机器上,首先安装好mysql,查看mysql已经启动 例如,在机器上已经安装完mysql,其路径为 /us ...

- pytest学习5-mark用例分类

使用Mark标记测试用例 通过使用pytest.mark你可以轻松地在测试用例上设置元数据.例如, 一些常用的内置标记: skip - 始终跳过该测试用例 skipif - 遇到特定情况跳过该测试用例 ...

- 【Python】字符串处理方法

- 训练20191005 2017-2018 ACM-ICPC Asia East Continent League Final

A 签到 M 签到 K 读懂后签到 L 博弈论 [引理]出现SXXS结构时后手必胜. 很容易发现n为奇数时后手不可能胜利,n为偶数时先手不可能胜利.n≤6时一定平局,n≥7时先手有可能胜利,n≥16时 ...