006 媒体独立接口(MII,Meida Independent Interface)

一、MII接口

MII接口Medium Independent Interface

MII(Media Independent Interface)即媒体独立接口,MII接口是MAC与PHY连接的标准接口。它是IEEE-802.3定义的以太网行业标准。MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接口支持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。"媒体独立"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。802.3协议最多支持32个PHY,但有一定的限制:要符合协议要求的connector特性。

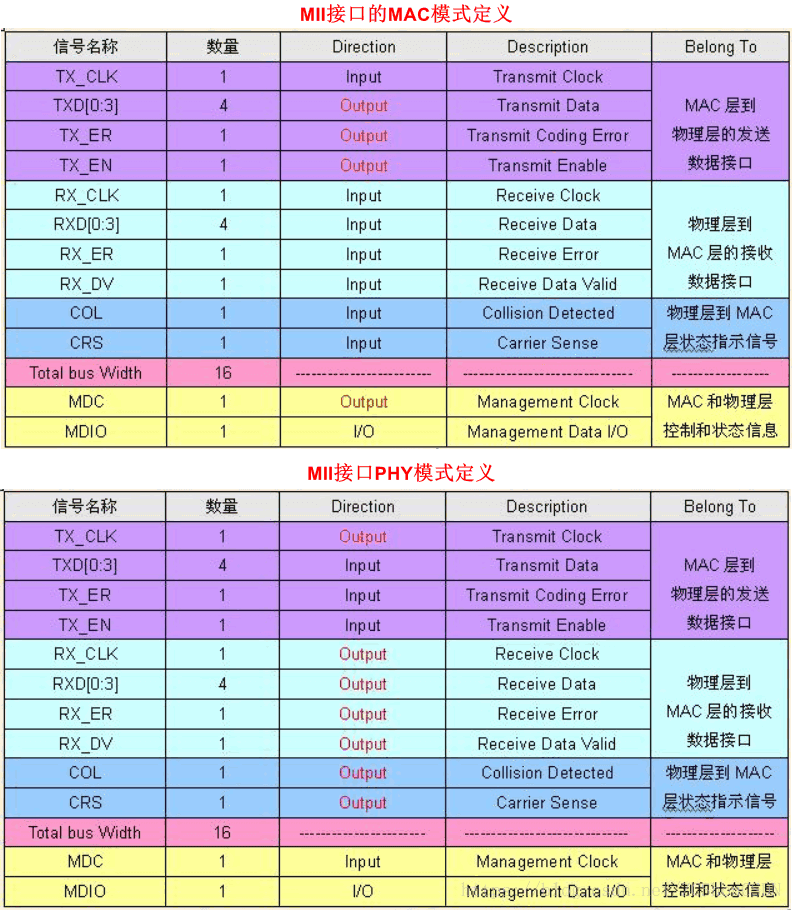

MII数据接口包含16个信号和2个管理接口信号,如下图所示:

提到MII,就有可能涉及到RS,PLS,STA等名词术语,下面讲一下他们之间对应的关系。

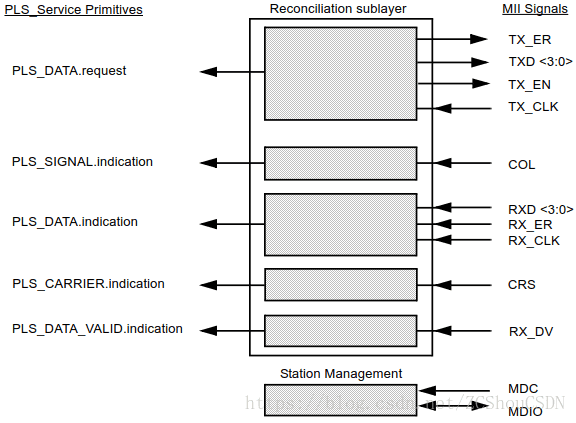

所谓RS即Reconciliation sublayer,它的主要功能主要是提供一种MII和MAC/PLS之间的信号映射机制。它们(RS与MII)之间的关系如下图:

MII的Management Interface是与STA(Station Management)相连的。

关于本节,具体可参考IEEE以太网标准802.3的22.3 Signal timing characteristics节,其中包含时钟信号等更详细内容。

MII接口主要包括四个部分。一是从MAC层到PHY层的发送数据接口,二是从PHY层到MAC层的接收数据接口,三是从PHY层到MAC层的状态指示信号,四是MAC层和PHY层之间传送控制和状态信息的MDIO接口。

MII包括一个数据接口,以及一个MAC和PHY之间的管理接口:

数据接口: 包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括

TX_ER(transmit coding error): TX_ER同步于TX_CLK,在数据传输过程中,如果TX_ER有效超过一个时钟周期,并且此时TX_EN是有效的,则数据通道中传输的数据是无效的,没用的。注:当TX_ER有效并不影响工作在10Mb/s的PHY或者TX_EN无效时的数据传输。在MII接口的连线中,如果TX_ER信号线没有用到,必须将它下拉接地。

TXD<3:0>(transmit data): TXD由RS驱动,同步于TX_CLK,在TX_CLK的时钟周期内,并且TX_EN有效,TXD上的数据被PHY接收,否则TXD的数据对PHY没有任何影响。

TX_EN: 发送使能。TX_EN由Reconciliation子层根据TX_CLK上升沿同步进行转换,时序如图22-16所示。

TX_CLK(transmit clock): TX_CLK (Transmit Clock)是一个连续的时钟信号(即系统启动,该信号就一直存在),它是TX_EN, TXD, and TX_ER(信号方向为从RS到PHY)的参考时钟,TX_CLK由PHY驱动TX_CLK的时钟频率是数据传输速率的25%,偏差±100ppm。例如,100Mb/s模式下,TX_CLK时钟频率为25MHz,占空比在35%至65%之间。

COL(collision detected): COL不需要同步于参考时钟。The behavior of the COL signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation。即半双工模式信号有效,全双工模式信号无效。

RXD<3:0>(receive data): RXD由RS驱动,同步于RX_CLK,在RX_CLK的时钟周期内,并且RX_DV有效,RXD上的数据被RS接收,否则RXD的数据对RS没有任何影响。While RX_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX_ER signal while driving the value <1110> onto RXD<3:0>。

RX_ER(receive error): RX_ER同步于RX_CLK,其在RX通道中的作用类似于TX_ER对于TX通道数据传输的影响。

RX_CLK: 它与TX_CLK具有相同的要求,所不同的是它是RX_DV, RXD, and RX_ER(信号方向是从PHY到RS)的参考时钟。RX_CLK同样是由PHY驱动,PHY可能从接收到的数据中提取时钟RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK。

CRS(carrier sense): CRS不需要同步于参考时钟,只要通道存在发送或者接收过程,CRS就需要有效。The behavior of the CRS signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation,即半双工模式信号有效,全双工模式信号无效。

RX_DV(Receive Data Valid): RXD_DV同步于RX_CLK,被PHY驱动,它的作用如同于发送通道中的TX_EN,不同的是在时序上稍有一点差别:为了让数据能够成功被RS接收,要求RXD_DV有效的时间必须覆盖整个FRAME的过程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。

MII管理接口: 是个双信号接口,通过管理接口,MAC就能监视和控制PHY。其管理是使用SMI(Serial Management Interface) 总线通过读写PHY的寄存器来完成的。一个是时钟信号(***MDC (management data clock)***)。另一个是数据信号(***MDIO (management data input/output)***)。

MDC: 由站管理实体向PHY提供,作为在MDIO信号上传送信息的定时参考。 MDC是一种非周期性的信号,没有最高或最低时间。 无论TX_CLK和RX_CLK的标称周期如何,MDC的最小高低时间应为160 ns,MDC的最小周期为400 ns。

MDIO: 是PHY和STA之间的双向信号。 它用于在PHY和STA之间传输控制信息和状态。 控制信息由STA同步地针对MDC驱动并且由PHY同步地采样。 状态信息由PHY针对MDC同步驱动并由STA同步采样。

MII接口信号定义如下:

| 信号名称 | 描述 | 方向 |

|---|---|---|

| TX_CLK | 发送时钟 | PHY → MAC |

| TX_ER | 发送数据错误 | MAC → PHY |

| TX_EN | 发送使能 | MAC → PHY |

| TXD0 | 发送数据位0(最先传输) | MAC → PHY |

| TXD1 | 发送数据位1 | MAC → PHY |

| TXD2 | 发送数据位2 | MAC → PHY |

| TXD3 | 发送数据位3 | MAC → PHY |

| RX_CLK | 接收时钟 | PHY → MAC |

| RX_DV | 接收数据有效 | PHY → MAC |

| RX_ER | 接收数据错误 | PHY → MAC |

| RXD0 | 接收数据位0(最先传输) | PHY → MAC |

| RXD1 | 接收数据位1 | PHY → MAC |

| RXD2 | 接收数据位2 | PHY → MAC |

| RXD3 | 接收数据位3 | PHY → MAC |

| CRS | 载波监测 | PHY → MAC |

| COL | 冲突碰撞监测 | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

MAC 通过MIIM 接口读取PHY 状态寄存器以得知目前PHY 的状态。例如连接速度、双工的能力等。也可以通过 MIIM设置PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。当时钟频率为2.5MHz时,对应速率为10Mb/s。

PHY 里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC 通过SMI 总线不断的读取PHY 的状态寄存器以得知目前PHY 的状态。例如连接速度、双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是由IEEE的规范的。因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

MII支持10Mbps和100Mbps的操作,一个接口由14根线组成,它的支持还是比较灵活的。但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线。一般按照这个接口做交换机是不太现实的。所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

二、RMII,SMII,GMII,RGMII

RMII

RMII(Reduced Media Independant Interface)

简化媒体独立接口是标准的以太网接口之一,比MII有更少的I/O传输。RMII收发使用2位数据进行传输,收发时钟均采用50MHz时钟源。

RMII口是用两根线来传输数据的,MII口是用4根线来传输数据的,GMII是用8根线来传输数据的。MII/RMII只是一种接口,对于10Mbps线速,MII的时钟速率是2.5MHz就可以了,RMII则需要5MHz;对于100Mbps线速,MII需要的时钟速率是25MHz,RMII则是50MHz。

MII/RMII用于传输以太网包,在MII/RMII接口是4/2bit的,在以太网的PHY里需要做串并转换,编解码等才能在双绞线和光纤上进行传输,其帧格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。以太网帧的格式为:前导符+开始位+目的mac地址+源mac地址+类型/长度+数据+padding(optional)+32bitCRC。如果有vlan,则要在类型/长度后面加上2个字节的vlan tag,其中12bit来表示vlan id,另外4bit表示数据的优先级!

RMII接口信号定义如下:

| 信号名称 | 描述 | 方向 |

|---|---|---|

| REF_CLK | 参考时钟 | MAC→PHY或由外部时钟源提供 |

| TX_EN | 发送数据使能 | MAC → PHY |

| TXD0 | 发送数据位0(最先传输) | MAC → PHY |

| TXD1 | 发送数据位1 | MAC → PHY |

| RX_ER | 接收错误 | PHY → MAC |

| RXD0 | 接收数据位0(最先传输) | PHY → MAC |

| RXD1 | 接收数据1 | PHY → MAC |

| CRS_DV | 载波和接收数据有效 | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

其中CRS_DV是MII中RX_DV和CRS两个信号的合并,当物理层接收到载波信号后CRS_DV变得有效,将数据发送给RXD。当载波信号消失后,CRS_DV会变为无效。在100M以太网速率中,MAC层每个时钟采样一次RXD[1:0]上的数据,在10M以太网速率中,MAC层每10个时钟采样一次RXD[1:0]上的数据,此时物理层接收的每个数据会在RXD[1:0]保留10个时钟。

SMII

SMII(Serial Media Independant Interface),串行MII接口。它包括TXD,RXD,SYNC三个信号线,共用一个时钟信号,此时钟信号是125MHz,信号线与此时钟同步。信号定义如下:

| 信号名称 | 描述 | 方向 |

|---|---|---|

| REF_CLK | 参考时钟 | 外部时钟源提供125MHz |

| TXD | 发送数据 | MAC → PHY |

| RXD | 接收数据 | PHY → MAC |

| SYNC | 同步信号 | - |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

SYNC是数据收发的同步信号,每10个时钟同步置高一次电平,表示同步。TXD和RXD上的数据和控制信息,以10bit为一组。发送部分波形如下:

从波形可以看出,SYNC变高后的10个时钟周期内,TXD依次输出一组10bit的数据即TX_ER,TX_EN,TXD[0:7],这些控制信息和MII接口含义相同。在100M速率中,每一组的内容都是变换的,在10M速率中,每一组数据需要重复10次,采样任一一组都可以。

GMII

GMII(Gigabit Media Independant Interface),千兆MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。GMII接口数据结构符合IEEE以太网标准,该接口定义见IEEE 802.3-2000。

发送器: 在千兆速率下,向PHY提供GTXCLK信号、TXD、TXEN、TXER信号与此时钟信号同步。否则在10/100Mbps速率下,PHY提供TXCLK时钟信号,其它信号与此信号同步。其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

GTXCLK——吉比特TX…信号的时钟信号(125MHz)

TXCLK——10/100Mbps信号时钟

TXD[7…0]——被发送数据

TXEN——发送器使能信号

TXER——发送器错误(用于破坏一个数据包)

接收器:

RXCLK——接收时钟信号(从收到的数据中提取,因此与GTXCLK无关联)

RXD[7…0]——接收数据

RXDV——接收数据有效指示

RXER——接收数据出错指示

COL——冲突检测(仅用于半双工状态)

管理配置: 管理配置接口控制PHY的特性。该接口有32个寄存器地址,每个地址16位。其中前16个已经在“IEEE 802.3,2000-22.2.4 Management Functions”中规定了用途,其余的则由各器件自己指定。

MDC——配置接口时钟

MDIO——配置接口I/O

GMII信号定义如下:

| 信号名称 | 描述 | 方向 |

|---|---|---|

| GTX_CLK | 1000M发送时钟 | MAC → PHY |

| TX_CLK | 100/10M发送时钟 | MAC → PHY |

| TX_ER | 发送数据错误 | MAC → PHY |

| TX_EN | 发送使能 | MAC → PHY |

| TX_[7:0] | 发送数据8bit | MAC → PHY |

| RX_CLK | 接收时钟 | PHY → MAC |

| RX_DV | 接收数据有效 | PHY → MAC |

| RX_ER | 接收数据错误 | PHY → MAC |

| RX_[7:0] | 接收数据8bit | PHY → MAC |

| CRS | 载波监测 | PHY → MAC |

| COL | 冲突碰撞监测(仅用于半双工状态) | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

RGMII

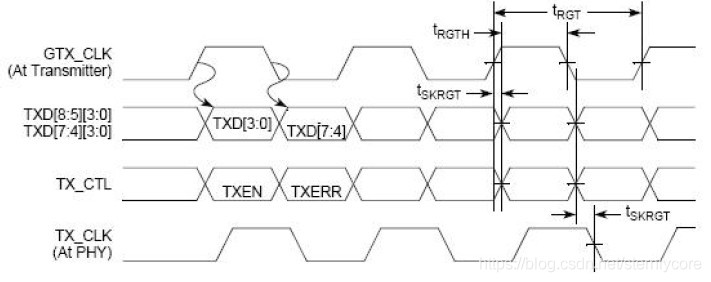

RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

- 发送/接收数据线由8条改为4条

- TX_ER和TX_EN复用,通过TX_CTL传送

- RX_ER与RX_DV复用,通过RX_CTL传送

- 1 Gbit/s速率下,时钟频率为125MHz

- 100 Mbit/s速率下,时钟频率为25MHz

- 10 Mbit/s速率下,时钟频率为2.5MHz

信号定义如下:

| 信号名称 | 描述 | 方向 |

|---|---|---|

| TXC | 发送时钟 | MAC→PHY |

| TX_CTL | 发送数据控制 | MAC → PHY |

| TXD[3:0] | 发送数据4bit | MAC → PHY |

| RXC | 接收时钟 | PHY → MAC |

| RX_CTL | 接收数据控制 | PHY → MAC |

| RXD[3:0] | 接收数据4bit | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

虽然RGMII信号线减半,但TXC/RXC时钟仍为125Mhz,为了达到1000Mbit的传输速率,TXD/RXD信号线在时钟上升沿发送接收GMII接口中的TXD[3:0]/RXD[3:0],在时钟下降沿发送接收TXD[7:4]/RXD[7:4],并且信号TX_CTL反应了TX_EN和TX_ER状态,即在TXC上升沿发送TX_EN,下降沿发送TX_ER,同样的道理试用于RX_CTL,下图为发送接收的时序:

三、MII接口对比

表8‑2 MII接口对比

|

简述 |

Pins |

速率计算 |

|

|

MII |

基本的100Mbps/10Mbps接口 |

RXD[3:0]、TXD[3:0] TX_ER、TX_EN RX_ER、RX_DV TX_CLK、RX_CLK CRS、COL |

Clock=25MHz or 2.5MHz 数据位宽4bit(一个时钟周期传输4bit数据) 100Mbps=25 MHz *4bit 10Mbps=2.5 MHz *4bit |

|

RMII |

在MII基础上精简的100Mbps/10Mbps接口; 通过提升Clock频率保持与MII一样的速率; |

RXD[1:0]、TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV |

Clock=50MHz 数据位宽2bit(一个时钟周期传输2bit数据) 100Mbps=50 MHz *2bit 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=50MHz/10*2bit |

|

SMII |

串行MII 100Mbps/10Mbps接口; 进一步提升Clock频率保持与MII一样的速率; |

RXD[1:0] TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV |

Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 计算有效带宽时需要去掉控制位 100Mbps=125 MHz *(8bit/10bit) 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=(125 MHz/10)*(8bit/10bit) |

|

GMII |

在MII接口基础上提升了数据位宽和Clock频率成为1000Mbps接口 |

RXD[7:0]、TXD[7:0] TX_ER、TX_EN RX_ER、RX_DV GTX_CLK、RX_CLK CRS、COL |

Clock=125MHz 数据位宽8bit(一个时钟周期传输8bit数据) 1000Mbps=125 MHz *8bit |

|

RGMII |

GMII的简化版本 |

RXD[3:0]、TXD[3:0] TX_EN RX_DV TX_CLK、RX_CLK CRS、COL |

Clock=125MHz 数据位宽4bit(一个时钟周期里,上升沿取TX\RX的0-3bit,下降沿取TX\RX的4-7bit,所以实际还是在一个时钟周期里传输8bit数据) 1000Mbps=125 MHz *8bit 100Mbps=25 MHz *8bit 10Mbps=2.5MHz *8bit |

|

SGMII |

串行GMII,在此基础上提升了时钟频率达到1000Mbps |

RXD[0]、TXD[0] RX_CLK |

Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 计算有效带宽时需要去掉控制位 1000Mbps=125 0MHz *(8bit/10bit) |

MII接口直接的区别与联系通过上表很容易进行区分。

四、参考资料

1、微信公众号OpenFPGA,https://mp.weixin.qq.com/s/B84yB2LkSfl4KTdgypS4hg

2、https://blog.csdn.net/ChenGuiGan/article/details/108603550

3、https://blog.csdn.net/zcshoucsdn/article/details/80090802#comments

006 媒体独立接口(MII,Meida Independent Interface)的更多相关文章

- 接口分离原则(Interface Segregation Principle)

接口分离原则(Interface Segregation Principle)用于处理胖接口(fat interface)所带来的问题.如果类的接口定义暴露了过多的行为,则说明这个类的接口定义内聚程度 ...

- 接口隔离原则(Interface Segregation Principle,ISP)

接口隔离原则: 1.使用多个专门的接口比使用单一的总接口要好. 2.一个类对另外一个类的依赖性应当是建立在最小的接口上的. 3.一个接口代表一个角色,不应当将不同的角色都交给一个接口.没有关系的接口合 ...

- 北风设计模式课程---接口分离原则(Interface Segregation Principle)

北风设计模式课程---接口分离原则(Interface Segregation Principle) 一.总结 一句话总结: 接口分离原则描述为 "客户类不应被强迫依赖那些它们不需要的接口& ...

- 【原创】Odoo开发文档学习之:构建接口扩展(Building Interface Extensions)(边Google翻译边学习)

构建接口扩展(Building Interface Extensions) 本指南是关于为Odoo的web客户创建模块. 要创建有Odoo的网站,请参见建立网站;要添加业务功能或扩展Odoo的现有业务 ...

- 接口隔离原则(Interface Segregation Principle)ISP

using System; using System.Collections.Generic; using System.Text; namespace InterfaceSegregationPri ...

- 【设计模式六大原则4】接口隔离原则(Interface Segregation Principle)

定义:客户端不应该依赖它不需要的接口:一个类对另一个类的依赖应该建立在最小的接口上. 问题由来:类A通过接口I依赖类B,类C通过接口I依赖类D,如果接口I对于类A和类B来说不是最小接口,则类B和类 ...

- 设计模式六大原则(4):接口隔离原则(Interface Segregation Principle)

接口隔离原则: 使用多个专门的接口比使用单一的总接口要好. 一个类对另外一个类的依赖性应当是建立在最小的接口上的. 一个接口代表一个角色,不应当将不同的角色都交给一个接口.没有关系的接口合并在一起,形 ...

- 面象对象设计原则之四:接口隔离原则(The Interface Segregation Principle,ISP)

接口隔离原则定义如下: 接口隔离原则(Interface Segregation Principle, ISP):使用多个专门的接口,而不使用单一的总接口,即客户端不应该依赖那些它不需要的接口. 根 ...

- 4.接口隔离原则(Interface Segregation Principle)

1.定义 客户端不应该依赖它不需要的接口: 一个类对另一个类的依赖应该建立在最小的接口上. 2.定义解读 定义包含三层含义: 一个类对另一个类的依赖应该建立在最小的接口上: 一个接口代表一个角色,不应 ...

随机推荐

- Java的反射机制一

Java具有一定的动态性,我们可以利用反射机制,字节码操作来获得类似动态语言的特性. 动态操作对象,构造方法,属性,方法 Demo2 如何取得属性和方法以及构造器 public class Demo2 ...

- MYSQL_Join注入技巧

Join注入技巧 join无名列报错注入 约束条件 在知到表名的前提下才能操作 注入语句 and extractvalue(1,concat(0x7e,(select * from (select * ...

- CF1539A Contest Start[题解]

Contest Start 题目大意 有 \(n\) 个人报名参加一个比赛,从 \(0\) 时刻开始每隔 \(x\) 分钟有一个人开始比赛,每个人参赛时间相同,均为 \(t\) .定义一个选手的不满意 ...

- VBA收集

EXCEL启用宏 1.excel另存为"启用宏的XLSM"的文件格式 excel2007打开显示"宏的工具栏" 点击"左上角的OFFICE按钮&quo ...

- Kubernetes部署-二进制方式

环境配置 一.系统环境 序号 用途 系统 Docker版本 IP地址 1 Master CentOS Linux release 7.6.1810 (Core) 19.03.4 192.168.0.1 ...

- Eclipse配置反编译插件jadclipse

参考自:https://blog.csdn.net/moneyshi/article/details/79715891 Jad是一个Java的一个反编译工具,是用命令行执行,和通常JDK自带的java ...

- 【转载】PHP 程序员进阶之路

原文:没有Nginx,你还能做什么? PHP程序员的未来不是Java,Java拯救不了你. 已经1368年了,你扪胸自问,没有了Nginx的你,还能用PHP做什么.有一些高端的刁民会愤怒地说:&quo ...

- 【洛谷P1318积水面积】最小生成树

我写一篇绝对原创的题解,算法原创,求洛谷通过!!!(让更多人看到这篇题解) 绝大多数人肯定认为这道题是一道模拟题 以下为正解 我们来看一下这一道题,其实就是找到左右高点,在模拟. 但是这个是正常人的想 ...

- git教程和命令集合

详细教程可参考 git community book中文版 git教程(廖雪峰) 安装 官网下载git安装包,进行安装即可: 打开cmd终端,输入 "git --version", ...

- SpringMVC 参数中接收之一 List

作者:张艳涛 time:2020-07-31 SpingMVC 一.前台传数组,SpingMVC用addusers(@RequestBody List<UserPojo> userlist ...