基于Verilog的按键检测实验

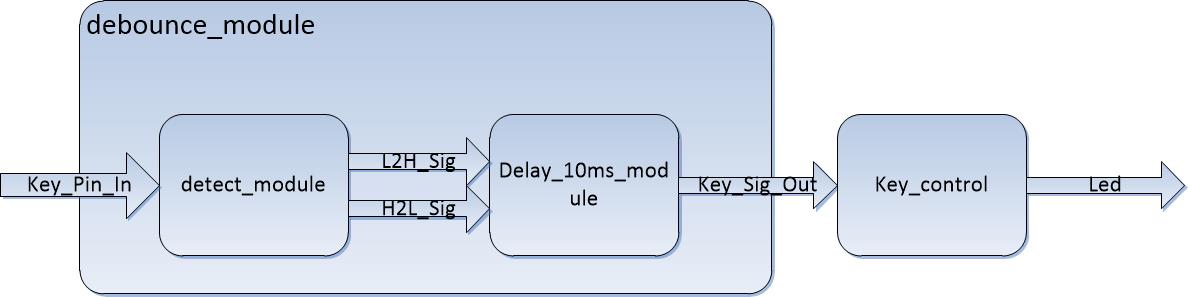

一、模块框图及基本思路

detect_module:检测按键输入脚的电平边沿变化

delay_10ms_module:延时消抖,输出按键有效信号

debounce_module:前两个模块的组合模块

key_control:按键信号控制Led

key_demo:顶层模块

二、软件部分

detect_module.v

module detect_module(

CLK,RSTn,

Key_Pin_In,

H2L_Sig,L2H_Sig

);

input CLK,RSTn;

input Key_Pin_In;

output H2L_Sig,L2H_Sig; /****************************************************/

localparam T100us=50_000_000/1_000_000*-;

reg [:] Count_100us;

reg isEn; always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

Count_100us<='d0;

isEn<='b0;

end

else if(Count_100us==T100us)

isEn<='b1;

else Count_100us<=Count_100us+'b1;

end /****************************************************/

reg H2L_Sig_r1,H2L_Sig_r2;

reg L2H_Sig_r1,L2H_Sig_r2;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

H2L_Sig_r1<='b1;

H2L_Sig_r2<='b1;

L2H_Sig_r1<='b0;

L2H_Sig_r2<='b0;

end

else

begin

H2L_Sig_r1<=Key_Pin_In;

H2L_Sig_r2<=H2L_Sig_r1;

L2H_Sig_r1<=Key_Pin_In;

L2H_Sig_r2<=L2H_Sig_r1;

end

end /****************************************************/ assign H2L_Sig=isEn?(H2L_Sig_

delay_10ms_module.v

module delay10ms_module(

CLK,RSTn,

H2L_Sig,L2H_Sig,

Key_Sig_Out

);

input CLK,RSTn;

input H2L_Sig,L2H_Sig;

output Key_Sig_Out; /**********************************************/

localparam T10ms=50_000_000/*-;

reg[:] Count_10ms;

reg isCount;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

Count_10ms<='d0;

end

else if(Count_10ms==T10ms) Count_10ms<='d0;

else if(isCount) Count_10ms<=Count_10ms+'b1;

end /**********************************************/

reg Key_Sig_Out_r;

reg [:]i;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

Key_Sig_Out_r<=;

i<=;

isCount<='b0;

end

else

case(i)

'd0:if(H2L_Sig) i<=2'd1;

else if(L2H_Sig) i<='d2;

'd1:if(Count_10ms==T10ms) begin Key_Sig_Out_r<=1'b1;isCount<='b0;i<=2'd0;end

else isCount<='b1;

'd2:if(Count_10ms==T10ms) begin Key_Sig_Out_r<=1'b0;isCount<='b0;i<=2'd0;end

else isCount<='b1; endcase

end

/***************************************************/

assign Key_Sig_Out=Key_Sig_Out_r; endmodule

debounce_module.v

module debounce_module(

CLK,RSTn,

Key_Pin_In,

Key_Sig_Out

);

input CLK,RSTn;

input Key_Pin_In;

output Key_Sig_Out; wire H2L_Sig;

wire L2H_Sig; detect_module U0(

.CLK(CLK),

.RSTn(RSTn),

.Key_Pin_In(Key_Pin_In),

.H2L_Sig(H2L_Sig),

.L2H_Sig(L2H_Sig)

);

delay10ms_module U1(

.CLK(CLK),

.RSTn(RSTn),

.H2L_Sig(H2L_Sig),

.L2H_Sig(L2H_Sig),

.Key_Sig_Out(Key_Sig_Out)

); endmodule

key_control.v

module key_control(

CLK,RSTn,

Key_Sig,

Led

);

input CLK,RSTn;

input Key_Sig;

output Led; /***********************************/

reg Key_Sig_r1,Key_Sig_r2;

wire Led_Sig;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

Key_Sig_r1<='b0;

Key_Sig_r2<='b0;

end

else

begin

Key_Sig_r1<=Key_Sig;

Key_Sig_r2<=Key_Sig_r1;

end

end

assign Led_Sig=Key_Sig_r1&!Key_Sig_r2;

/************************************/

reg rLed;

always @(posedge CLK or negedge RSTn )

begin

if(!RSTn) rLed<='b0;

else if(Led_Sig) rLed<=~rLed;

end

assign Led=rLed;

endmodule

key_demo.v

module key_demo(

CLK,RSTn,

Key_Pin_In,Led

);

input CLK,RSTn;

input [:]Key_Pin_In;

output [:]Led; wire Key_Sig1;

key_control U0 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Sig(Key_Sig1),

.Led(Led[])

);

debounce_module U1 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Pin_In(Key_Pin_In[]),

.Key_Sig_Out(Key_Sig1)

); wire Key_Sig2;

key_control U2 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Sig(Key_Sig2),

.Led(Led[])

);

debounce_module U3 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Pin_In(Key_Pin_In[]),

.Key_Sig_Out(Key_Sig2)

); wire Key_Sig3;

key_control U4 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Sig(Key_Sig3),

.Led(Led[])

);

debounce_module U5 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Pin_In(Key_Pin_In[]),

.Key_Sig_Out(Key_Sig3)

); wire Key_Sig4;

key_control U6 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Sig(Key_Sig4),

.Led(Led[])

);

debounce_module U7 (

.CLK(CLK),

.RSTn(RSTn),

.Key_Pin_In(Key_Pin_In[]),

.Key_Sig_Out(Key_Sig4)

); endmodule

三、硬件部分

黑金SPARTAN-6开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3; NET "Led[0]" LOC = P4;

NET "Led[1]" LOC = N5;

NET "Led[2]" LOC = P5;

NET "Led[3]" LOC = M6; NET "Key_Pin_In[0]" LOC = C3;

NET "Key_Pin_In[1]" LOC = D3;

NET "Key_Pin_In[2]" LOC = E4;

NET "Key_Pin_In[3]" LOC = E3;

基于Verilog的按键检测实验的更多相关文章

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 第33章 TIM—电容按键检测—零死角玩转STM32-F429系列

第33章 TIM—电容按键检测 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/fir ...

- zigbee学习之路(十五):基于协议栈的按键实验

一.前言 经过上次的学习,相信大家已经初步学会使用zigbee协议进行发送和接受数据了.今天,我们要进行的实验是按键的实验,学会如何在协议栈里实现按键中断. 二.实验功能 在协议栈上实现按键中断,BU ...

- 基于Arduino的按键控制LED实验

I/O 口的意思即为INPUT 接口和OUTPUT 接口,到目前为止我们设计的小灯实验都还只是应用到Arduino 的I/O 口的输出功能,这个实验我们来尝试一下使用Arduino的I/O 口的输入功 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于FPGA的按键扫描程序

最近在学习FPGA,就试着写了个按键扫描的程序.虽说有过基于单片机的按键扫描处理经验,对于按键的处理还是有一些概念.但是单片机程序的编写通常都采用C写,也有用汇编,而FPGA却是采用VHDL或者Ver ...

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

随机推荐

- 键盘录入一个文件夹路径,统计该文件夹(包含子文件夹)中每种类型的文件及个数,注意:用文件类型(后缀名,不包含.(点),如:"java","txt")作为key, 用个数作为value,放入到map集合中,遍历map集合

package cn.it.zuoye5; import java.io.File;import java.util.HashMap;import java.util.Iterator;import ...

- 什么是DNS攻击?它是如何工作的?

什么是DNS攻击?它是如何工作的? DNS攻击是一种利用域名系统中的弱点或漏洞的网络攻击.今天,互联网已成为我们生活中不可或缺的一部分.从社交到金融.购物再到旅游,我们生活的方方面面都是互联网.由于互 ...

- CSS 内边距 外边距

CSS 内边距 外边距 <html> <!-- style="margin: 0 auto" 将网页上方空白边距填满--> <body style=& ...

- EJB到底是什么?

EJB到底是什么? 1. 我们不禁要问,什么是"服务集群"?什么是"企业级开发"? 既然说了EJB 是为了"服务集群"和"企业 ...

- Win32汇编学习(11):对话框(2)

我们将进一步学习对话框,探讨如何把对话框当成输入设备.如果您看了前一篇文章,那就会发现这次的例子只有少量的改动,就是把我们的对话框窗口附属到主窗口上.另外,我们还要学习通用对话框的用法. 理论: 把对 ...

- NodeJS:(一)特性&环境&测试

特性: ①非阻塞I/O,事件驱动,单线程 非阻塞I/O:进程不等I/O完成(阻塞是等I/O完成后才进行下一步) 事件驱动:异步操作结束后通知 ②优点 前端职责范围变大,统一开发体验 处理高并发(单位时 ...

- robot framework学习二-----元素定位

文章摘自:https://www.cnblogs.com/fnng/p/3901391.html 不要误认为Robot framework 只是个web UI测试工具,更正确的理解Robot fram ...

- Entity Framework框架 (二)

一.前面一篇EF的介绍主要是通过linq语句,本篇主要是介绍一下不通过linq语句如何去操作EF执行查询sql语句与执行存储过程. 1. 其中的Acccout是输出参数对应的类.比如输出参数有三个值 ...

- html css js 细节

细节1 1.Chrome中文界面下会将小于12px的字体默认显示为12px,解决方法:在CSS中加入-webkit-text-size-adjust:none; 2.link可以加载除CSS以外的其他 ...

- ranch 源码分析(三)

接上ranch 源码分析(二) 上次讲到了ranch_conns_sup和ranch_acceptors_sup这2个ranch的核心模块,我们接着分析 首先查看ranch_conns_sup.erl ...