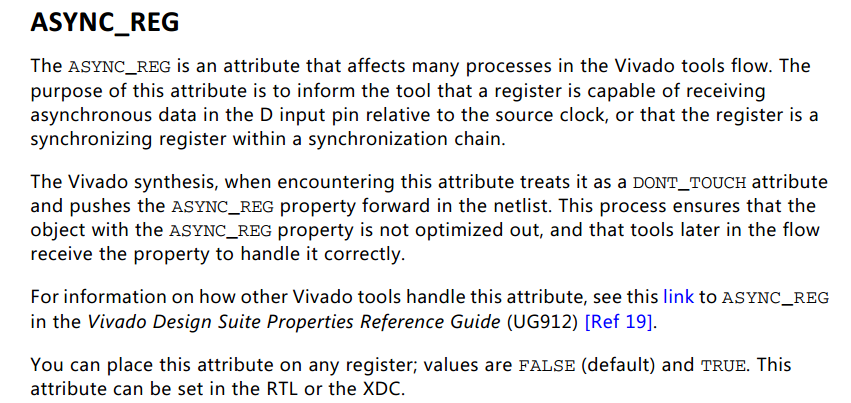

对编译特性(* ASYNC_REG = “TRUE” *)的理解

(*ASYNC_REG = "TRUE"*)命令用于声明寄存器能够接收相对于时钟源的异步数据,或者说寄存器是一个同步链路上正在同步的寄存器。这条命令可以放在任何寄存器上,除了设置它的值为TRUE外还可以设置为FALSE.

例子:(*ASYNC_REG = "TRUE"*) reg [0:0] async_rst = 0;

这样可以强制指定async_rst为异步时钟输入,防止综合器对打拍寄存器进行优化,类似DONT_TOUCH。 详情见UG901-Vivado Design Suite User Guide.pdf

module reset_sync

(input clk,

input reset_in,

output reset_out); (* ASYNC_REG = "TRUE" *) reg reset_int = 'b1;

(* ASYNC_REG = "TRUE" *) reg reset_out_tmp = 'b1; always @(posedge clk or posedge reset_in)

if(reset_in)

{reset_out_tmp,reset_int} <= 'b11;

else

{reset_out_tmp,reset_int} <= {reset_int,'b0}; assign reset_out = reset_out_tmp; endmodule // reset_sync

module cdc#(

parameter DW = ,

parameter SL =

)

(

input sys_clk ,

input sys_rst ,

input [DW-:] A_Din ,

output [DW-:] S_Dout

); (*ASYNC_REG="true"*)reg [DW-:] ccsrl_A_Din[:SL-];

reg [DW-:] ccr_A_Din ={DW{'b0}} ; always@(posedge sys_clk)

begin

if(sys_rst)

begin

ccsrl_A_Din[SL-] <= 'b0 ;

end

else

begin

ccsrl_A_Din[SL-] <= A_Din ;

end

end genvar i;

generate

for(i=;i<SL-;i=i+)

begin

always@(posedge sys_clk)

begin

if(sys_rst)

begin

ccsrl_A_Din[i] <= 'b0 ;

end

else

begin

ccsrl_A_Din[i] <= ccsrl_A_Din[i+] ;

end

end

end

endgenerate always@(posedge sys_clk)

begin

if(sys_rst)

begin

ccr_A_Din <= {DW{'b0}} ;

end

else

begin

ccr_A_Din <= ccsrl_A_Din[] ;

end

end assign S_Dout =ccr_A_Din; endmodule

相关参考:

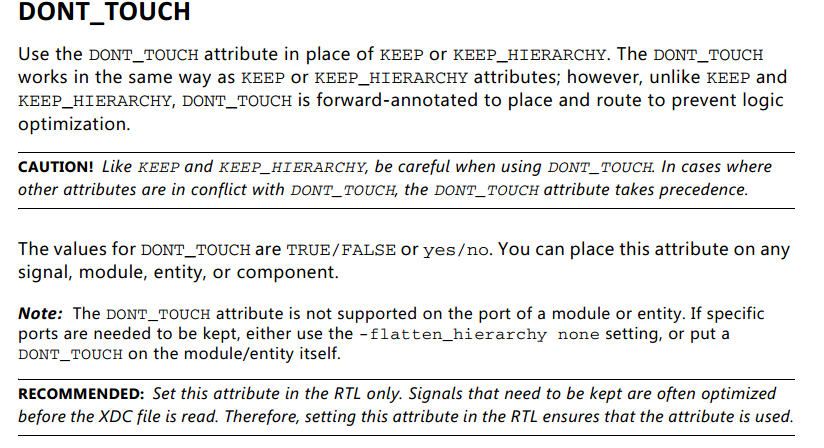

DONT_TOUCH Verilog Examples Verilog Wire Example

(* dont_touch = “yes” *) wire sig1;

assign sig1 = in1 & in2;

assign out1 = sig1 & in2; Verilog Module Example

(* DONT_TOUCH = “yes” *)

module example_dt_ver

(clk,

In1,

In2,

out1); Verilog Instance Example

(* DONT_TOUCH = “yes” *) example_dt_ver U0

(.clk(clk),

.in1(a),

.in2(b),

.out1(c));

对编译特性(* ASYNC_REG = “TRUE” *)的理解的更多相关文章

- 理解Babel是如何编译JS代码的及理解抽象语法树(AST)

Babel是如何编译JS代码的及理解抽象语法树(AST) 1. Babel的作用是? 很多浏览器目前还不支持ES6的代码,但是我们可以通过Babel将ES6的代码转译成ES5代码,让所有的浏览器都 ...

- Hibernate中inverse="true"的理解

Hibernate中inverse="true"的理解 举例如下 转自:http://lijiejava.iteye.com/blog/776587 Customer类: publ ...

- 《编译原理》-用例题理解-自顶向下语法分析及 FIRST,FOLLOW,SELECT集,LL(1)文法

<编译原理>-用例题理解-自顶向下语法分析及 FIRST,FOLLOW,SELECT集,LL(1)文法 此编译原理确定某高级程序设计语言编译原理,理论基础,学习笔记 本笔记是对教材< ...

- 《编译原理》-用例题理解-自底向上的语法分析,FIRSTVT,LASTVT集

<编译原理>-用例题理解-自底向上的语法分析,FIRSTVT,LASTVT集 上一篇:编译原理-用例题理解-自顶向下语法分析及 FIRST,FOLLOW,SELECT集,LL(1)文法 本 ...

- 【重构前端知识体系之HTML】讲讲对HTML5的一大特性——语义化的理解

[重构前端知识体系之HTML]讲讲对HTML5的一大特性--语义化的理解 引言 在讲什么是语义化之前,先看看语义化的背景. 在之前的文章中提到HTML最重要的特性,那就是标签.但是项目一大,标签多的看 ...

- 关于MVC的特性(AuthorizeAttribute)的一些理解

许多 Web 应用程序要求在用户登录之后才授予其对受限制内容的访问权限. 在某些应用程序中,即使是登录的用户,也会限制他们可以查看的内容或可以编辑的字段. 要限制对 ASP.NET MVC 视图的访问 ...

- Java面试题,Java三大特性之一——多态的理解

首先我们知道Java是一门面向对象的语言 面向对象三大特性,封装.继承.多态. 封装.继承.多态 ↓ 无论是学习路线,还是众人的口语习惯,都是按照这个这样进行排序,这是有原因的.因为封装好了才能继承, ...

- 使用Servlet3.0新特性asyncSupported=true时抛异常java.lang.IllegalStateException: Not supported

最近在运用Servlet3.0新特性:异步处理功能的时候出现以下了2个问题: 运行时会抛出以下两种异常: 一月 19, 2014 3:07:07 下午 org.apache.catalina.core ...

- java中关于while(true)的理解

java中while(true)的理解: while(true)作为无限循环,经常在不知道循环次数的时候使用,并且需要在循环内使用break才会停止,且在run()方法中基本都会写while(true ...

随机推荐

- caffe生成log日志

参考日志: http://blog.csdn.net/sunshine_in_moon/article/details/53529028 http://blog.csdn.net/lishanlu13 ...

- springboot---->获取不到yml配置文件指定的值

import org.springframework.boot.SpringApplication; import org.springframework.boot.autoconfigure.Spr ...

- 请问WCF 跟 WebService之间的相同跟异同

https://social.msdn.microsoft.com/Forums/zh-CN/c06420d1-69ba-4aa6-abe5-242e3213b68f/wcf-webservice W ...

- Python自学:第二章 合并(拼接字符串)

first_name = "ada" last_name = "lovelace" full_name = first_name + " " ...

- LeetCode--042--接雨水(java版)

给定 n 个非负整数表示每个宽度为 1 的柱子的高度图,计算按此排列的柱子,下雨之后能接多少雨水. 上面是由数组 [0,1,0,2,1,0,1,3,2,1,2,1] 表示的高度图,在这种情况下,可以接 ...

- 部署--云服务器(RubyChina上的转帖); 附加用cap部署sidekiq

https://ruby-china.org/topics/36899 附加https://ruby-china.org/topics/36899 Capistrano + Rails5.2部署 使用 ...

- Routing a Marathon Race

直接爆搜的复杂度是2^n,对于n<=40的数据过不了. 考虑优化一下. 发现如果走了一个点后,以后是不可能再经过与它相邻的点的,因为这样走显然不如直接走那个与它相邻的点. 这样每走一步就可以删掉 ...

- 『cs231n』通过代码理解gan网络&tensorflow共享变量机制_上

GAN网络架构分析 上图即为GAN的逻辑架构,其中的noise vector就是特征向量z,real images就是输入变量x,标签的标准比较简单(二分类么),real的就是tf.ones,fake ...

- python-day72--django实现的cookie/session

COOKIE 与 SESSION 一.概念cookie不属于http协议范围,由于http协议无法保持状态,但实际情况,我们却又需要“保持状态”,因此cookie就是在这样一个场景下诞生.cookie ...

- php开启redis

看下自己phpinfo的信息 php 5.5以下的都有这些文件 到这个地方下载所需要的文件:https://github.com/nicolasff/phpredis/downloads 下载解压 ...